一种具备MBIST 功能的Flash 型FPGA 配置芯片设计

2022-12-03柯志鸣党堃原单宝琛丛红艳

柯志鸣,党堃原,单宝琛,丛红艳

(中微亿芯有限公司,江苏无锡 214072)

1 引言

FPGA 是一种可编程的数字集成电路,20 世纪80年代由Xilinx 公司推出后逐渐进入大众视野[1]。FPGA从诞生到现在已蓬勃发展了30 余年,被广泛应用于消费电子、汽车电子、航空航天、武器装备等领域[2]。目前主流的FPGA 配置芯片大致可以分为3 种类型,分别为Flash 型、可擦除可编程只读存储器(EPROM)型和反熔丝型[3-7],在航空航天等对可靠性要求较严苛的领域中,EPROM 型FPGA 由于稳定性及灵活性较差,无法适应恶劣的环境[8];反熔丝FPGA 可靠性高但却只能单次编程[9],灵活性不足;而Flash 型FPGA 兼具前2者的优势,在可靠性高的同时可重复编程[10],具有开关性能优异、面积小、非易失性、低功耗等特性[11]。随着Flash 型存储器的不断发展和应用,其内部存储器密度不断增加,可能存在的故障类型不断增多。因此,具备更全面测试算法的存储器内建自测试(MBIST)就显得尤为重要。

本文设计了一款具备MBIST 功能的Flash 型FPGA 配置芯片,提出了一种更全面的测试算法,该算法可以有效提高故障覆盖率,并通过功能仿真及原型验证保证了设计的正确性。

2 整体方案设计

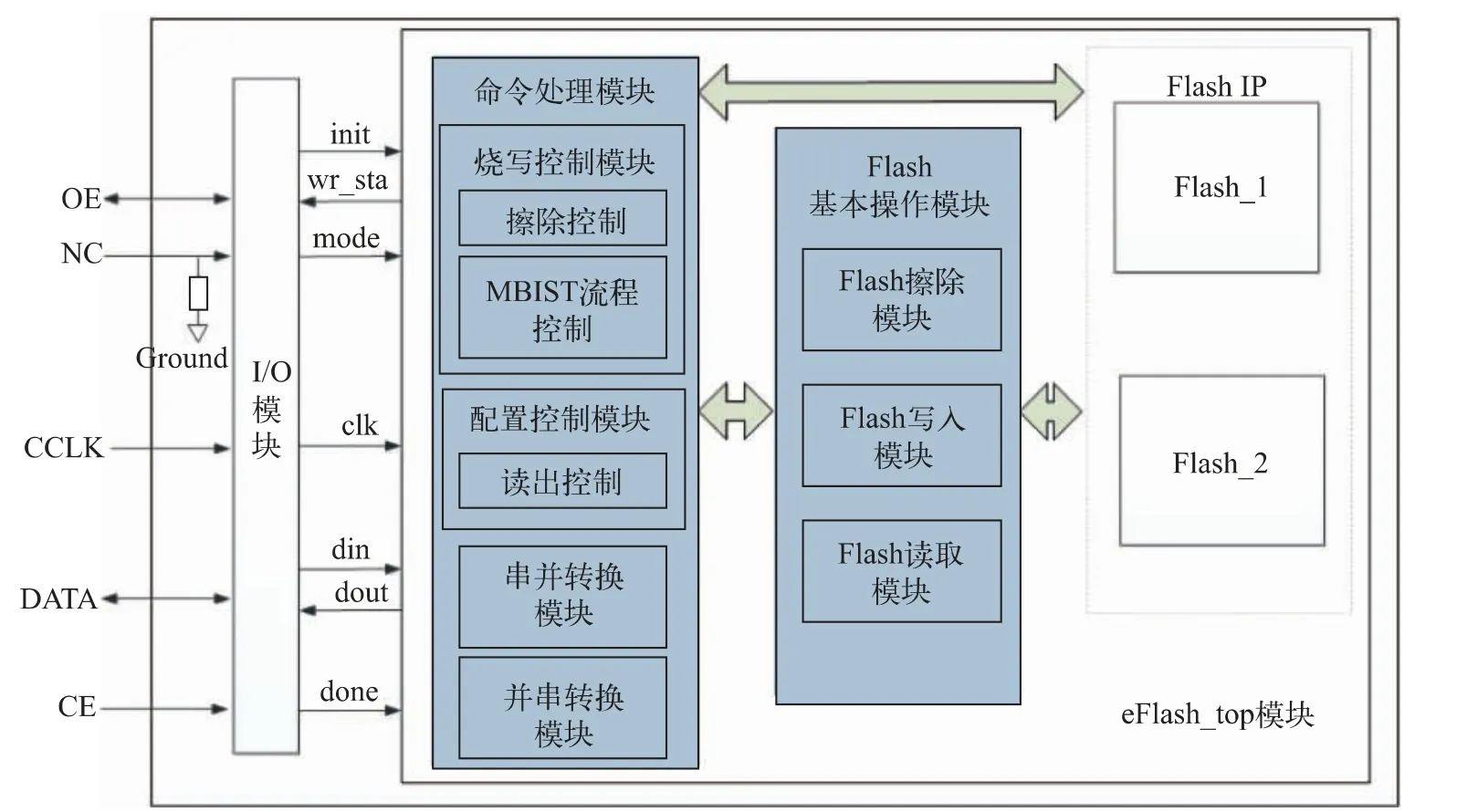

配置芯片模块如图1 所示,本文主要介绍Flash控制器eFlash_top 数字模块的功能逻辑设计,其余外围电路为模拟定制。本文主要完成RTL 代码的实现及验证,整个设计将采用拼接的方法完成。

图1 配置芯片模块

eFlash_top 模块包括命令处理模块(烧写控制模块、配置控制模块、串并转换模块、并串转换模块)、Flash 基本操作模块(读、写、擦操作模块)、Flash IP 等。I/O 模块将从芯片外输入的待配置芯片初始化完成信号OE、烧写配置模式选择信号NC、全局时钟信号CCLK、数据输入/输出(I/O)端口信号DATA 和配置完成信号CE 转化成eFlash_top 模块所需的端口信号。命令处理模块对来自于I/O 模块的命令进行处理并生成读、写、擦等基本命令。基本操作模块接收来自命令处理模块的命令,生成对Flash IP 单元的基本控制信号,完成对Flash IP 的操作。

Xilinx 公司的FPGA 芯片配置有JTAG、主串、从串、主并、从并共5 种方式的访问接口[12]。本文设计的Flash 型FPGA 配置芯片采用主串模式完成对芯片的配置,主串模式使用最少的管脚,具有灵活的I/O 电平,支持10 MHz 以下的时钟配置比特流。本设计的配置芯片应用场景空间复杂但对速度要求并不高,因此采用主串的配置方式。

3 系统设计

基于Flash 的FPGA 配置芯片系统如图2 所示。单个Flash 的容量为32 kbit,本设计搭载2 块32 kbit Flash 并进行拼接,使此配置芯片容量达到64 kbit,电路设计的最高时钟频率为25 MHz,串行配置最大速率为10MHz,设计MBIST 功能以确保Flash 功能正常。

图2 基于Flash 的FPGA 配置芯片系统

由图2 可知,eFlash_top 模块由2 个子模块组成。1)命令处理模块,即Flash_IF 模块,处理外界命令的同时向Flash 基本操作模块Flash_CTRL 输出读、写、擦命令和地址(rd_cmd、wr_cmd、er_cmd 和flash_din);实现并串转换,将来自Flash_CTRL 的64 位并行信号flash_dout 变为串行信号dout,并输出给需要配置的FPGA 芯片;实现串并转换,将来自烧写器件的串行信号din 转换为64 位并行信号flash_din,并发给Flash_CTRL 模块;处理从2 片Flash 返回的单地址写入完成信号tbit0 和tbit1,并生成相应的擦结束信号er_end 和 全 地 址 写 入 完 成 信 号 tbit_end。 2)Flash_CTRL 模块接收和处理来自命令处理模块的存储命令和地址,产生操作Flash 所需要的基本控制信号和时序,驱动2 片Flash 工作;输出读计数值信号rd_cnt 给命令处理模块用于地址的累加,读过程会持续循环读出Flash 中的值,并以flash_dout 信号输出,直到FPGA 芯片配置成功,配置完成标志信号done 拉高。

对于eFlash_top 模块,当模式选择信号mode 上拉,且done 信号拉高时,烧写流程开启。进入烧写流程后,先擦除Flash,再进入MBIST 检查,然后将输入的64 位串行数据转换为64 位的并行数据,最后将其写入Flash。当mode 信号下拉,且待配置芯片初始化完成信号init 拉高时,配置流程开启。在配置过程中,从Flash 中读出的64 位并行数据经并串转换模块转换为串行数据输出。具体操作过程中由状态机控制系统工作状态,并由控制条件控制状态的跳转,具体分为等待状态IDLE、自检测写状态MBIST_WR、自检测读状态MBIST_RD、擦除状态ERASE、写入状态WRITE、读出状态READ 6 个状态。

图3 为命令处理状态机转移图。上电完成后,系统首先进入IDLE 状态,然后在第1 次擦除结束后(er_end==1)进入MBIST 状态,包括MBIST_WR 及MBIST_RD,通过自检测计数信号pattern_cnt 和无错误标志信号no_err_sec 控制自检测过程的转态跳转,如果写入和读出的数据不相同,则说明Flash 块有错点,写入使能信号wr_sta 拉高进行报警并锁死系统。MBIST 每次读出数据后都要擦除Flash,方便下一步的操作。

图3 命令处理状态机转移

本文设计的MBIST 采用了基于March C-的一种改进测试算法,该算法共进行9 次自检测。March C-测试算法是基于目前最流行的March C 算法衍生而来,它具有更高的故障覆盖率和更少的测试步骤[13],但仍然无法做到最全面的故障覆盖。

在Flash 上电初始化完成后,所有地址数据均为全0 或者全1,相邻2 个地址的数据相同,数据之间缺少01 和10 这2 种数据状态,在这种情况下发生的故障称为耦合故障。本文提出的算法可以对该故障进行有效测试。通过深入研究存储器的故障类型,在算法中对相邻2 个单元地址位写入相反的值10、01 和0011、1100,例如4 位的地址写入16 进制的55,二进制表示为0101,然后写入16 进制的AA,二进制表示为1010,同理写入全3 和全C 对地址数据0011 和1100状态进行测试,这种测试算法可以覆盖每个相邻地址的耦合故障,结合March C-算法可以完整有效地对耦合故障、相邻单元桥接故障、数据保持故障等进行测试。

具体测试过程为:1)按照地址位的升序对每个地址进行写0 和读0 操作;2)按照地址位的升序对每个地址进行写1 和读1 操作;3)按照地址位的升序对每个地址进行写0 操作,然后按照地址位的降序进行读0 操作;4)按照地址位的降序对每个地址进行写1 和读1 操作;5)按照地址位的降序对每个地址进行写0操作,然后按照地址位的升序进行读0 操作;6)按照地址位的升序对每个地址进行写全0101 和读全0101 操作;7)按照地址位的升序对每个地址进行写全1010 和读全1010 操作;8)按照地址位的升序对每个地址进行写全0011 和读全0011 操作;9)按照地址位的升序对每个地址进行写全1100 和读全1100 操作。

在自检测准确无误后,该Flash 型配置芯片通过检测FPGA 芯片的init 信号来决定是否可以进入配置模式。本文设计的具备MBIST 功能的Flash 型FPGA配置芯片在烧写及配置工作过程中主要完成以下功能。

1)MBIST 检测。配置芯片在复位完成后,首先开始对Flash 进行MBIST 检测,向其中循环9 次写入、读出数据并进行对比,如果对比出错,将进行系统锁死并报警。

2)上位机烧写配置芯片。在MBIST 检测无误后,通过上位机将比特流以25 MHz 的时钟频率写入配置芯片,当地址为16’h1FFF 且tbit_end 信号为1,烧写完成信号wr_end 为1,代表Flash 主区烧写结束。

3)待配置FPGA 及配置芯片上电。初始化的FPGA 上电后,init 信号会自动产生0 到1 的跳变。若init 信号为高,指示FPGA 内部初始化完成,进入数据下载过程,同时等待配置芯片电路内部复位完成,之后开始正常工作;若init 信号为低,则一直检测该信号,直到变为高电平为止。当用户对初始化配置进行操作时,FPGA 可以通过将复位信号PROGRAM 拉低,并拉抵done 信号开启配置过程,然后进入存储擦除阶段。

4)FPGA 配置及循环冗余校验(CRC)检测。一旦init 被拉高,用户可以开始加载配置数据给FPGA,在加载配置数据的过程中,嵌入到配置文件中的CRC 值被取出,和FPGA 内部用来计算的CRC 值进行检查比对。如果CRC 值不符合,FPGA 将init 信号拉低,意味着有结构错误发生,配置有问题。若用户想要重新配置,则必须重新进行初始化,可以拉低PROGRAM 来复位配置逻辑,或者以重新上电复位FPGA 的方式进行重新配置。CRC 校验成功后进入FPGA 开始运行阶段(STARTUP)。

5)STARTUP。该步骤为编程下载的最后一步,完成FPGA 由配置模式到功能模式的切换。在STARTUP 期间,FPGA 正常工作所需要的全局信号置为有效,done 信号拉高,且配置时钟在该过程结束后停止输出时钟信号,代表该配置芯片配置结束。

本文设计的具备MBIST 功能的Flash 型FPGA配置芯片最高工作时钟频率为10 MHz,具备Flash 内建自检测功能,支持快速、有效地对Flash 功能及电路逻辑正确性进行检查,确保用户使用过程中该配置芯片正常工作。

4 应用验证

本文设计的基于Flash 的具备MBIST 功能的FPGA 配置芯片通过了RTL 代码的功能验证及板级原型验证测试,均满足应用需求。基于覆盖率驱动搭建并编写多个测试用例,并通过添加断言的方式验证控制Flash 的读、写、擦时序的正确性,如果断言失败,立即中断仿真。板级原型验证通过一款Xilinx FPGA芯片实现此配置芯片的功能,以确保Flash 型FPGA配置芯片产品的后续步骤正常进行,避免流片失败而导致的巨大成本损失。

4.1 功能验证

验证环境的搭建是正式开始验证工作的第一步也是最重要的一步,本设计中的验证平台是基于SystemVerilog 搭建的。利用搭建好的FPGA 配置芯片验证环境进行本方案中的RTL 代码验证,通过VCS仿真验证该芯片的逻辑功能,确保设计能实现预期的目标。

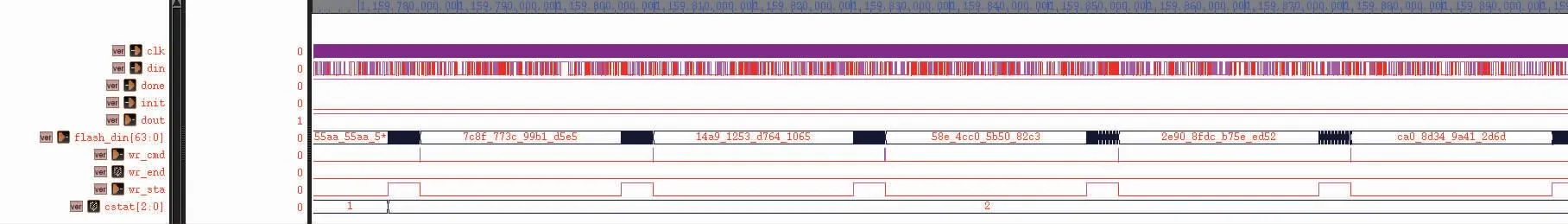

在上电过程完成后,系统进入MBIST 过程,MBIST 过程仿真验证波形如图4 所示。系统将从IDLE 状态自动跳入自检测的写、读状态,并在自检测读出完成后将读出数据与写入数据进行对比,共计进行9 次自检测过程。对比成功后则进入擦除状态,为下一次自检测写入做好准备。仿真中前8 次自检测正确且系统状态跳转无误,对比失败时则通过拉高wr_sta 信号进行报警并锁死系统,仿真中通过强制改变读出数据使第9 次自检测失败时,成功报警并锁死系统。

图4 MBIST 过程仿真验证波形

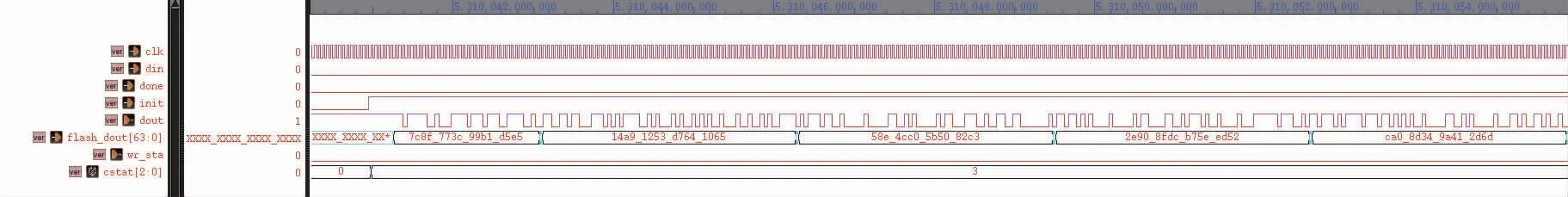

配置芯片写入Flash 随机值的仿真波形如图5 所示,在每次自检测完成后会进行擦除操作,擦除完成后当系统状态满足写入条件时,系统从自检测状态成功跳转为写入状态,将串行输入数据din 通过串转并模块转为并行数据flash_din,并正确地写入Flash。配置芯片读出的Flash 数据仿真波形如图6 所示,当满足读出条件时,系统从自检测状态成功跳转为读出状态,将读出的并行数据flash_dout 通过并转串模块转为串行数据dout,并正确地输出。由图5、6 中的flash_din 和flash_dout 数据可知,写入与读出数据一致。

图5 写入Flash 随机值的仿真波形

图6 读出的Flash 数据仿真波形

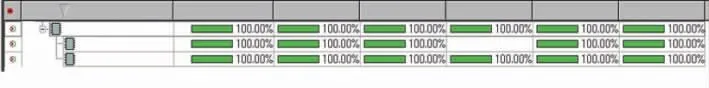

针对本方案设计的所有功能验证点,进行了行覆盖率、翻转覆盖率、条件覆盖率、分支覆盖率的收集和分析,并通过增加定向的测试用例使覆盖率达到100%,覆盖率情况如图7 所示。验证结果表明,本方案设计切实可行,满足设计需求。

图7 Flash 型FPGA 配置芯片仿真覆盖率

4.2 板级原型验证

通过建立基于FPGA 的高性能原型验证系统,可及时发现芯片设计中的错误和不足,进而缩短芯片研发周期[14]。原型验证板的整体系统结构如图8 所示,用于配置FPGA 芯片的比特文件经上位机软件发送给烧写器,经烧写器进行处理后,送至块随机存取存储器(BRAM)进行存储,配置芯片会根据FPGA 芯片的接口命令将储存在其中的比特流配置到该芯片中,该FPGA 芯片则会根据配置的比特流实现相应的功能。

图8 原型验证板的整体系统结构

原型验证板搭载2 片Xilinx 公司Virtex5 系列的SX95T 芯片,一片用于实现烧写器功能,另一片用于实现本设计配置芯片功能,配置比特流经2 片SX95T下载到FPGA 后,搭载1 块待配置FPGA 芯片作为目标配置芯片,根据其行为来验证本设计配置芯片逻辑功能的正确性,本设计的板级原型验证功能为通过按键控制LED 灯的点亮和关闭,最终通过观察LED 灯的状态判断是否配置成功。

测试结论为FPGA 芯片功能启动正常,LED 灯成功点亮,按键控制正常,证明设计的Flash 型FPGA 配置芯片功能逻辑正确,主串模式配置功能正确。

5 结论

本文提出了一种具备MBIST 功能的Flash 型FPGA 配置芯片的可行性设计方案,通过完整的数字化流程设计并验证了配置芯片的逻辑功能,该配置芯片通过设计MBIST 功能可以快速有效地检查Flash功能的正确性。方案通过了RTL 代码功能验证和板级原型验证,确保功能设计正确无误。本应用研究大大提高了Flash 型配置芯片的可靠性,缩短了出现故障时定位问题所需的时间。该配置芯片可以应用于各种复杂场景,具有广泛的应用需求。