12GSa/s12bit 超宽带数据采集系统研究

2022-12-03许家玮孔谋夫季尔优

许家玮,武 锦,孔谋夫,周 磊,季尔优

(1.电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054;2.中国科学院微电子研究所,北京 100029)

1 引言

数据采集是将自然界中存在的模拟信号通过模数转换器(ADC)转换成数字信号,再对该数字信号进行相应的接收和处理。数据采集系统作为数据采集的手段,在移动通信、图像采集、无线电等领域有重要作用[1]。随着电子信息技术的飞速发展,电信号呈现出高度复杂化的变化趋势,高频、瞬态信号的捕获、分析需要更高带宽、更高采样率的数据采集系统。提升数据采集系统前端ADC 的性能和利用并行采样方法的系统架构是提高采集系统性能的2 个有效途径。ADC 芯片是数据采集系统的核心[2],ADC 芯片的性能决定了数据采集系统的性能,但如今在ADC 的模拟电路设计中,设计出高采样率、高精度的ADC 具有很大的挑战性。因此本文从并行架构出发,基于多颗ADC 板级交织采样技术,提出了一种超宽带数据采集系统的设计方法。

本文重点介绍了采集系统中4 相位时钟模块、微变延时限模块与信号获取模块的设计。4 相位时钟模块提供一种4 路ADC 芯片交替采样的时钟方案;微变延时限模块完成对4 路子ADC 芯片的延时微调功能,用以解决时间交织技术带来的误差;信号获取模块保证输入至ADC 采样的模拟信号的质量。对数据采集系统单音信号下多频点和宽带信号的测试结果表明:在12 GSa/s 采样时钟下,单音信号时钟输入在10 MHz~2 GHz 范围内,采集系统的平均有效位数(ENOB)不低于7.2 bit,无杂散动态范围(SFDR)均在58 dB 以上;对于宽带信号具有一定的数据采集能力,在1~3 GHz 宽带信号输入下信噪比(SNR)在30 dB以上。

2 数据采集系统的基本原理

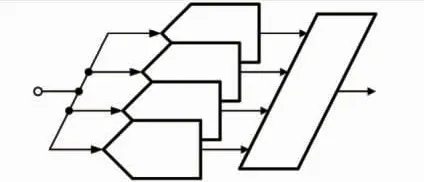

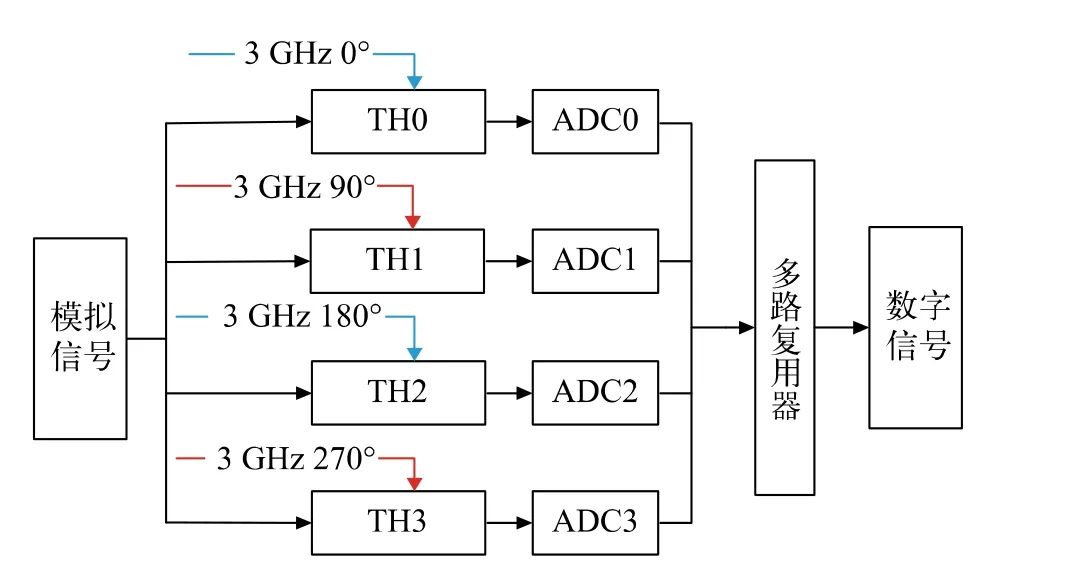

时间交织技术是一种将多颗ADC 芯片并联的手段,对多颗子ADC 芯片并行交替采样,从而使得整个系统的采样率倍增。图1 为一种4 路板级交织的数据采集系统结构图,每个ADC 结构相同且拥有相同的采样周期[3]。每个相邻ADC 的采样时钟相互错1/4 个采样周期,使这4 个ADC 能在一个时钟周期内采样4次,且每次采到的信息并不重合。最后通过逻辑电路把每个ADC 输出的数字码按照采样先后顺序整合起来,若单通道ADC 的采样率为Fs,那么最终得到采集系统整体的采样率即为4Fs,而精度仍然是子通道ADC 的精度[4]。

图1 4 路板级交织的数据采集系统

将多颗ADC 芯片集成在板卡的设计方案有利于缩小设计周期与流程,便于采集系统的开发与调试,最终完成对多颗ADC 芯片的板级交织,大大提高了采样速度,实现了超宽带数据采集系统。

3 数据采集系统关键模块设计

3.1 低抖动4 相位时钟产生模块

低抖动4 相位时钟产生模块将产生4 路相位差为90°的采样时钟,以实现对4 颗3 GSa/s 采样率、12 bit ADC 芯片的等间隔采样。由于高频下多路时钟之间的相位差关系不便于调节,在现有的时钟方案下,产生一组达到3 GSa/s 等间隔采样的时钟存在一定困难。设计交织采样时钟的方案一般有2 种:一种方案提出直接通过时钟芯片自身的延时功能,依次产生4 路相位差相同的采样时钟[5];另一种方案为在4 路子ADC前加入定制数字电路,控制数据选通,使得4 路子通道的时钟依次对ADC 进行采样[6]。对于本次设计,方案1很难找到可以提供给4 路高速、高精度ADC 采样时钟和相位调整的时钟芯片,当采样率较高时,一般时钟芯片会产生抖动和噪声,极大地影响了产生时钟的相位关系。在方案2 中,前置的数字电路会增加数据采集板卡的复杂度和不稳定性。因此本文的数据采集系统采用了一种多级锁相环(PLL)结构,用以实现低抖动的4 相位时钟模块。

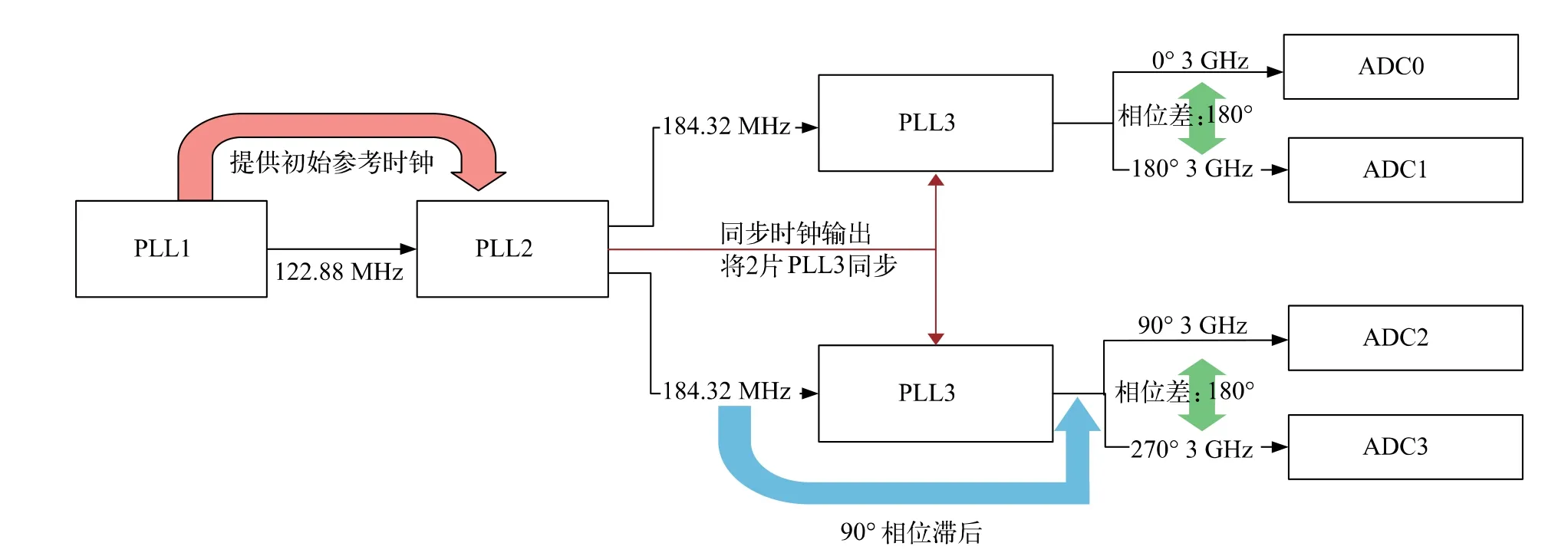

本设计采用的4 路等间隔采样时钟方案如下,选择3 级PLL 的架构来产生所需要的时钟。其中第1 级PLL 为晶振发生器,产生初始的参考时钟,无需外部时钟输入,第2 级与第3 级PLL 需要提供外部的时钟输入。3 级锁相环时钟架构如图2 所示,第1 级PLL 产生初始的122.88 MHz 时钟信号作为参考时钟给到第2级PLL,第2 级PLL 将产生的184.32 MHz 时钟给到第3 级PLL。这里第2 级PLL 的作用有2 点,首先是第3 级时钟会产生2949.12 MHz 信号作为最终的采样时钟,第3 级PLL 会对信号倍频进行放大,因此,需要将122.88 MHz 时钟转为184.32 MHz,与下一级的输出目标2949.12 MHz 为整倍数关系;同时考虑到时钟传到下一级2 颗PLL 时需要做到时钟同步,若时钟到达第3 级PLL 的时间不一致,会引起4 颗子ADC 的采样时刻严重不一致,因此需要第2 级PLL 芯片具有参考时钟功能,使2 片PLL3 的时刻同步。

图2 3 级锁相环时钟架构

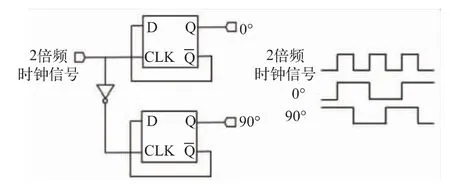

第3 级PLL 最终产生4 路交织时钟,第3 级产生的时钟信号会经过时钟分配器,产生2 路相位相差180°的时钟,这样即可为第1 路与第3 路子ADC 提供采样时钟。如何产生90°的相位差是本次设计的一个关键,相位差90°分频原理如图3 所示[1],在PLL 内部产生了一个2 倍频输出时钟,经过2 个D 触发器结构后会输出2 路相位相差90°的时钟。借助该原理,图2 中第2 颗PLL3 相对于第2 级PLL 的输出产生了90°相位的滞后。这样再经过时钟分配器就产生了差分的90°与270°信号输出,为第2 颗与第4 颗子ADC 提供采样时钟。

图3 相位差90°分频原理

3.2 微变延时限模块

理想情况下,时间交织要求4 颗ADC 均匀地交替采样,相邻通道的采样时钟间隔相同。在实际的时间交织中,采样时钟的分频与驱动电路的不对称造成了采样时刻的偏差,这也会对量化结果产生影响。实际上,4 颗ADC 并没有完全按照90°相位差交替采样,存在采样时间失配。存在的误差例如失调失配、增益失配、采样时刻偏差[7],会严重影响ADC 板卡的性能,只有把这些误差校准到一定的范围内才能获得预想的ADC 的性能。

因为采样时刻误差,时间失配误差对结果的影响最大。图4 为时间失配误差值与ENOB 的关系曲线图,此处时间失配误差值代表子ADC 芯片采样时刻间隔与理想采样间隔的误差值。可以看到,随着时间失配误差值的增加,ADC 的性能会有明显的下降。板卡需要具有对每一路时钟在极短时间内进行微调的功能,只有4 路子ADC 具有可变延时才能实现后续的时间失配校准功能。

图4 时间失配误差值与ENOB 的关系

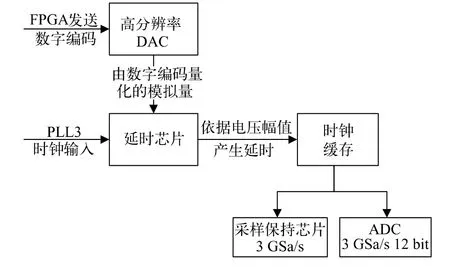

构建的可变延时限模块如图5 所示,通过数模转换器(DAC)和延时芯片连接产生延时对ADC 进行相位微调。从FPGA 向DAC 芯片发送数字信号编码,让DAC 可以产生一定范围内的可调电压(0~2.5 V)。采用一种宽带延时芯片,具有0~70 ps 的延时调整范围,产生的延时随输入电压线性变化。经过延时芯片后信号分别给到采样保持芯片和ADC。这样4 颗ADC 都具有了自身的可变延时限功能,在后续的时钟失配校准阶段可实现对4 颗ADC芯片的相位微调。

图5 可变延时限模块

3.3 输入信号提取模块

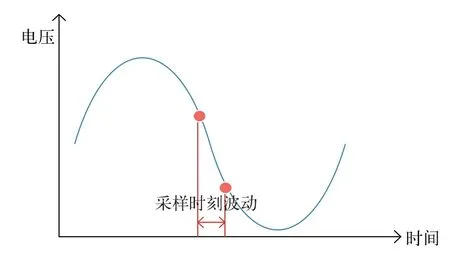

ADC 在获取输入模拟信号的过程中,采样保持电路通常处在ADC 的最前端,是系统中非常重要的一环。采样保持电路用于对输入信号的采样和保持,采样保持电路获取的信号精度决定了ADC 的最大精度和最大分辨率。ADC 会在采样时钟的控制下在采样时刻进行数据采集,而在采样时钟频率非常高的情况下,ADC 的每次采样会在采样信号比较器阈值范围内抖动,无法获取到采样时刻原本的位置。采样时刻偏差如图6 所示,每个采样时刻会在极短时间范围内有波动,而高采样率下该波动范围内采样时刻量化值会有很大的偏移。

图6 采样时刻偏差示例

此外比较器的输出节点[8]处于再生阶段时电压变化较大,这会经过寄生电容,产生对输入电压的干扰,从而产生回踢噪声。为了解决这一问题,需要在ADC前加入采样保持电路,对输入信号进行采样,尽量将真实的数据输入到ADC 中。

因此在本设计的4 颗子ADC 前加入具有高采样带宽的采样保持电路芯片TH,确保了输入至4 颗ADC 芯片中模拟信号的质量,信号提取模块结构如图7 所示。该采样保持芯片的最大精度为8 bit,考虑到本设计采集系统中4 颗ADC 芯片的实际可量化ENOB小于8 bit,该采样保持芯片量化精度满足采集系统设计要求。采样保持芯片模拟信号带宽达8 GHz,最大采样率支持4 GSa/s,符合ADC 的3 GSa/s 采样率要求。

图7 信号提取模块结构

4 电路实现和测试结果

4.1 数据采集系统功能测试

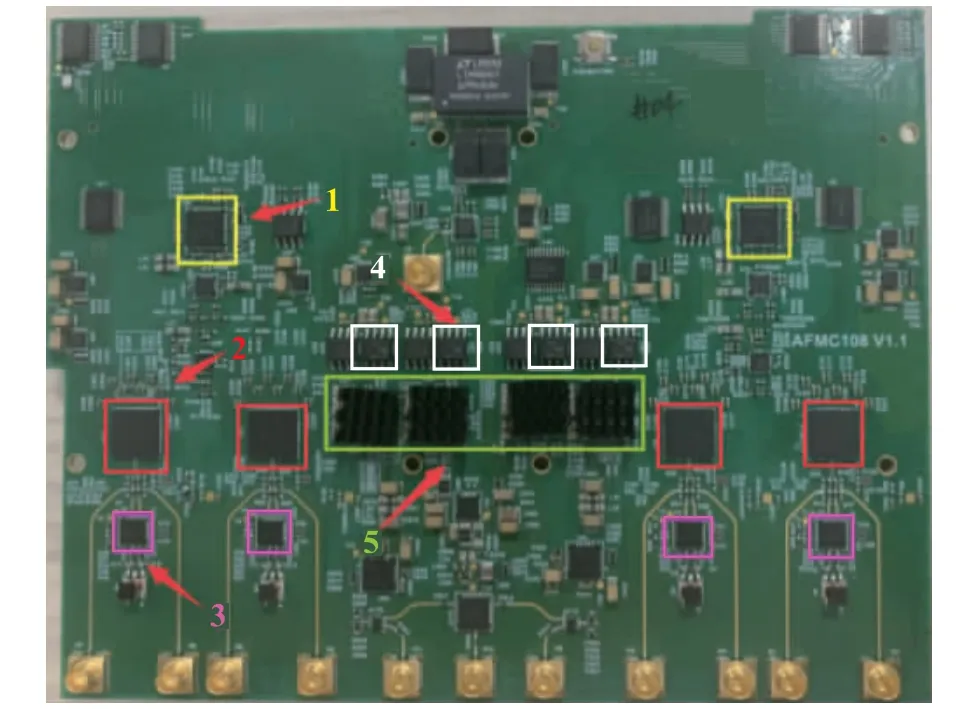

设计完成的板卡如图8 所示,序号1 处为2 颗第3 级锁相环,序号2 处为集成在板卡上的4 颗ADC 芯片,序号3 处为采样保持芯片,序号4 处为可变延时模块的4 颗DAC 芯片,序号5 处为4 颗延时芯片。

图8 板卡实物图

数据采集系统的驱动模块采用上位机-软核-AXI总线结构,该模块通过顶层C 代码对板卡上芯片的寄存器进行配置,经过AXI 总线将数据传输至各个芯片,驱动4 相位时钟模块、可变延时模块与信号获取模块。在上位机中通过网口通信完成FPGA 后台校准,将时间交织技术产生的误差校准至理想范围内。

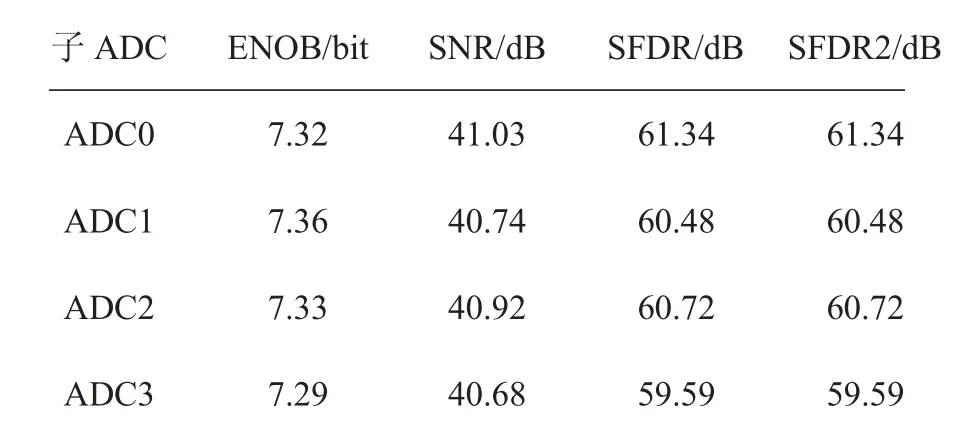

在500 MHz 下测试板卡单颗ADC 芯片性能,获取交织后采集系统性能的理想值。罗德与施瓦茨公司生产的SMM100A 信号发生器提供正弦波信号,该信号源谐波大小在-70 dB 左右,输出频率为500 MHz,幅值为12 dB。测试结果如表1 所示,当输入采集系统的时钟为500 MHz 时,每颗ADC 芯片的采样信号时钟频率为125 MHz,可以看到4 颗ADC 芯片的ENOB 不低于7.29 bit,SFDR 与除基波外最大杂散幅值(SFDR2)均不小于59 dB。采集板卡是对4 颗ADC芯片交织采样,单颗ADC 芯片的性能参数反映了数据采集系统理想条件下的最高性能。

表1 500 MHz 下板卡4 颗子ADC 性能

为了分析芯片焊接在板卡上带来的性能损失,通过单颗ADC 的评估板单独测试了每颗ADC 芯片集成在板卡前的性能水平,ADC 芯片单颗性能如表2 所示。可以看到将ADC 焊接在板卡上后会产生一些性能差异,这是由板卡上电路构造如输入损耗、亚稳态等带来的一些不可避免的性能损失。

表2 125 MHz 下4 颗子ADC 集成在板卡前的性能

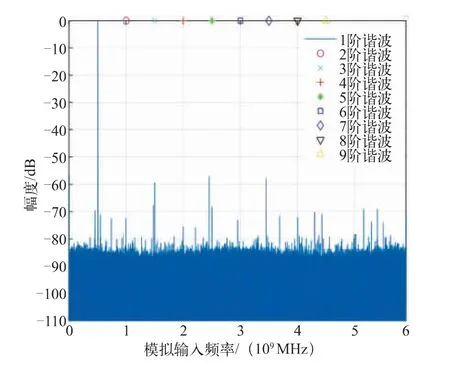

500 MHz 下的单音信号频谱如图9 所示,选取40万个点进行计算,采样率为12 GSa/s。在500 MHz 下,数据采集系统的ENOB 为7.32 bit、SFDR2 为57.92 dB、SFDR为60.13 dB、SNR 为40.77 dB。交织后采集系统的性能与单颗子ADC 性能相近,这代表板级交织效果达到理想预期,即数据采集系统的精度与单颗ADC芯片精度保持一致。

图9 500 MHz 下的单音信号频谱

4.2 各个频点下的板卡测试

在单音信号下测试多频点采集系统的性能,测试频点依次选择10 MHz、100 MHz、500 MHz、800 MHz、1 GHz、1.2 GHz、1.5 GHz、2 GHz,测试结果见表3。

表3 各个频点下数据采集系统性能

在输入信号幅值为12 dB、采样率为12 GSa/s、单音信号频率为10 MHz~2 GHz 的条件下,采集系统的ENOB 均 在7.2 bit 以 上,SFDR 均 在58 dB 以 上,SFDR2 均在54 dB 以上,在性能上与单颗ADC 芯片的性能接近,与期望中的设计目标相符合。

4.3 宽带信号测试

宽带信号测试不同于信号后处理的滤波校准,通过可变延时限功能可以将板卡本身校准到最佳性能,这样可以直接从块状存储器(BRAM)中读出校准后的数据,通过滤波校准信号后处理的方法无法满足宽带信号校准的需求,该采集系统在对中心频点校准后可用于处理宽带信号。

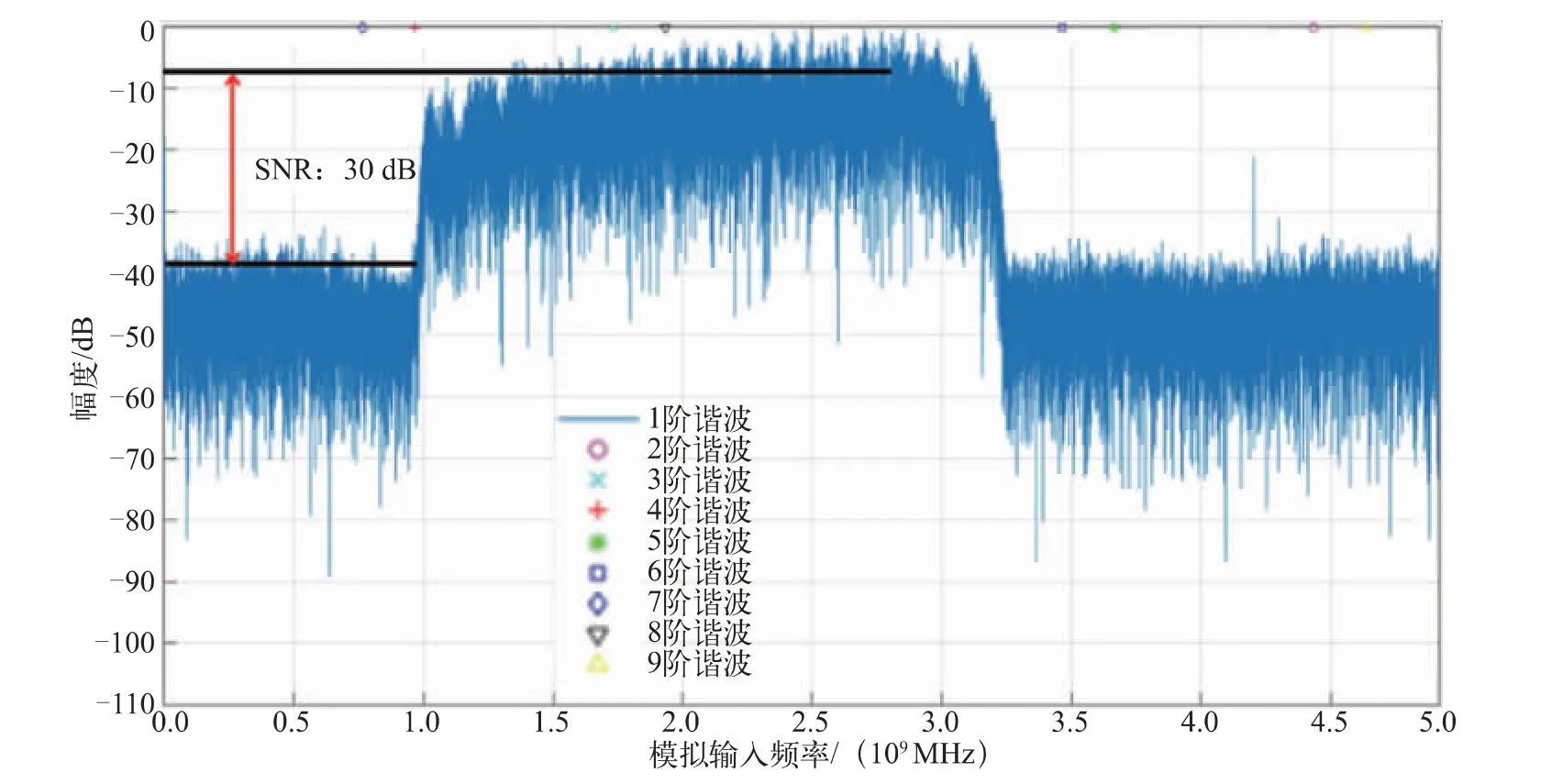

信号源选择带宽为2 GHz、起始频率为1 GHz、终止频率为3 GHz 的宽带信号,信号幅值为14 dB。选择2 GHz 作为中心频点下的校准参数,在2 GHz 校准后进行宽带信号测试。宽带信号测试结果如图10 所示,可以看出,宽带信号的SNR 为30 dB,该测试结果验证了采集系统的宽带信号采集功能。

图10 宽带信号测试结果频谱

5 结论

本研究介绍了数据采集系统的基本原理,提出了一种多颗ADC 芯片板级交织的设计方法。重点介绍了基于交织技术的采集系统中一些关键模块的设计方案,包括4 相位低抖动时钟模块、微变延时限模块与数据提取模块。在测试环节中,典型频率500 MHz 下采集系统的ENOB 为7.32 bit,SFDR2 为57.92 dB,SFDR 为60.13 dB,SNR 为40.77 dB,并对数据采集功能进行了验证。数据采集系统在10 MHz~2 GHz 单音信号下的ENOB 不低于7.2 bit,SFDR 均在58 dB 以上。宽带信号测试结果显示,信噪比为30 dB。