衍射光学元件成套制造技术研究进展

2022-08-31谢常青

谢常青

(中国科学院 微电子研究所 微电子器件与集成技术重点实验室,北京 100029)

1 引 言

衍射光学元件(Diffractive Optical Elements,DOE)是基于光波衍射理论,借助计算机辅助设计技术获取二值化的离散数据,利用微纳加工技术制造出的两个或多个台阶的相位/振幅光学元件[1]。1964年,基于当时最先进的集成电路光刻掩模制造设备(IBM 7094计算机和Calcomp绘图仪),IBM工程师Lohmann研制出世界上第一块计算机全息图[2],并且指出“平面光学的优势是用轻量化的元件取代笨重而复杂的长焦镜头”[3]。1987年,美国MIT林肯实验室Veldkamp研究组在设计传感系统中,将标准CMOS(Complementary Metal Oxide Semiconductor)工艺中的光刻掩模制造技术引入DOE制作,并提出了“二元光学”概念[4]。随后,DOE成为现代光学、计算机与集成电路技术等领域的新兴交叉学科,加快了现代光学仪器设备小型化、轻量化和集成化进程。近年来,随着集成电路装备、物联网、人工智能、大数据及增强现实等领域的快速发展,DOE在光学系统中的应用需求增长迅速,逐渐成为引领集成电路装备和光学仪器两大产业发展的核心元器件。

通过在微纳米尺度上对红外线、可见光、紫外、极紫外、软X射线乃至硬X射线光波进行波前精确调控,DOE将衍射光波集中到设定的衍射级次上,从而实现成像、色散、均匀化、准直、聚焦和任意设定波前等光学功能。DOE具有精度高、质量轻、紧凑、设计自由度大、色散特性独特和易于校准等优点,广泛应用于光通信、微光机电系统、传感测量等领域[5]以及先进光刻、同步辐射、激光聚变和X射线天文学4大光学工程[6-7]。特别地,DOE的研究进展与先进光刻机的进展相辅相成,DOE的精度依赖于先进光刻机水平,DOE的精度提高在先进光刻机的发展中一直发挥着决定性的作用[3]。DOE已经广泛应用于第四代光刻机(193 nm步进扫描投影光刻机)和第五代光刻机(极紫外步进扫描投影光刻机),包括激光带宽压缩、光束整形、离轴照明、非球面高精度检测、调焦和套刻控制、工件台位移超精密控制、计量学等重要环节[3,8-10]。193 nm光刻掩模本质上就是一种基于熔石英衬基的“零缺陷”(图形区中大于50 nm的缺陷数量为0)透射式DOE,而极紫外光刻掩模则是一种基于Mo/Si多层膜的“零缺陷”(图形区中大于20 nm的缺陷数量为0)反射式DOE[3,11]。

一方面,将标准CMOS技术引入微纳光学结构制造是衍射光学学科发展和产业升级的必然选择[12]。以高量产(High Volume Manufacturing,HVM)、高精度、高成品率为显著特征的标准CMOS工艺是集成电路生产的重要基础和基本前提,也是集成电路技术节点持续缩微的核心驱动力。2019年,数值孔径为0.33的极紫外步进扫描投影光刻机投入集成电路量产,其极限分辨率达13 nm,12英寸硅片的曝光产率达到170片/小时。基于极紫外投影光刻等上千道加工工序的高可靠集成技术,iPhone手机芯片以及人工智能处理器的性能不断提高,摩尔定律已经延续到7 nm技术节点,对应的金属半周期为14 nm,单芯片容纳的晶体管数量超过100亿[13]。预计到2033年,数值孔径为0.55或更高的极紫外步进扫描投影光刻机将投入1 nm技术节点集成电路量产,对应的金属半周期为7 nm[14]。

另一方面,标准CMOS技术并不能直接应用于定制化、小批量DOE制造,其原因是DOE产品本身结构复杂且多样,不同波段DOE对制造技术的要求各不相同,其制造模式与硅基集成电路存在巨大差异。具体来说,标准CMOS制造技术采用薄胶工艺,难以直接实现熔石英、Au等光学功能层结构转移;高端光学光刻机曝光场区面积较小,难以满足更大面积的复杂结构DOE图形生成要求,如极紫外步进扫描投影光刻机在硅片面上的最大曝光场区面积为26 mm×33 mm;复杂结构DOE的GDSII(Geometry Data Standard II的简写)数据量远高于集成电路,难以采用标准版图单元库;标准CMOS工艺不允许Au等重金属离子污染,不考虑加工面形精度要求,而且制造装备价格昂贵,其加工对象为结构图形相对简单、高度标准化、大批量(可达数十亿颗)的硅基集成电路,不适合中小批量的元器件生产。目前,极紫外步进扫描投影光刻机价格超过1.2亿欧元/台,仅为英特尔、中国台积电和三星三家公司所拥有。如何在兼容标准CMOS技术的基础上,研制复杂性、多样性的光学功能结构,集成制造出设定光学功能的DOE,一直是跨微纳尺度制造领域的核心科学问题[15]。

近年来,国内外该领域的研究工作取得了较快发展。基于HSQ光刻胶,麻省理工学院的电子束光刻孤立线线宽达到2 nm,半周期达到5 nm[16]。利用两次电子束套刻技术,劳伦斯伯克利国家实验室研制了12 nm分辨率Au X射线波带片(对应高宽比2.5∶1)[17]。俄罗斯科学院图像处理系统研究所建设了DOE专用研发线[18]。斯坦福大学报道了线宽100 nm、高宽比达140∶1的硅基衍射光学元件研制结果[19]。瑞典皇家理工学院研制了分辨率为30 nm、高宽比达30∶1的Pd/Si波带片[20]。陈宜方课题组报道了最外环宽度分别为100 nm(对应高宽比为16∶1),50 nm(对应高宽比为6∶1),30 nm(对应高宽比为7∶1)的X射线波带片,20~300 nm分辨率板的研制结果[7,21]。结合HSQ电子束光刻和低温电感耦合等离子体反应离子刻蚀技术,段辉高课题组研制了亚10 nm硅纳米管,对应周期为100 nm,高度达390 nm[22],逼近了硅纳米结构的加工极限。最近,采用HSQ光刻胶,该课题组还报道了亚5 nm单个重离子光刻技术[23]。

1995年,中国科学院微电子研究所在国内首次建立了0.8μm CMOS成套工艺技术体系,并实现了量产,这标志着我国集成电路技术水平首次进入亚微米时代[24]。在此基础上,我们将0.8 μm标准CMOS工艺成果导入DOE制造,报道了0.5μm分辨率(1000线对/mm)的X射线DOE研制结果[25]。之后,提出了混合光刻制作微纳金属光学结构技术,研制了0.1μm分辨率(5000线对/mm)的X射线光栅[26-27]。然而,DOE制造技术仍然面临三个方面的挑战:(1)单一的光刻方法难以同时满足DOE的高精度和大面积图形生成需求;(2)单一的图形转移方法难以满足DOE的多元性、复杂性光学功能结构生成需求;(3)大面积DOE的高可靠集成。针对DOE复杂图形数据处理、多元化衬基、跨微纳尺度、高深宽比(结构厚度与最小特征尺寸之比)和高保真等问题,本文在兼容标准CMOS工艺的约束条件下,对DOE成套制造技术路径进行了系统研究,总结了高精度、多功能(高保真、高深宽比、高面形、多元化衬基等)和大面积DOE成套制造技术的研究成果,并对降低成本和提高成品率的技术方案进行了讨论。

2 基本方法

高精度、多功能和大面积贯穿着DOE研究发展的整个历程。高精度指特征尺寸不断缩小,且特征尺寸精度控制越来越严格;多功能指可实现多元化衬基、高保真、高深宽比、高面形的微纳光学结构制造;大面积指DOE的光学功能结构面积大。不同应用波段和应用场景的DOE对衬基材料、特征尺寸、高宽比和台阶数的需求如表1所示。

表1 可见光到硬X射线波段DOE的微纳加工需求及应用场景Tab.1 Micro/nanofabrication requirements and application scenarios of DOE with photon energies ranging from visible to hard X-ray regions

DOE制造技术的核心是如何按照设计者的意图高精度生成光刻胶图形,进而精确地在功能层材料上高保真复制出与光刻胶图形一样的功能层结构,并实现设定的高宽比。显然,实现高性能DOE的关键取决于衬基/功能层材料的选择、制造方法的成熟度和可用的微纳加工装备之间的复杂关系。尤其是在X射线波段,所有已知材料的折射率非常接近1,消光系数非常小(与入射波长的三次方成正比)。这种迥异于可见光光学性质的相移吸收二元属性(相位伴随强度衰减而发生改变)对微纳加工提出了极其苛刻的要求[28],即自支撑/镂空薄膜上制造跨微纳尺度、高深宽比、剖面陡直、尺度控制精确的重原子序数金属光学结构,并耐受极其恶劣的辐射运行环境。我们建立了覆盖可见光到硬X射线波段的DOE成套制造技术体系,如图1所示。建立了复杂图形光刻数据处理方法,将衍射光学设计者意图转换为集成电路光刻掩模设备所识别的GDSII数据格式。提出了混合光刻图形生成方法,将GDSII数据精确传递到衬基材料表面上的光刻胶,形成功能图形。形成了加法(剥离、电镀)和减法(干法刻蚀、金属辅助化学刻蚀)两种类型的高精度图形转移基础方法,将光刻胶功能图形高保真传递到衬基表面上的功能层结构,实现对入射波前的光场调控。结合接近式光学光刻、溅射、等离子体增强化学气相沉积(Plasma Enhanced Chemical Vapor Deposition,PECVD)、原子层沉积(Atomic Layer Deposition,ALD)等传统加工技术,高可靠集成制造出DOE,最后进行检测、划片、清洗和封装。该DOE成套制造体系兼容标准CMOS工艺,加工精度、可靠性和成品率可以随着光学掩模制造技术的进步而提升。

图1 复杂结构DOE成套制造技术原理Fig.1 Schematic diagram of complete manufacturing technology for DOE with complex structures

3 跨微纳尺度复杂光学结构制造

针对可见光到硬X射线波段的DOE制造需求,需要在复杂图形光刻数据处理、先进光刻图形生成和复杂图形转移基础方法等方面开展关键技术研究,以实现功能化的跨微纳尺度复杂光学结构。

3.1 复杂图形光刻数据处理体系

复杂图形光刻数据处理是DOE从设计走向制造的第一步。单片集成电路的核心面积通常为0.1~100 mm2,图形复杂度通常不高且有一定规律,对应的GDSII数据量通常为0.1~100 Mbit。DOE的核心面积可达数万平方毫米,其GDSII数据量比常规集成电路的GDSII数据量高2~4个数量级,基于圆弧和任意函数曲线的复杂位置编码无法使用集成电路版图编辑与标准版图单元库[29]。为此,我们开发了复杂数学函数加权构成的空间位置编码微光刻数据处理体系。采用混合切割任意多边形的算法,基于集成电路商用版图软件L-Edit的宏文件技术、VC编程工具和Python软件,建立了DOE布局文件的层次结构和继承关系,自动生成由复杂数学函数加权构成的复杂空间位置编码。在兼容商用集成电路版图设计软件的前提下,高保真实现了DOE设计与制造的无缝连接。

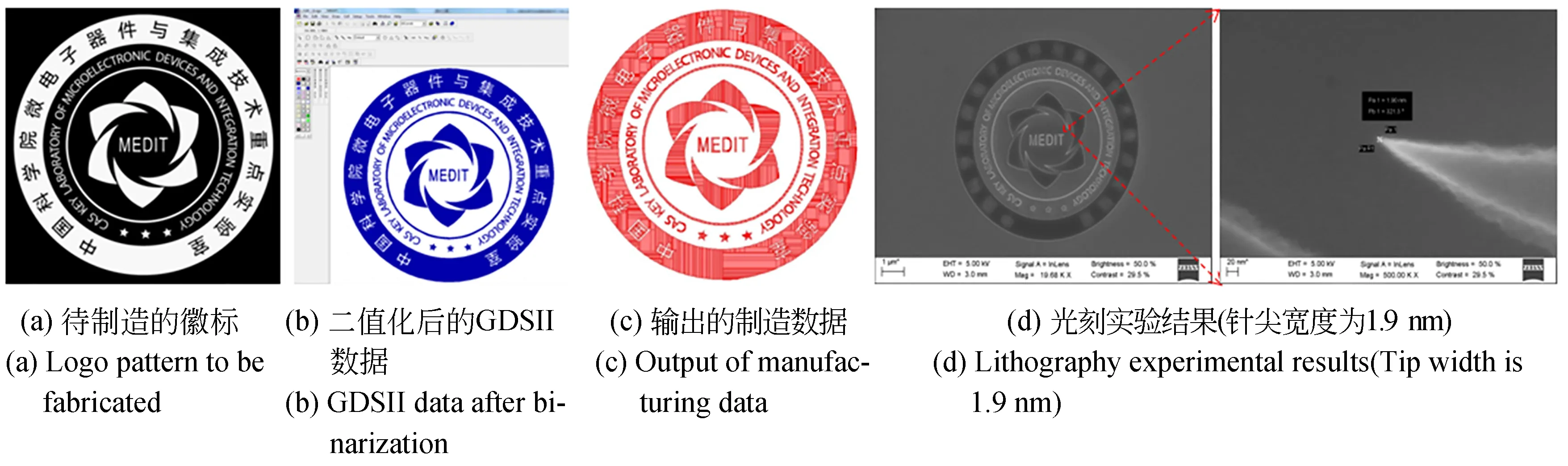

图2给出了一个典型的复杂图形微光刻数据处理例子。图2(a)是待制造的本实验室徽标。基于自制的L-Edit软件宏文件,对徽标图形进行二值化处理,自动获取了GDSII数据,如图2(b)所示。图2(c)是对图2(b)的GDSII数据进行自动处理后获取的制造数据,图2(d)是根据图2(c)提供的制造数据完成的光刻图形,徽标图形直径为8.5μm,针尖精度优于2 nm,表明GDSII数据的栅格参数设置为2 nm时,设计者意图仍然可以体现在光刻胶图形上。

图2 高精度复杂图形微光刻数据处理Fig.2 High-precision microlithography data processing for complex structures

3.2 先进光刻图形生成

图形生成是集成电路制造最核心的环节,其成本约占集成电路制造的35%,加工周期占集成电路制造周期的40%~60%。同时,图形生成还是DOE制造中技术难度最大、成本最高的环节。我们将集成电路光刻掩模制造技术拓展应用于复杂结构DOE图形生成,提出了基于高斯束矢量扫描/可变矩形束拼接电子束光刻、激光直写和i线/248 nm分步投影光刻的混合光刻方法。其基本原理是根据不同的图形特征尺寸,采用不同类型的光刻技术,有效兼顾了精度与速度。首先,利用高斯束矢量扫描电子束光刻生成纳米图形,降低邻近效应影响,并同步生成套刻标记图形,以便于后续光刻套准识别。接着,利用可变矩形束拼接电子束光刻或者248 nm分步投影光刻机生成深亚微米光刻图形。最后,利用激光直写或i线分步投影光刻生成微米/亚微米光刻图形。高斯束矢量扫描电子束光刻具有最高的光刻分辨率,但是效率极低(每平方毫米约需1~8小时),仅适用于100 nm以下复杂DOE图形的生成。可变矩形束拼接电子束光刻是当前45 nm节点(对应特征尺寸约为200 nm)及以下光刻掩模图形生成的唯一工具,效率较高(88 mm×88 mm面积约需6小时),为此用于小批量深亚微米复杂DOE图形生成。对于大批量深亚微米复杂DOE图形生成,则采用248 nm步进投影光刻机(约80片/小时)。图3(a)给出了极限分辨率光刻实验结果。通过采用冷显影(2°C)的方法,光刻极限分辨率达到了6 nm,对应的光刻胶厚度为70 nm。图3(b)是复杂图形的设计图纸,图3(c)和图3(d)分别给出了平面和倾斜角度的扫描电镜测试结果。

图3 亚10 nm分辨率和复杂图形光刻实验结果Fig.3 Experimental results of sub-10 nm lithography and generation of complex pattern

3.3 复杂图形转移基础方法

图形转移的质量(功能层结构的保真度、高宽比等)直接影响DOE的衍射效率和信噪比。硅集成电路加工技术采用感应耦合等离子刻蚀硅、金属和介质,采用大马士革镶嵌工艺进行铜布线,III-V族化合物半导体集成电路加工技术则采用蒸发剥离制造源极、漏极和栅极。基于这一思路,针对复杂DOE不同高宽比和高保真图形转移的需求,我们发展了加法和减法两种类型,4种图形转移基础技术,如图4所示。加法技术包括蒸发剥离和金属电镀图形转移基础方法。前者用于可见光到极紫外波段的振幅型DOE制造。在带底切的光刻胶图形上蒸发所需的金属,用湿法同时去除残余光刻胶及其表面上的金属,在石英衬基上形成所需的金属结构。该方法能制作的金属厚度一般不超过光刻胶厚度的一半,可制造小高宽比金属结构,如图4(a)所示。后者用于制造透射型X射线波段的DOE。在自支撑衬基上光刻出大高宽比光刻胶图形,采用基于脉冲电源的亚硫酸盐纳米镀金技术,降低电镀液的表面张力,实现侧壁形貌与光刻胶模板具有高度一致性的图形转移,制作出来的金属结构和光刻胶模板具有相同的高度,如图4(b)所示。减法技术包括多层干法刻蚀和低温金属辅助化学刻蚀图形转移基础方法。前者用于可见光到深紫外波段透射型DOE的制造,也可用于极紫外到硬X射线波段反射型DOE的制造。采用多层套刻、等离子体刻蚀方法形成多台阶结构,以提高DOE的衍射效率,如图4(c)所示。后者主要用于硬X射线波段透射型DOE的制造,如图4(d)所示。高宽比大于100∶1的纳米光学结构是DOE应用于硬X射线波段的主要技术瓶颈,挑战微纳加工技术的极限。我们提出了侧墙转移金属辅助化学刻蚀方法。首先,利用薄胶光刻和离子束刻蚀在硅基表面制作Ti/Au金属结构,基于提出的低温金属辅助化学刻蚀方法加工竖直硅纳米结构[30-31],在硅纳米结构表面ALD一层氧化物(Al2O3,TiO2等),然后利用无掩蔽等离子刻蚀法去除硅纳米结构表面上的氧化物和硅纳米结构,并从硅衬基背面挖窗口和湿法去硅,从而在自支撑硅膜上获取高宽比远高于传统干法刻蚀的侧墙氧化物纳米结构,用于形成硬X射线波段透射型DOE功能层结构。

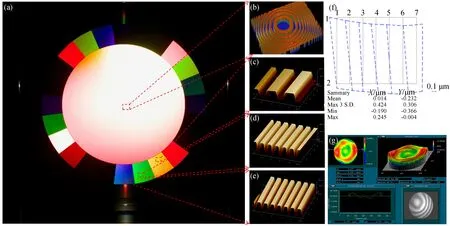

图4最后一行给出了蒸发剥离、金属电镀、多层干法刻蚀和侧墙转移金属辅助化学刻蚀方法的实验结果。其中,蒸发剥离的L型金属结构分辨率达30 nm,高宽比为1∶1,如图4(a)所示。Au结构线宽为25 nm,厚度为300 nm,对应高宽比为12∶1,如图4(b)所示。多层干法刻蚀完成8台阶可见光DOE的制造,其三维光学表面轮廓如图4(c)所示。侧墙转移金属辅助化学刻蚀法的实验结果如图4(d)所示,Al2O3纳米管线宽为30 nm,厚度为15μm,对应高宽比达500∶1。

图4 加法(a和b)和减法(c和d)图形转移方法示意图Fig.4 Schematic illustration of pattern transfer by additive(a,b)and subtractive(c,d)manufacturing techniques

3.4 不同波段微纳光学结构制造方案

不同应用波段和应用场景的DOE制造通常需要采用不同的技术方案,具体如下:(1)可见光、紫外和深紫外波段DOE的分辨率要求相对较低,部分应用场景需要采用多台阶结构,因此,采用可变矩形束拼接电子束光刻、激光直写或者i线/248 nm分步投影光刻的混合光刻方法,以及剥离或者干法刻蚀的图形转移方法;(2)极紫外和软X射线波段DOE的分辨率要求极高,采用高斯束矢量扫描电子束光刻和激光直写的混合光刻方法,前者采用干法刻蚀的图形转移方法,减少干法刻蚀损伤和缺陷,后者采用电镀或者干法刻蚀的图形转移方法;(3)硬X射线波段DOE的分辨率通常不超过50 nm,采用高斯束矢量扫描/可变矩形束拼接电子束光刻和激光直写的混合光刻方法,以及干法刻蚀或者金属辅助化学刻蚀的图形转移方法。

自主研发的复杂图形光刻数据处理体系兼容集成电路商用版图软件,将DOE设计指标高保真转换成可制造的GDSII数据。基于电子束与光子束的混合光刻方法可以有效解决单一光刻技术难以同时兼顾高精度和大面积图形生成的技术难题。基于加法和减法技术的4种图形转移基础方法,包括剥离、电镀、干法刻蚀和金属辅助化学刻蚀,可以满足多元性、复杂性光学功能结构的生成需求。

4 大面积衍射光学元件集成

大面积DOE可以提高光通量,实现大视场光学系统的精细光场调控,是衍射光学领域一个重要的发展方向。我们将复杂图形光刻数据处理、混合光刻和高精度图形转移基础方法等核心制造模块和接近式光学光刻、PECVD等常规加工技术相结合,综合考虑了衬基材料和厚度、机械传输手、光刻胶处理(前后烘温度、时间、均匀性、制冷方式和时间、显影液类型和浓度、显影时间和温度等)、化学清洗和腐蚀等加工敏感参数对图形定位精度、面形精度和表面粗糙度等性能参数的影响,建立了相应的工艺控制规范,集成了系列大面积DOE,覆盖可见光到硬X射线波段。

4.1 深紫外波段衍射光学元件集成

图5(a)是集成研制的直径为140 mm的深紫外波段透射式位相型DOE,采用标准的6025光刻掩模熔石英衬基。图5(b)是其中心位置光学结构的三维轮廓,图5(c)~5(e)是采用原子力显微镜测试的边缘位置光学结构,最外环宽度达到300 nm。我们还采用集成电路光刻掩模定位测量系统(LMS IPRO2)对大面积DOE的光学结构位置误差进行了定位表征,结果如图5(f)所示,虚线表示的是设计位置,实线表示的是测量位置。在图形内选择150个点进行测量,X方向平均定位误差为14 nm,Y方向平均定位误差为232 nm,均在光刻掩模标准允许误差范围内,误差来源为长时间、长行程的工件台拼接和光刻胶处理、刻蚀过程等高温工艺引起的误差。图5(g)是采用ZYGO干涉仪获取的透射式面形测试结果,PV值为0.287λ,优于标准193 nm光刻掩模的面形PV值(约1.5λ)。深紫外波段DOE已经应用于我国首台90/28 nm光学光刻机的镜头测试。

图5 六英寸深紫外波段透射式位相型DOE。(a)实物图;(b)中心位置光学结构;(c~e)边缘位置光学结构;(f)定位精度;(g)面形精度Fig.5 Six inch phase-type DUV transmission DOE.(a)Fabricated DOE;(b)Optical structures at central location;(c-e)Optical structures at various edge locations;(f)Position accuracy;(g)Surface flatness

4.2 极紫外波段衍射光学元件集成

图6(a)是集成研制的142 mm×142 mm极紫外波段反射式振幅型DOE,采用具有极低热膨胀系数的6025 Mo/Si多层膜衬基[32]。在多层膜衬基表面采用离子束方法淀积了100 nm厚的Cr薄膜后,在20.1万倍的扫描电镜下观测了Cr薄膜表面形貌,发现Cr薄膜颗粒形貌呈柱状分布,如图6(b)所示,这不同于传统的细丝状分布。随机选取3个位置采用原子力显微镜测试表面粗糙度,Cr薄膜均方根粗糙度均小于1 nm,如图6(c)所示。图6(d)是在国家同步辐射实验室计量线站获取的多层膜反射率测试结果,13.5 nm波长处的反射率达到68.6%,接近69.5%的理论极限[33]。图6(e)~6(f)是Cr光学结构的平面和剖面扫描电镜测试结果。极紫外反射式光栅设计线宽为88 nm,设计周期为176 nm。实测线宽为87.25 nm,实测周期为174.5 nm。极紫外波段DOE已经应用于我国首台32/22 nm节点EUV投影光刻原型装置和空间探测EUV地面定标系统。

图6 六英寸极紫外波段反射式振幅型DOE。(a)实物图;(b)Cr薄膜表面形貌扫描电镜测试;(c)三个位置的Cr薄膜表面粗糙度;(d)多层膜反射率;(e~f)平面及剖面扫描电镜测试Fig.6 Six inch amplitude-type EUV reflective DOE.(a)Fabricated DOE;(b)Surface SEM image of Cr film;(c)AFM characterization exhibiting surface roughness at three different locations;(d)Reflectivity verus wavelength plot for Mo/Simultilayer;(e-f)Surface and cross-sectional SEM images of the fabricated DOE

4.3 软X射线波段衍射光学元件集成

图7是集成研制的直径为70 mm的软X射线波段透射式DOE。集成电路商用PECVD设备的淀积温度为400℃,导致生长的无定形SiC自支撑薄膜口径、热学、机械和抗辐射等性能不满足恶劣辐射环境的应用需求。我们自制了双腔立式、高真空1 000℃非商用PECVD设备[34],研究了淀积参数和退火度对SiC(100)多晶薄膜微结构、机械和光学性能的作用规律。在自支撑SiC衬基研制的基础上,采用Au电镀的图形转移方法集成制造了软X射线波段透射式DOE,如图7(a)所示。图7(b)~7(c)是Au光学结构的扫描电镜测试结果,其中的厚金加强筋结构采用接近式光学套刻和电镀的方法制备,以防止Au光学结构倒塌,从而实现完全镂空。软X射线波段DOE已经应用于我国“神光”系列激光聚变等离子体诊断系统。

图7 Au电镀的图像转移法集成制造的4英寸软X射线波段透射式DOEFig.7 Four inch soft X-ray transmission DOE fabricated by free-standing gold transmission grating supported by Au grid structures

4.4 硬X射线波段衍射光学元件集成

图8(a)是集成研制的硬X射线波段高面形反射式DOE。图8(b)~8(c)是Au光学结构的扫描电镜测试结果。图8(d)是采用原子力显微镜随机测试的Au光学结构和衬基表面粗糙度,均方根粗糙度分别1.31 nm和1.40 nm。图8(e)是面形测试结果,3个光栅区域的面形精度PV值分别为0.06λ,0.07λ和0.03λ。该面形结果远优于深紫外波段DOE,主要原因在于精抛光过程中硅衬基材料的光滑度和加工面形控制难度比熔融石英/极低膨胀玻璃基板小。硬X射线波段DOE已经应用于我国同步辐射X射线光学元件标定平台上。

图8 硬X射线波段反射式DOE。(a)实物图;(b~c)平面扫描电镜测试结果;(d)原子力表征结果;(e)面形Fig.8 Hard X-ray reflective DOE.(a)the fabricated DOE;(b-c)SEM images of gold strip gratings;(d)AFM characterization;(e)Surface flatness of the fabricated DOE

5 总结与展望

针对DOE高精度、多功能和大面积的发展趋势,本课题组建立复杂结构DOE成套制造技术,实现入射电磁波的精确操控,不仅是当前衍射光学研究发展的前沿和热点,也是DOE产业发展的主要瓶颈。

近年来,在兼容标准CMOS工艺的约束条件下,我们自主研发了复杂图形光刻数据处理体系,实现了DOE设计指标到可制造的GDSII数据的高保真转换。发展了基于电子束与光子束的混合光刻方法,同时兼顾了高精度和大面积的复杂图形生成。进一步提出了剥离、电镀、干法刻蚀和金属辅助化学刻蚀4种图形转移基础方法,可以满足可见光到硬X射线DOE的光学功能结构生成需求。基于上述关键制造技术,在熔石英、多层膜、SiC自支撑薄膜、高面形硅片等衬基上大面积集成了系列DOE,覆盖可见光到硬X射线波段,应用于先进光刻、同步辐射、激光聚变和天文观测等多项国家重大工程[35]及超过1 000家国内外高等院校、科研院所和高新企业。该成套制造技术还拓展应用于超表面、MEMS等器件[36-37]。然而,国内在DOE成套制造量产技术方面与国外仍然具有很大差距。德国卡尔蔡司公司生产的深紫外和极紫外波段DOE已经批量应用于193 nm/EUV步进扫描投影光刻机。麻省理工学院空间纳米技术实验室生产的100 nm分辨率硬X射线光栅数量已经达到数万块,仅Lynx光栅光谱仪携带的大面积硬X射线光栅数量就达到2 000块[38]。

种类繁多、功能多样化及应用范围广泛的DOE制造仍然面临着提高性能、降低成本和提高成品率等挑战。一方面,设计工艺协同优化(Design Technology Co-optimization,DTCO)是当前标准CMOS工艺的前沿方向,未来需要将DTCO方法引入DOE制造。在DOE制造层面,从衬基材料、图形生成和结构转移等角度建立可重复使用的制造模块,提供限定设计规则和坏点图形库。在DOE设计层面,建立包括衍射效率、分辨率、面积和成本等因素在内的评价函数,对输入面进行相位恢复,并输出可制造的二值化离散化数据,实现设计与制造的协同优化。另一方面,近年来,多种新型纳米加工方法被提出,但是,如何从兼容标准CMOS工艺角度实现纳米级图形生成、纵向与横向结构转移的精确控制,突破DOE集成制造和检测瓶颈还需要进一步研究,尤其是大场区、高分辨、低成本的HVM光刻技术、检测方法及装备。这些技术问题的解决,不仅能够提高DOE的整体性能和降低成本,也会为超表面、微纳光电子、MEMS/NEMS等器件的HVM生产提供支持。

致 谢:Mo/Si多层膜衬基由中国科学院长春光学精密机械与物理研究所金春水提供,多层膜反射率测试得到了国家同步辐射实验室计量线站周洪军和霍同林的帮助,面形测试得到了北京理工大学刘克的帮助,先进光刻机DOE设计及应用得到了长春国科精密光学技术有限公司周连生等人的帮助,X射线DOE设计及应用得到了深圳技术大学曹磊峰、中物院激光聚变中心魏来等人的帮助。DOE的集成制造由中国科学院微电子器件与集成技术重点实验室朱效立、李海亮、华一磊、牛洁斌等30多名员工和研究生共同完成。