基于自适应陷波器的干扰信号滤除及FPGA实现

2022-05-14邓文舫郭来功

邓文舫,郭来功

(安徽理工大学 电气与信息工程学院,安徽 淮南 232001)

在采集的各种监测信号时,传感器在进行信号提取以及信号的传输过程中,往往会受到一些信号干扰或者传输设备自身固有的干扰,从而影响信号传输的质量。窄带强干扰是最常见的干扰信号之一,由于我国交流电的频率为50Hz,因此在信号采集过程中,容易受到这种工频信号的干扰[1]。一般当干扰带宽小于传输信号的1%,且强度大足够时,极可能会使有用信号完全失真。为抑制信号受到的窄带干扰,同时为追求实际应用价值,国内外许多学者都相继提出了大量针对窄带强干扰信号的滤除算法。包括采用模拟滤波器搭建相应的滤波电路来实现信号的降噪,以及根据实际信号的幅度大小进行自适应噪声滤波。但这些算法由于存在计算量大,收敛速度慢等原因,不利于硬件的实现。在FPGA硬件实现的数字滤波器能很好解决并行性和速度问题,且由于FPGA的可编程特性,可以节省资源实现其他功能[2],即可实现更快地运行速度和更强地可扩展性[3-5]。

设计了以LMS算法作为自适应算法的自适应频率陷波器,可以针对已知频率但不知幅度以及相位的干扰信号进行滤除。并在Altera公司的Cyclone系列芯片上成功实现了这一算法,将本例待处理信号中叠加的两个强窄带干扰信号滤除,同时为了便于硬件实现,还与Matlab进行了联合仿真,首先使用产生一段有用信号,再将这个有用信号与多个窄带干扰信号进行叠加,作为待处理信号即整个陷波滤波处理系统的输入信号,对待处理信号使用Matlab进行陷波算法仿真,再将这个待处理信号加载到FPGA上进行算法的硬件实现。

1 自适应陷波器

陷波系统基本结构如图1所示,由自适应算法和滤波器两部分组成[6]。为考虑实际运用需求和滤除效果,采用最小均方误差算法(LMS)作为自适应算法和有限脉冲相应滤波结构(FIR)的滤波结构在保证有用信号不被损失的条件下,对两个频率的干扰信号进行滤除。信号x(t)是有用信号s(t)叠加窄带干扰后的待处理信号,将其作为输入信号从系统的期望信号端输入。干扰信号的幅度大小是未知的,频率是已知的。为了实现对干扰信号的估计和复现,需要引入参考信号r(t),并调整权值w,以合成与干扰信号相同信号,即得出陷波器的估计值y(t)。信号y(t)与待处理信号的差值e(t)就是所需要得到的有用信号,也是LMS算法的误差信号。

其中,对权值w的调整过程需要采用LMS算法,陷波结构对干扰信号的估计和原干扰信号之间差值不断减小,并快速收敛至差值为0的程度。对于某一频率的信号干扰,需要添加该频率的正弦和余弦两路信号进行加权运算和叠加。因此在评价这个陷波系统性能的重要指标即为收敛的速度、有用信号和待处理信号之间的差值与实际误差值的大小对比。所以在最后仿真结束时,要使用Matlab计算信号处理前后的干性比大小。

图1 自适应陷波器结构

1.1 滤波结构

自适应陷波器作为一种滤波器,一般采用的是有限脉冲相应(FIR)滤波器结构,其前向路径更受青睐,它可以细分为直接型、转置型、网格型和脉动阵列型[7]。

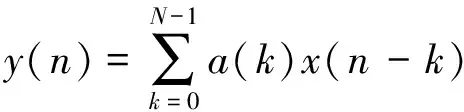

其滤波器结构的方程可用公式(1)表示。

(1)

公式(1)中的各项参数代表着滤波器的基本结构,x(n)为输入序列,y(n)为输出序列,a(k)为滤波器系数,N是滤波器的阶数。为了更方便地对公式(1)中的离散信号进行处理,需要对公式(1)进行Z变换,整理可得FIR滤波器的传递函数如公式(2)所示。

(2)

公式(2)是经过Z变换后得到的FIR滤波器的传递函数关系式,H(z)表示输入和输出间的传递关系,X(z)和Y(z)分别表示输入、输出序列的Z变换结果,a(k)z-k为系数a(k)的Z变换结果。设计的基于FIR基本结构的参数可调的数字滤波器,在实现对输入数据的处理过程中,当遇到数据的某一特性是未知量时可进行跟踪,对公式(2)中滤波器结构的各参数进行调节,使之能够实现相应的滤波功能,同时具有一定的自适应特性。

1.2 LMS算法

最小均方误差(LMS)算法,最早由wirdow和Hoff提出[8]。是基于最小均方误差准则,算法简单实用,已成为一种广泛使用的自适应滤波算法[9]。它改进了均方误差梯度的估值计算方法,同时取用每一时刻误差的平方e2(n)来进行估计。LMS算法通过计算参考信号与输出信号的差值来自动选定自适应改进滤波器的权值系数,使下一次迭代输出的结果更加精确[10]。

LMS算法可以用一组递推公式表示。

y(n)=WH(n)X(n)

(3)

e(n)=d(n)-y(n)

(4)

W(n+1)=W(n)+2μX(n)e2(n)

(5)

可以分为以下几个步骤:首先对LMS进行步长的确定,需要满足收敛条件,根据相应的环境选择适应的步长因子μ;再初始化权值ω(0)=0,进行LMS迭代计算时还要将对这一部分进行赋值并更新。LMS算法完全由加减法和乘法组成,这便于在FPGA上对这个算法进行的硬件实现。

2 FPGA算法实现

FPGA作为一种可编程的高效数字信号处理器件,适合在系统对算法的实时性以及大规模的数值处理的场景中使用。数据处理选用的是ALTERA公司的CycloneI VE系列芯片。

系统流程图如图2所示,其中虚线框内为陷波算法部分。设计的FPGA程序框图包含了三个模块分别为陷波器顶层模块、时序控制模块、DDS数据产生成模块,关键的陷波算法实现部分,采用了6级权值更新。输入的信号为待处理信号,对这一信号进行AD数模转换后将所得到的数据储存到实例化后命名为ROM1的IP核中,再与加权过后的参考信号进行差值运算将结果输出。

图2 系统流程图

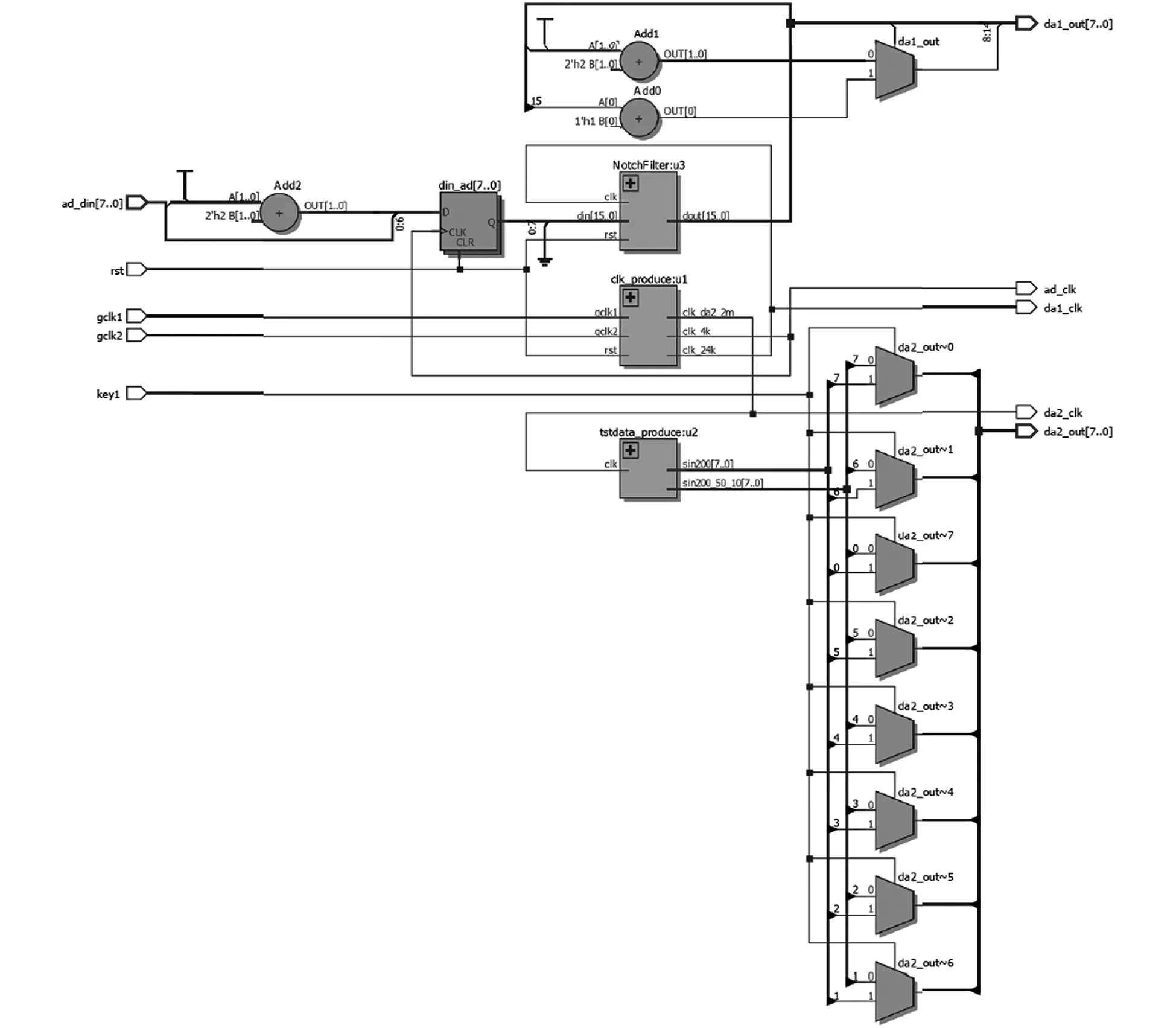

建立工程文件并进行Verilog语言的硬件编程和综合分析后得到如图3所示的RTL硬件原理图。从图3中可以看出是需要使用的各逻辑器件的种类和数量,同时完成了它们之间的逻辑连线。

图3 RTL结构示意图

2.1 信号储存模块

数据生成模块中的模块框图如图4所示,采用的AD、DA通道均为8bit,AD通道的采样频率设定为200Hz,而陷波器的输入数据为16bit,因此还需对AD通道的输入数据进行补零操作将位宽扩展到16bit。

产生长度为4096点的待处理信号采集后,将信号储存为mif文件加载到ROM核中,数据生成模块实例化ROM核以产生待处理信号,同时使用同样的方法将50Hz和100Hz的参考信号加载到QuartusII13.1的ROM核中,然后在顶层模块中引用该信号发生模块,并将待处理信号加载到陷波器的输入端。

图4 数据生成模块框图

2.2 时序生成模块

进行FPGA的硬件实现过程中首先需要将输入信号储存在rom核中,并实例化rom核后的数字式频率合成器模块产生输入信号。所以我们需要对每个过程设定相应的周期,以产生不同需要的采样频率。产生不同时钟的方式一般有两种,一种是采用IP核对FPGA的时钟信号进行任意分频和倍频以得到所需的时钟频率,另一种是直接使用Verilog语言进行设计来描述分频器。这两种方法都可以得到所需的时钟频率,并进行使用,但使用IP核的方法可以有效提高FPGA的开发效率,同时减少设计以及调试的时间。

为了便于使用简化步骤通过分频时序生成模块产生的驱动时钟,调用了QuartusII13.1中的ALTPLL核分别产生频率为2.048MHz的时钟信号、24kHz的待处理时钟信号,以及4kHz的采样时钟信号。并对整个系统的时序进行控制,保证其正常运行。

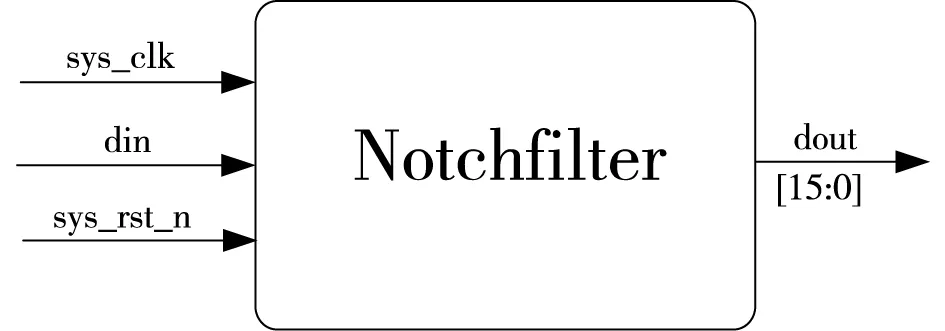

2.3 陷波算法处理模块

频率陷波处理的模块框图如图5所示。输入端为设置的系统时钟以及复位信号和16bit的输入数据,输出端为经过滤波处理后得到的16bit输出信号。由于LMS算法的六个步骤在FPGA实现过程中,共需要占用6个时钟周期,所以FPGA的处理频率24kHz为数据抽样频率4kHz的6倍。陷波运算采用的算法即前文中对LMS自适应算法,在硬件的实现过程中,需要使用Verilog语言进行相应的编程以实现这一算法,然后将这一模块实例化放入工程的顶层文件中。

图5 陷波器结构框图

3 仿真分析

为展现前文所述的陷波算法性能及其硬件实现效果,使用Matlab和FPGA进行联合仿真实验,使用Matalb产生一段达到需求的信号作为原始有用信号用以表示监测信号,然后将这一信号与模拟的干扰信号相互叠加产生待处理信号。最后对待处理信号分别进行软件处理和硬件实现以及Modelsim仿真,以便于将处理的波形结果进行对比,以此来反映处理信号滤波处理的软件和硬件实现效果,并使用Matlab计算处理过后的信号干性比和信号强度。

3.1 Matlab算法仿真

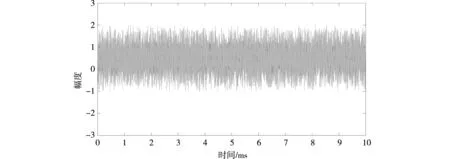

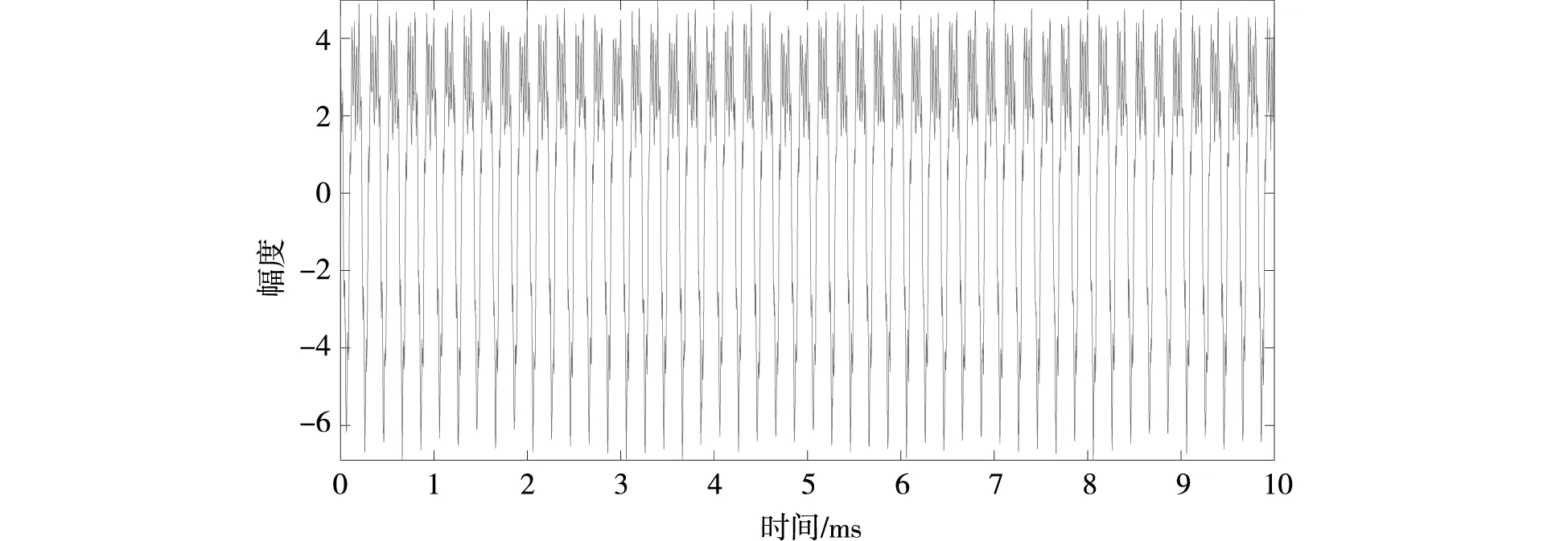

首先使用Matlab软件对该LMS算法进行仿真。使用simulink产生一段持续时间为10ms的测试信号,将其视作有用信号。然后对所产生信号以抽样频率为4000Hz进行采集,共采集了一段时间内的4096个数据点,得到如图6所示的信号时域波形图。

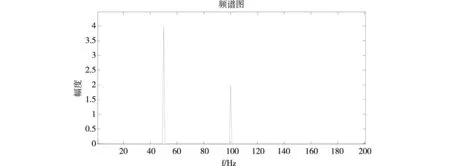

然后将50Hz工频干扰信号和100Hz干扰信号和它进行混叠,并设定待处理信号的干信比为10db得到如图7所示的信号波形,作为待处理信号添加到LMS算法的输入端在Matlab上实现该算。对待处理信号进行幅频变换可得如图8所示的幅频信号波形图。

从图8可以看出,当有用信号叠加窄带干扰信号之后,在干扰信号的频率附近叠加信号的幅度会显著变大。如图7中所示,当窄带干扰的个数和强度达到一定程度时可将输入的有用信号完全覆盖掉,几乎无法分辨出原有用信号。由此可见,强窄带干扰对监测信号的正常采集影响极大,说明了对这一信号进行处理的必要性。

使用陷波算法对这一叠加的信号进行干扰滤除处理之后即可得到如图9所示的信号即为所得的结果。由滤除后的图形和待处理信号的时域波形可知,在经过LMS算法的逐步逼近过程之后,输出信号与原有用信号的误差开始逐步变小,最终将有用信号从混叠的待处理信号中分离出来。

经过计算可得,待处理信号的,干性比为-3.6db,即显著降低了13.6db,有用信号为15.07db,即损失了0.05db,实现了对原有用信号的成功识别。

图6 有用信号时域图

图7 待处理信号时域图

图8 待处理信号频域图

图9 MATLAB滤波处理后的信号

3.2 FPGA仿真

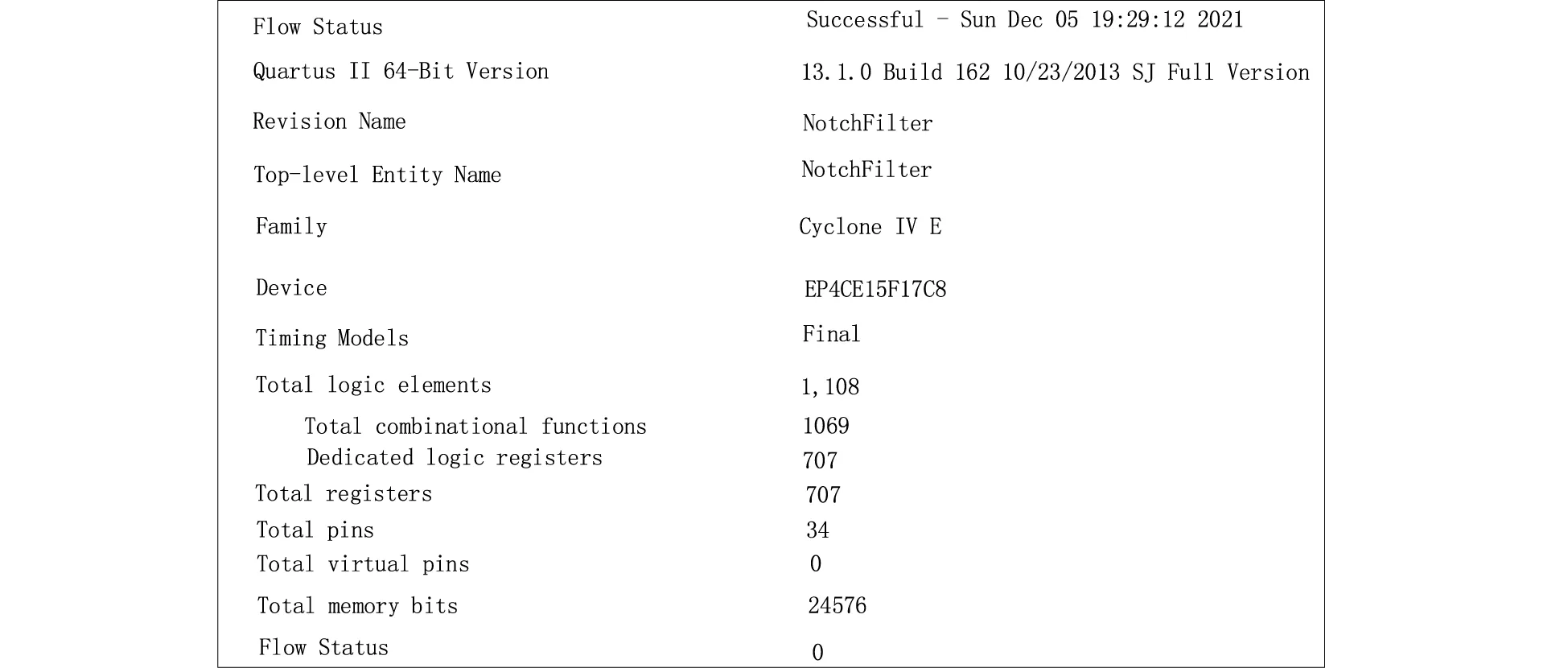

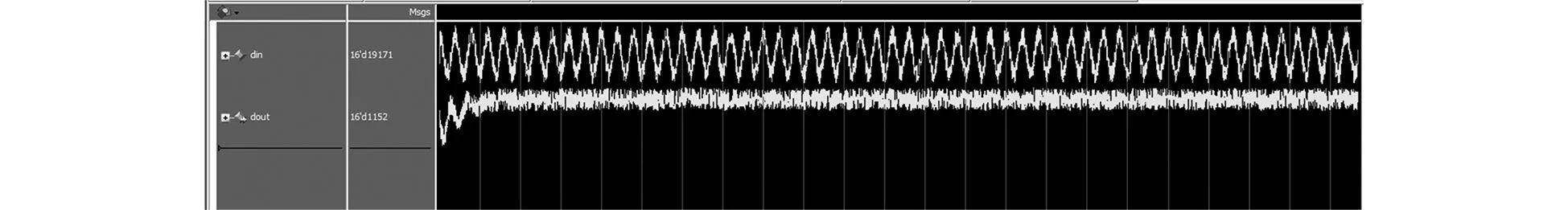

将Matlab产生的待处理信号数据导入到QuartusII13.1的rom核之中,再将这个rom核进行实例化引用待处理信号,并接入到处理板中进行频域陷波算法处理,处理结束后得到如图10所示的资源占用图。再编写tb仿真程序在Modelsim平台上进行仿真处理,得到如图11所示的仿真图像波形,待处理信号为din,输出信号为dout,其波形与Matlab处理后的波形相同,表明在FPGA上实现了这一算法。将处理过后的波形数据导出并保存为txt文件,使用Matlab软件对该波形数据进行计算。结果表明,经过FPGA硬件处理后得到结果与Matlab软件处理的效果接近,干扰信号被有效地抑制。最后,使用Matlab计算其平均功率可得进行抑制后干性比为-3.3db。

图10 资源占用图

图11 Modelsim仿真波形

结语

随着各种电气和机械自动化设备的飞速发展,对这些设备运行状态的监测也越发受人关注[11-12],针对监测过程中各种工频以及谐波电流的强窄带干扰,采用了基于LMS的自适应算法的频率陷波处理,对有用信号和窄带强干扰信号混叠的待处理信号进行频率陷波时,由Matalb和FPGA的联合仿真结果分析可知:

(1)FPGA对待处理信号的仿真指标略低于Matlab上的仿真运算结果,这可能是由于数据在处理过程中的约分引起的,不影响对有用信号的提取。

(2)强窄带干扰信号对信号的影响十分强烈,在多个频率的信号干扰下,有用信号的提取会受到严重影响。

(3)采用自适应频率陷波器在信号收到单个或多个频率信号的干扰,具有良好的抑制效果,还可以根据输入干扰信号的幅度和相位调节其滤波参数,实现自适应特性。

基于LMS作为自适应算法的自适应陷波器的采集信号窄带干扰过滤,针对一个或多个频率的窄带干扰信号的处理进行有效滤除,消除工频和谐波干扰,处理过后的数据可以更加明显地反映出系统的运行状态。