一种适用于低电压应用的低漏电高性能电荷泵

2022-05-06张云峰李睿文柳成林

张云峰, 李睿文, 柳成林, 程 心

(合肥工业大学 电子科学与应用物理学院,安徽 合肥 230601)

0 引 言

DCP的关键设计参数包括稳态输出电压、上升时间和输出电压纹波,通过这些限制可以设置电路最小所需的阶数和泵浦电容值[7]。基于二极管或MOS管的CTSs通常受二极管阈值电压的严重限制,为了降低这种典型缺陷造成的影响,很多文献提出各自的结构,如文献[8]中的锁存型DCP、文献[9]使用动态门控CTSs的DCP、文献[3]中的带自举开关的DCP以及文献[6]中的时钟增压等。这些方案使用较为广泛,能够有效消除有源器件在传导阶段的阈值压降效应,但是往往需要输入电压高于晶体管阈值电压。目前有许多(如能量收集和智能传感器节点等)应用于物联网系统中的结构,需要升压DC-DC变换器在非常低的输入电压时正常工作,并且输出电流相对较高[4-6]。针对这类应用,文献[10]提出一种新的结构,它可以在输入电压低于MOS晶体管阈值电压1/2的情况下工作,并且相对其他结构,它在电压转换效率(voltage conversion efficiency,VCE)、功率效率、驱动电流范围和响应速度方面性能更好。但是这种结构在输入电压接近MOS晶体管阈值电压时,CTSs存在较大的反向漏电流,使得其VCE相比锁存型DCP反而更低。

本文提出一种新的电荷泵结构,使用增压结构改变节点电压,有效降低CTSs的反向漏电流,从而提高电荷泵的VCE,此外该电荷泵结构的功率效率和响应速度方面相比文献[10]都得到了提高,总体性能更优。

1 栅极偏置低压电荷泵

无论是在慢开关限制系统中还是在快开关限制系统中,CTSs电阻都是影响DCP的关键参数之一,为了提高DCP性能,必须尽力降低其中的CTSs电阻[11]。

在实际DCP电路中,CTSs电阻通常为处于三极管区域的NMOS和PMOS晶体管的电阻。忽略短沟道效应,工作在三极管区域的NMOS和PMOS晶体管的电阻可以近似表示为:

(1)

(2)

其中:μn为电子迁移率;μp为空穴迁移率;Cox为单位面积的栅电容;(W/L)N、(W/L)P为晶体管宽长比;Vtn、Vtp分别为NMOS、PMOS晶体管的阈值电压;VGS=-VSG为MOS晶体管的栅源电压。由(1)式、(2)式可以看出,增加VGS会有效降低CTSs电阻。在传统DCP中,CTSs的VGS值一般等于时钟振幅即输入电压VDD。因此使VGS值高于时钟振幅,可以进一步降低CTSs电阻。

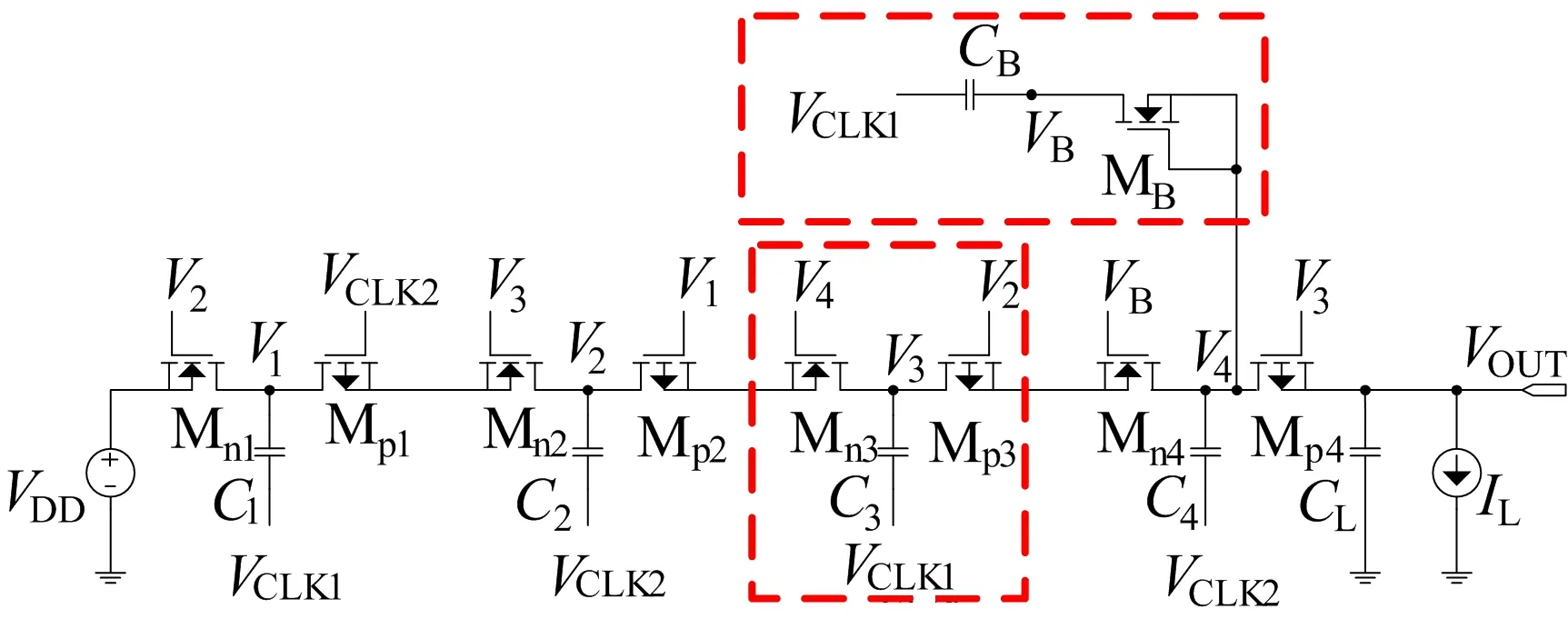

4阶栅极偏置电荷泵结构如图1所示。该结构能够为CTSs的MOS晶体管提供2倍时钟振幅的VGS值。图1中:VDD为输入电压;VCLK1、VCLK2表示频率为f、振幅为VDD的互补时钟信号;C1~C4为泵浦电容;CL为输出电容;恒流源IL近似表示负载,用来模拟由DCP提供的系统电流消耗。电荷泵共4阶,每阶电路结构如图1最下方的红色虚线框所示,每个CTS由1个NMOS和1个PMOS晶体管串联组成。在电荷传导阶段,电荷由PMOS晶体管流向下一阶CTSs的NMOS晶体管。另外,所有MOS晶体管的衬底与源极连接,因此晶体管不受体效应影响。电荷传导阶段的CTS电阻可以表示为(1) 式、(2) 式的和。

图1 4阶栅极偏置电荷泵结构

以图1中最下方红色虚线框中第3阶电荷泵为例,NMOS晶体管Mn3的栅极连接到节点V4(即下一阶的输出电压),PMOS晶体管Mp3的栅极连接到节点V2(即上一阶的输出电压)。该电荷泵除了第1阶与最后一阶之外的每一阶都是按此规律构建的。而为了与其他CTS保持相同的VGS值,第1阶PMOS晶体管的栅极连接到时钟信号VCLK2,最后一阶如图1最上方红色虚线框所示,由1个辅助NMOS晶体管MB与1个小电容CB产生节点电压VB作为本阶NMOS晶体管Mn4的栅极电压。

教学中,教师不仅要看到数学的知识、技能,还应看到隐藏在数学知识里的思想、精神、观念、价值观等,要充分利用教材,挖掘教材章头图,培养学生的直观想象能力。例如:北师大版七年级下册第一章《整式的乘除》,利用章头图(如图),让学生充分想象本章将要学习什么?为什么学?怎么学?让学生说说对将要学习的内容了解多少?让学生充分交流发言,既提高了学生学习的积极性,又了解了学生对不等式相关知识的掌握情况,教师才能有依据地对本章教学做到因材施教,同时培养学生的直观想象能力。

当时钟VCLK1为高电平时,Mn3截止,Mp3导通,电荷由C3传导至C4,此时节点V2电压值为2VDD,节点V3电压值等于V4电压值为4VDD,因此Mp3的VGS值为2VDD;当时钟VCLK1为低电平时,Mn3导通,Mp3截止,电荷由C2传导至C3,此时节点V2电压值等于V3电压值为3VDD,节点V4电压值为5VDD,因此Mn3的VGS值也为2VDD。2倍时钟振幅的VGS可显著降低CTSs的电阻值。

2 本文提出的低漏电电荷泵

2.1 低漏电流的电荷泵结构

图1的电荷泵结构虽然在电荷传导阶段可以有效降低CTSs的电阻值,但在电荷截止阶段时由于NMOS晶体管呈现二极管连接状态,使得此时CTSs存在不低的反向漏电流。仍以上节第3阶电荷泵为例,当VCLK1为高电平即VCLK2为低电平时,电荷由C3传导至C4,C2与C3之间处于截止状态,由于此时节点V3电压值等于V4电压值,NMOS晶体管Mn3相当于1个有源二极管,此时节点V3电压值远高于节点V2电压值,因此有部分电荷由C3反向传导回C2形成反向漏电流。这部分反向电荷的损耗,使得电荷泵的VCE降低,上升时间增加,也会降低总体功率效率。此外,随着输入电压VDD的增大,这种影响也会随之加剧。

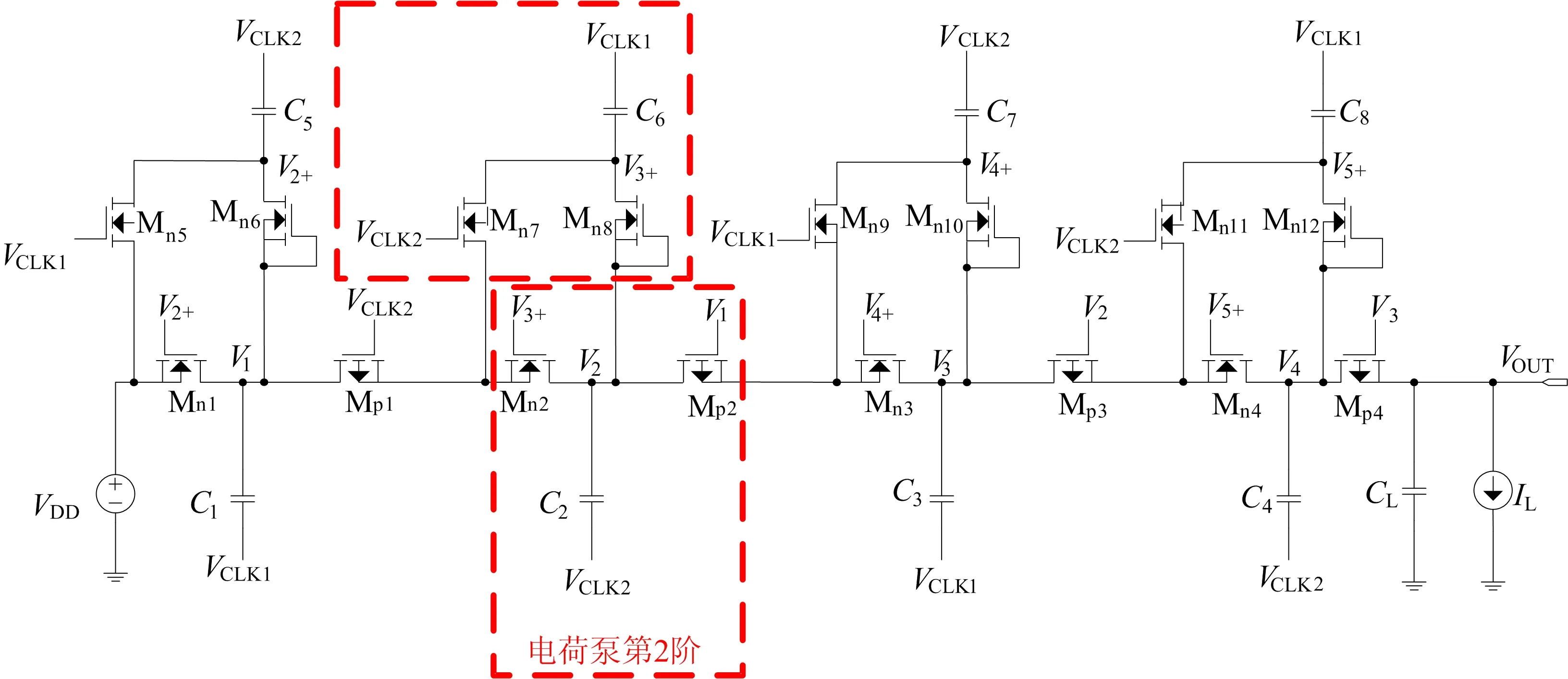

针对以上问题,本文提出低漏电的4阶电荷泵的结构,如图2所示。每一阶都利用1个辅助NMOS晶体管与1个小电容产生的节点电压作为CTSs的NMOS晶体管的栅极电压,并且通过互补时钟信号VCLK1与VCLK2控制1个开关管来改变电荷泵每阶之间的节点电压,从而在电荷截止阶段降低反向漏电流。以图2中红色虚线框为例,下方虚线框表示电荷泵第2阶,其中PMOS晶体管Mp2的栅极连接到节点V1(即上一阶的输出电压),而NMOS晶体管Mn2的栅极电压由上方虚线框中的辅助NMOS晶体管Mn8和小电容C6产生的节点电压V3+提供,另外由VCLK2控制开关管Mn7的导通与截止。

图2 4阶低漏电电荷泵结构

当VCLK1为高电平即VCLK2为低电平时,Mn2导通,Mp2截止,开关管Mn7截止,电荷由C1传导至C2,此时节点V1电压值等于V2电压值为2VDD,而节点V3+的电压值为4VDD,因此Mn2的VGS值仍为2VDD;而当VCLK1为低电平即VCLK2为高电平时,Mn2截止,Mp2导通,电荷由C2传导至C3,此时节点V1电压值等于VDD,节点V2电压值为3VDD,节点V3+的电压值也为3VDD,因为此时开关管Mn7导通,所以电荷泵第2阶与前一阶中间节点电压也上升为3VDD,即Mn2的栅源漏电压均相等,VGS=VDS=0,使得反向漏电流相比图1结构大大减少。

2.2 减少反向漏电流的工作原理

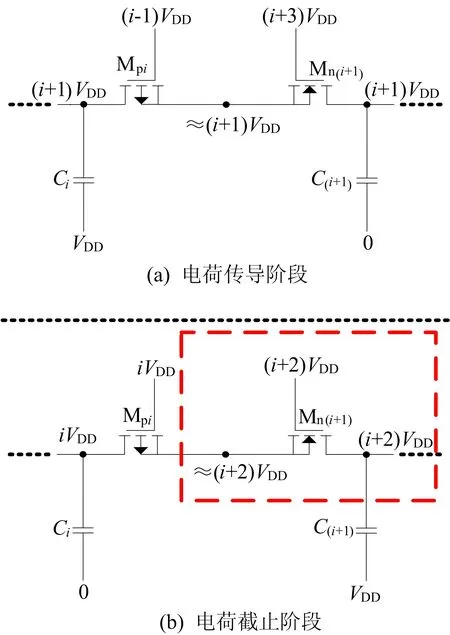

本节简要分析CTSs在时钟高低电平时的工作原理。包括VCLK1为高(即电荷传导阶段)和VCLK1为低(即电荷截止阶段)时的电荷泵第i阶与(i+1)阶CTSs的状态图,以及电荷泵相邻两阶的部分PMOS晶体管与NMOS晶体管栅极电压与稳态节点电压值,如图3所示。

假设电荷泵处于稳定状态,且无任何电流负载,图3a所示为当VCLK1=VDD且半周期结束时Mn(i+1)的栅源电压和Mpi的源栅电压均为2VDD。此时Mpi与Mn(i+1)导通,电荷由Ci传导至C(i+1)。在电荷传导阶段,该结构仍保持CTSs的NMOS晶体管和PMOS晶体管的VGS等于2VDD(即2倍时钟振幅),这可以使CTSs电阻大幅降低,并有效降低最小供电电压。

图3b所示为在电荷截止阶段即当VCLK1=0,VCLK2=VDD且半周期结束时CTSs的状态。因为此时CTSs不导电,从Ci至C(i+1)的3个节点电压由低至高,所以Mpi与Mn(i+1)晶体管的源极和漏极互换,Mn(i+1)的栅漏电压为0,Mpi的漏栅电压与源栅电源均为0。Mpi的漏极和栅极的电压均等于iVDD,晶体管呈现二极管连接,因此处于饱和区。并且此时第(i+1)阶上方的开关管处于导通状态,使得Mn(i+1)的晶体管状态如图3中红色虚线框所示,此时Mn(i+1)的源极电压升高至近似等于(i+2)VDD,因此该晶体管的漏极源极和栅极的电压均相等,近似处于截止状态。相比图1的栅极偏置电荷泵,图2中的低漏电电荷泵使得原本于电荷截止阶段存在的从C(i+1)流向Ci的反向电荷显著减少,反向漏电流减小,从而降低了电荷损耗,提高了VCE和功率效率。

图3 2个时钟半周期的电荷泵状态

3 仿真结果与分析

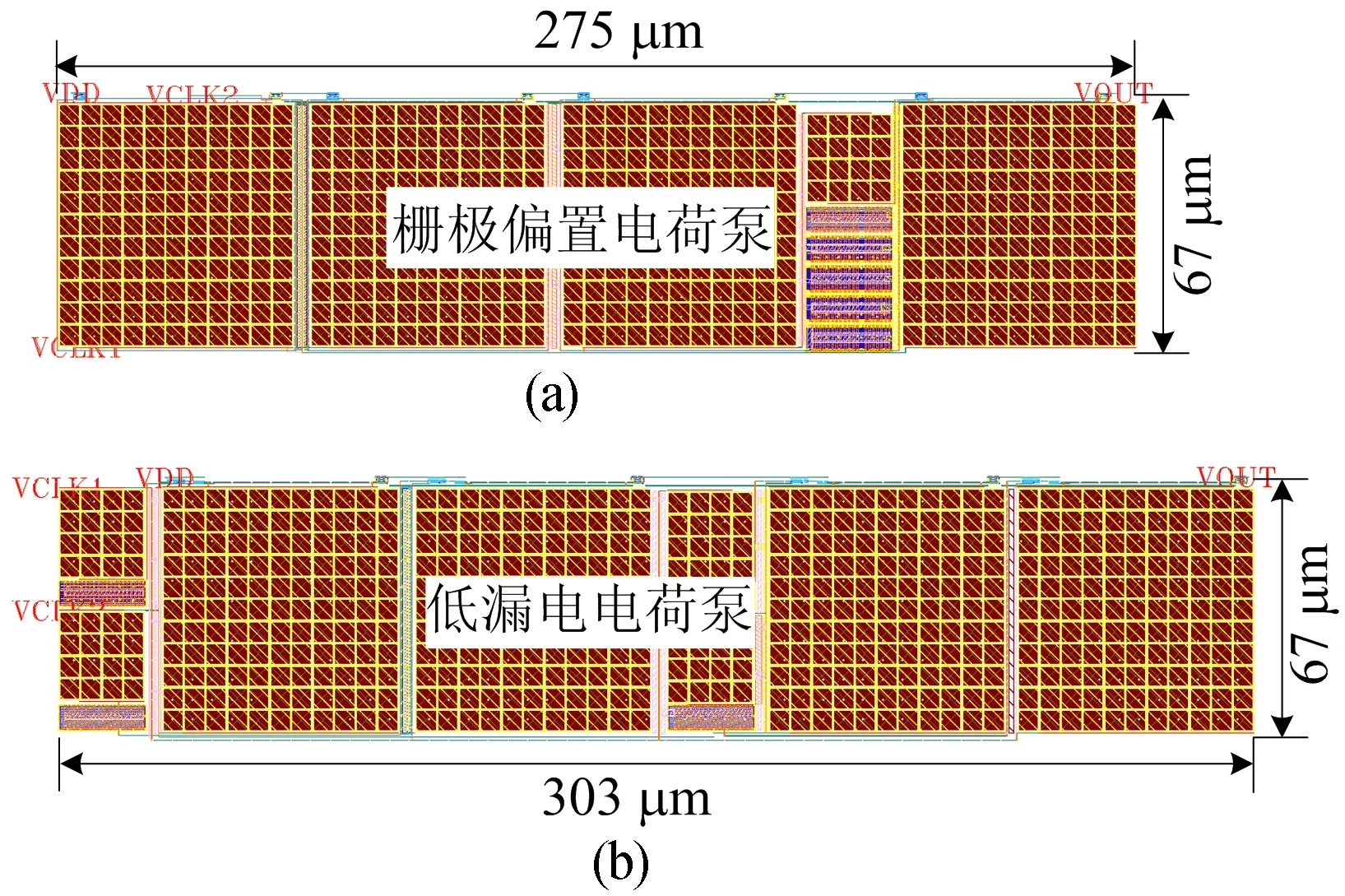

为了验证本文所提出的低漏电电荷泵的优势,使用Cadence分别搭建了图1中的4阶栅极偏置电荷泵和图2中的4阶低漏电电荷泵,并使用SMIC 40 nm CMOS标准工艺进行仿真。在这种工艺中,PMOS和NOMS晶体管的标准阈值电压分别为404、388 mV。绘制了4阶栅极偏置电荷泵和低漏电电荷泵的版图,占用面积分别为67×275 μm2和67×303 μm2,其中电容占据了绝大部分面积,如图4所示。

仿真中,本文设计参数包括互补时钟信号频率f=10 MHz,负载电流IL=5 μA,负载电容CL的容值为100 pF,输入电压VDD范围为200 ~400 mV。电荷泵的C1~C4容值均为10 pF,而小电容C5~C8的容值均为2 pF,CTSs中NMOS和PMOS晶体管的沟道长度均为100 nm,宽长比设置为100。

图4 电荷泵版图

采用相同的设计参数、晶体管尺寸和泵浦电容值,并根据版图后仿真结果,对所提出的低漏电电荷泵和栅极偏置电荷泵进行比较。因为低漏电电荷泵相比栅极偏置电荷泵多了一些晶体管与小电容,所以电路面积增加了约10%。重要的比较指标包括VCE、功率效率、驱动电流范围和响应速度(上升时间)。VCE为电压转换效率,定义为实际输出电压VOUT与理想输出电压之比,VVCE=Vout/(N+1)VDD,其中N为电荷泵阶数,而功率效率被定义为η=Pout/Pin。

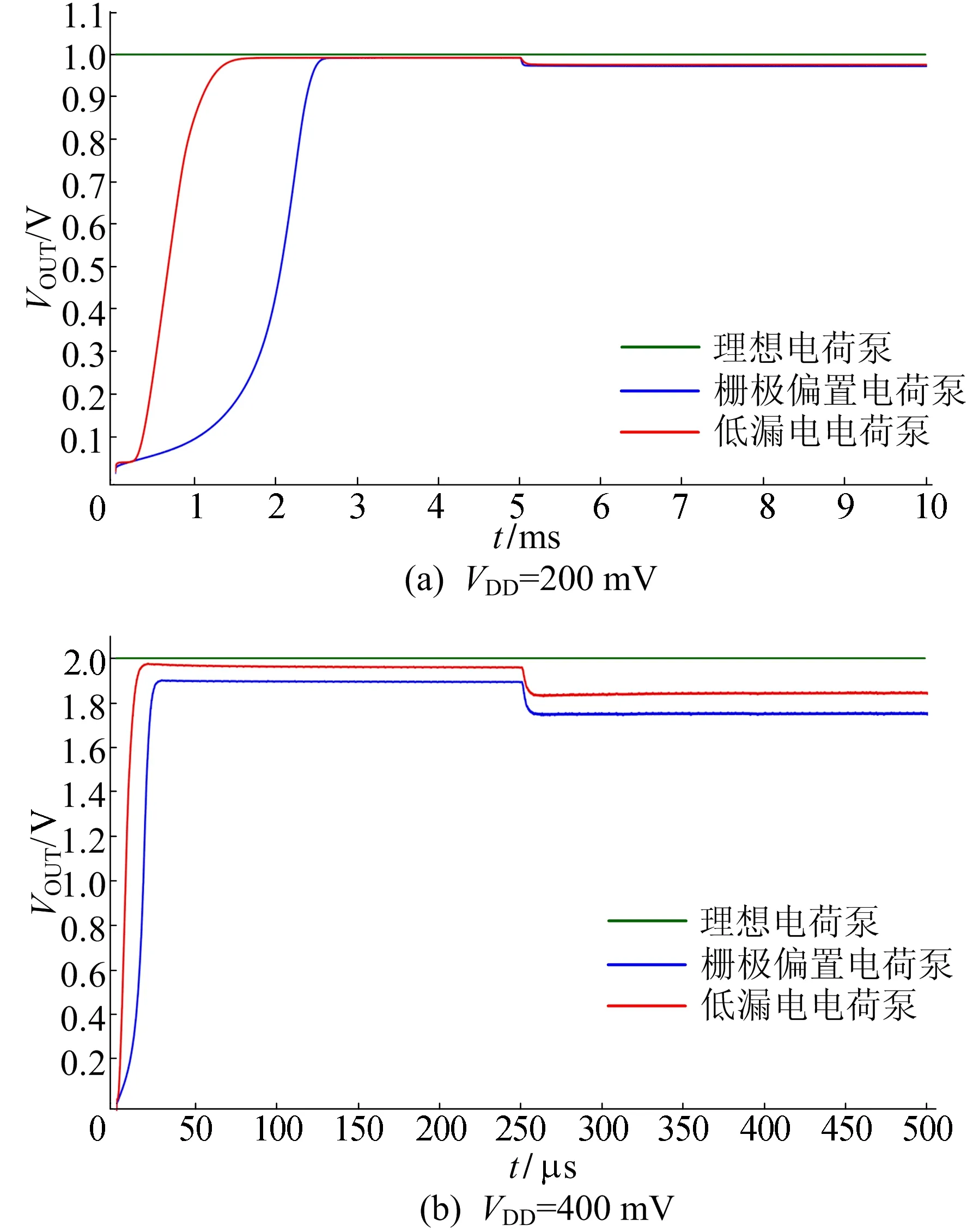

低漏电电荷泵和栅极偏置电荷泵分别在VDD=200 mV和VDD=400 mV下的输出电压VOUT仿真结果比较如图5所示。

图5 不同输入电压的电荷泵输出VOUT

当VDD=200 mV时,2个电荷泵首先在空负载的条件下工作到5 ms(VDD=400 mV时为250 μs),随后突然增加负载电流IL=1 μA(VDD=400 mV时为5 μA)。从图5可以看出,在空负载时低漏电电荷泵的输出电压高于栅极偏置电荷泵,尤其是在VDD=400 mV时更为显著。另外低漏电电荷泵的上升时间更短,响应速度更快。因为负载电流突然增加,所以输出电压会出现降低,从图5还可以看出,2种电荷泵的输出电压降幅均不大,表示都拥有良好的驱动能力。

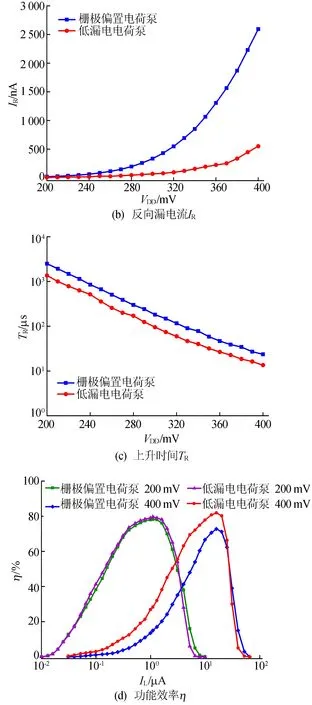

空负载条件下,输入电压VDD在200~400 mV范围内变化,输出电压VOUT如图6a所示。从图6a可以看出,因为相同输入下低漏电电荷泵的输出电压明显更高,所以其VCE更大,在VDD=400 mV时VCE经计算达到98.3%,相比栅极偏置型的94.2%提高约4.1%。

空负载条件下,输入电压VDD在200~400 mV范围内变化,电荷截止阶段CTSs的反向漏电流IR如图6b所示。从图6b可以看出,相同输入下低漏电电荷泵的反向漏电流明显更低,在VDD=400 mV时反向漏电流为550 nA,相比栅极偏置型的2 590 nA降低约78.9%。

VDD在200~400 mV范围内上升时间TR随VDD变化的关系如图6c所示。从图6c可以看出,低漏电电荷泵的上升时间总是更低,即响应速度更快。在VDD=200 mV时,低漏电电荷泵的上升时间约为1 360 μs,相比栅极偏置型的2 490 μs降低约45.4%。

在VDD=200 mV和VDD=400 mV下,栅极偏置和低漏电电荷泵的稳态功率效率η与负载电流IL的关系如图6d所示。

从图6d可以看出,当VDD为200 mV时,2种电荷泵的功率效率基本上相差不大;然而在VDD为400 mV时,低漏电电荷泵在轻负载时的η更高,相比栅极偏置电荷泵最高提高21.9%,且η最高达到81.9%。

图6 仿真结果对比

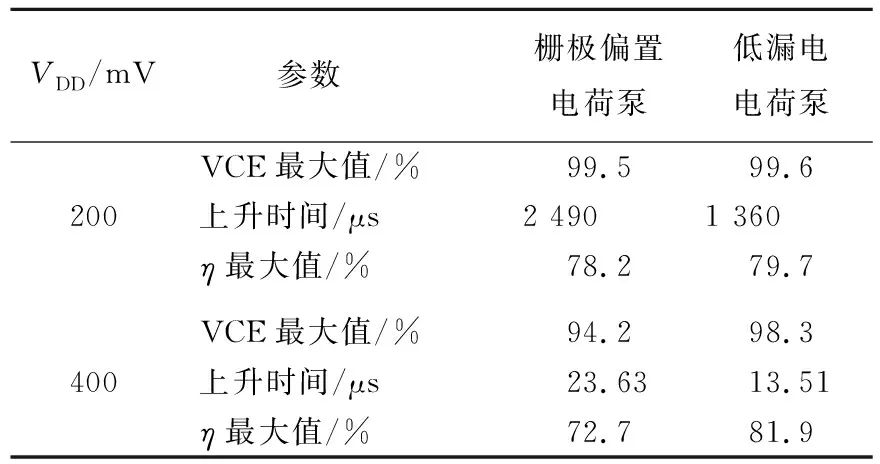

综上所述,本文的低漏电电荷泵总体性能更好。在VDD为200 mV和400 mV时的仿真结果比较见表1所列。

表1 仿真结果比较

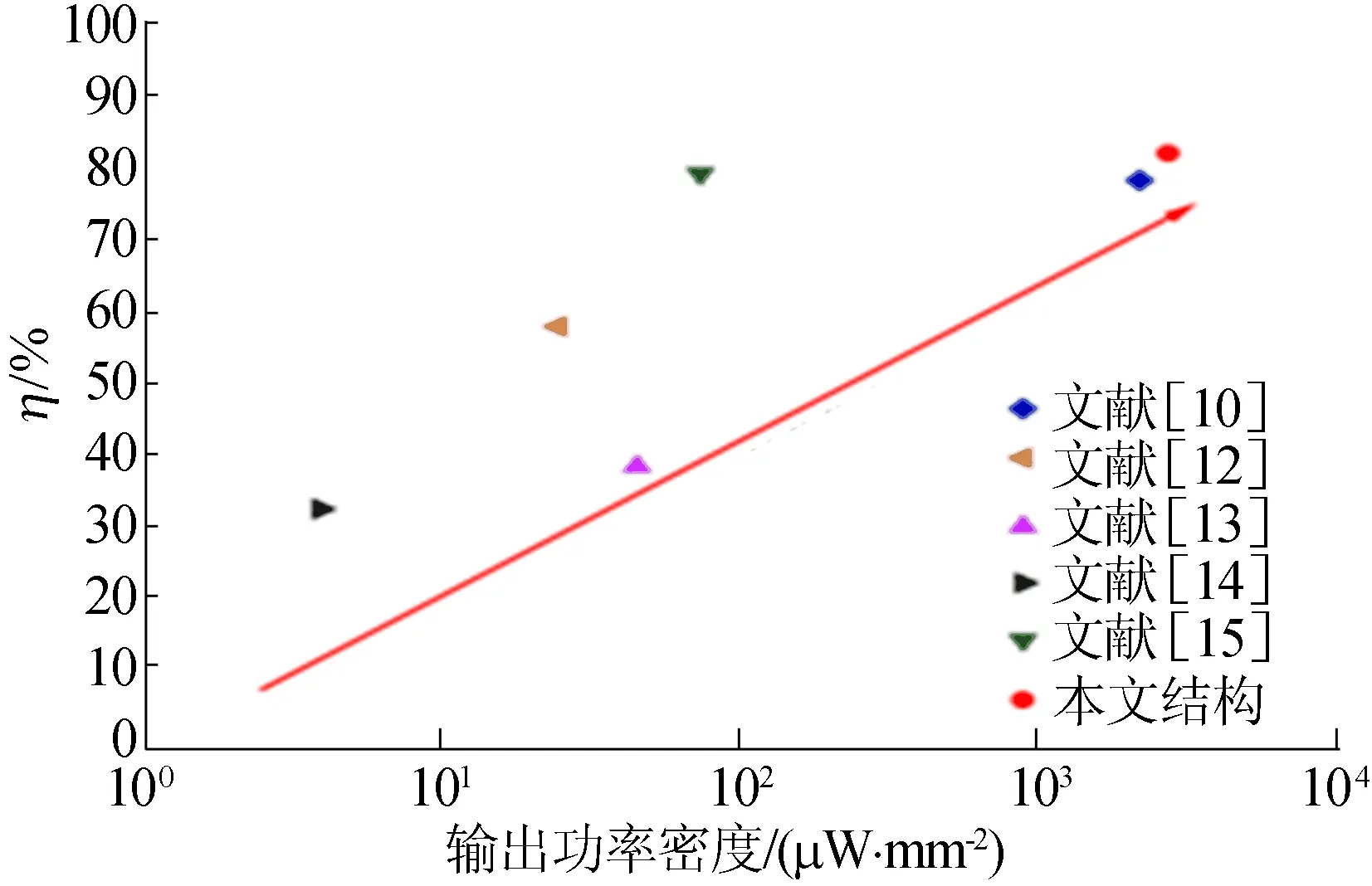

本文结构与现有文献结构的性能比较如图7所示。图7中数据点表示各文献电荷泵的最大功率转换效率η与输出功率密度的函数关系。显然,本文提出的低漏电电荷泵性能最高。

图7 本文结构与文献结构的性能比较

4 结 论

本文提出了一种新型低漏电电荷泵,在输入电压低于MOS管阈值电压时正常工作,具有较高的驱动能力。所提出的电荷泵在极低的输入电压下,不仅为CTSs提供2倍时钟振幅的栅极电压以降低CTSs的电阻,并且显著降低CTSs的反向漏电流,与原本的栅极偏置电荷泵相比,它的驱动电流范围良好,反向漏电流降低约78.9%,上升时间降低约45.4%,VCE提高约4.1%,轻负载功率效率最大提高21.9%。因此所提出的新型电荷泵在低输入电压应用中性能更好。