一种数模混合的低频锯齿波电路设计

2021-08-29何勇杰叶文霞陈宁锴

何勇杰,孙 江,叶文霞,陈宁锴,刘 炳

(西南交通大学 信息科学与技术学院,四川 成都 611756)

锯齿波是电路设计中常见波形之一。其波形先呈固定斜率上升,随后垂直下降,循环往复。其波形类似锯子的锯齿,故被命名为锯齿波。

锯齿波常用于扫描电路,如屏幕图像的显示电路。也可和比较器组合生成PWM 波,用于偏置晶体管基极或MOS 管栅极,达到调节输出的目的。PWM 是数字信号控制模拟量的有效途径,广泛应用在测量、通信、电机控制和LED 显示等许多领域中[1-2]。

采用数模混合方式设计的电路可以通过时钟的切换,将不同的电压按时序依次释放,便可得到电压随时间变化的信号。将不同的电压有序排列,并加入计数器和反馈电路实现对时钟的自定义计数和清零,即可生成梯形锯齿波。通过调节时钟频率、反馈节点和电压值,便可以调节梯形锯齿波的周期和幅值[3-5]。和传统方案相比,在生成大周期锯齿波时所需的芯片面积更小,抗干扰能力更强,电路的移植性更好。

电子点火器即采用PWM 控制MOS 管栅压的方式实现恒定输出[6-7]。符合要求的PWM 波形需要特定频率和幅值的锯齿波来生成[8-10]。本文为此设计的锯齿波生成电路采用数模混合的方式,节约了芯片面积,降低了干扰,可以生成合适的锯齿波供电子点火器使用。

1 传统方案

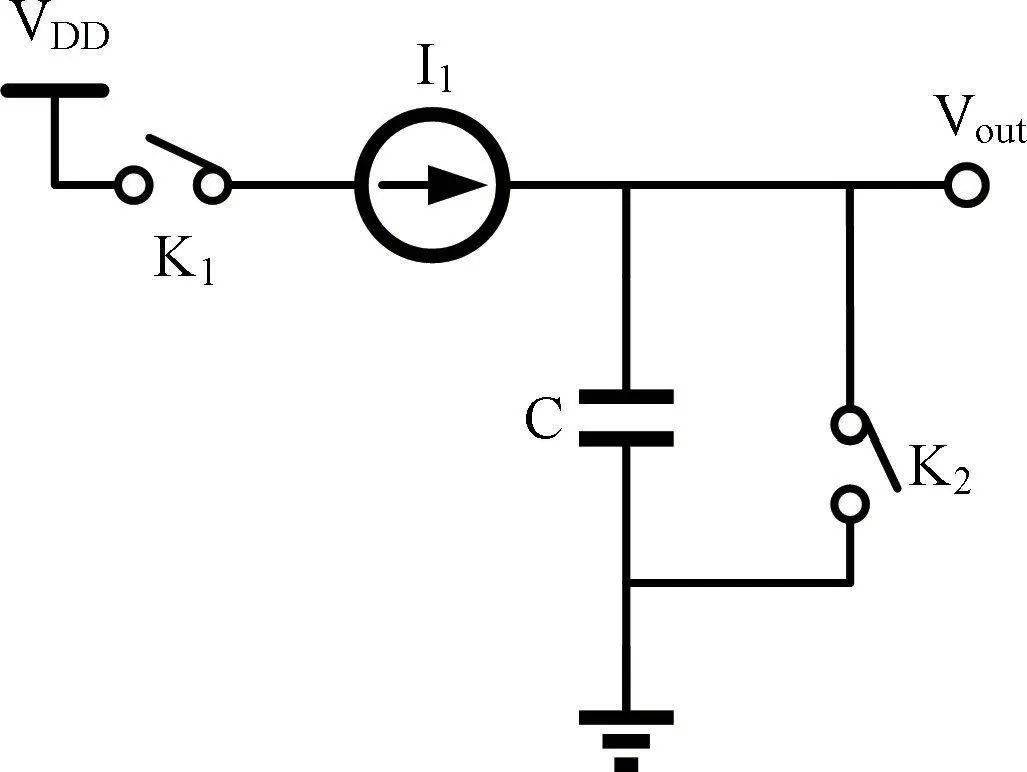

传统的模拟方案基本采用电容充放电方法生成锯齿波,通过控制充放电电流的大小和充放电时长来调节锯齿波的峰值和周期,原理如图1。

图1 电容充放电生成锯齿波原理图Fig.1 Schematic diagram of sawtooth wave generated by capacitor charging and discharging

传统结构满足公式:

式中:T为锯齿波的周期;C为电容的容值;Umax为电容充电上极板可达到的电压最大值;I1为充电电流大小。

由式(1)可知,令Umax=VDD,则要想使得T增大,必须增大C或者减小I1。假设电流设置到μA 级,CMOS 工艺中电容通常取到pF 级,所以T的数量级通常在μs 级别。

电子点火器发热丝工作时要求驱动信号周期为8~12 ms。按照传统结构要想把锯齿波周期做到ms 级别,就需要减小电流到原来的几千分之一或者增大电容为原来的几千倍,电流越小就越容易受到干扰,电容增大就要耗费更多芯片面积。

所以传统结构无法满足电子点火器PWM 波生成电路中对锯齿波周期的要求。因此,本文电路针对此进行创新改进。

2 改进后设计方案

图2 为改进后的电路设计架构图,采用数模混合设计,分为四个模块:双复位分频器、数字译码器、电阻分压网络和滤波反馈网络。双复位分频器将CLK信号分频生成六路数字信号;数字译码器将六路数字信号译码后用于后续的电压选择;电阻分压网络生成不同的电压,在数字译码器的输出信号控制下按时序输出电压;滤波反馈网络接收六路数字信号后采用数字逻辑反馈到分频器,决定锯齿波的周期大小和最大幅值[11-12]。

图2 锯齿波生成电路设计架构图Fig.2 Sawtooth wave generation circuit design architecture

2.1 双复位分频器

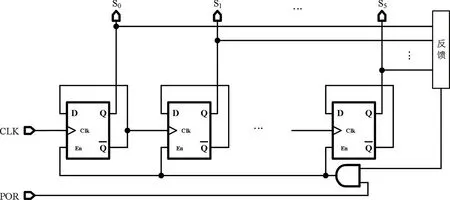

双复位分频器电路原理图如图3 所示,通过D 触发器将CLK 信号分频后得到S0~S5一系列信号。

图3 双复位分频器电路原理图Fig.3 Schematic diagram of double reset frequency divider

本电路中使用POR 上电复位信号和反馈信号双重控制使能端[13],既能保证电路在上电时清零,减少上电过程中亚稳态影响,又可以供用户自定义调整计数范围,设置不同的锯齿波周期。

S0~S5各输出端口频率和CLK 频率关系为:

式中:fSi为Si端口对应的输出频率;i为端口的下标;fCLK为CLK 端口的输入频率。

2.2 数字译码器

数字译码器用来将分频器生成的S0~S5六路数字信号译码为51 位独热信号和一位Yon信号,供后续的电阻分压网络使用[14],其电路原理图如图4。

图4 数字译码器电路原理图Fig.4 Schematic diagram of digital decoder circuit

数字译码器对应译码真值见表1。随着时钟的变化,双复位分频器模块生成的数字信号也在有规律切换。输入数字译码器后,输出信号Y1Y2…Y51Yon以独热码的形式随输入信号切换。

表1 数字译码器真值表Tab.1 The truth table of digital decoder

2.3 滤波反馈网络

滤波反馈网络用来设置锯齿波周期和电压阶数,其电路设计如图5。在电子点火器电路中,共分为51阶,即锯齿波的周期为CLK 的51 倍。所以滤波反馈网络要保证图4 中的S5S4S3S2S1S0六路数字信号在状态为110011(对应十进制数51)时,反馈到分频电路中将输出端清零,同时将分压网络输出电压置零。

图5 滤波反馈网络电路原理图Fig.5 Schematic diagram of filter feedback network

数字电路中,因为存在竞争冒险现象,在信号切换过程中会产生很多毛刺干扰,对后续电路的稳定性造成极大威胁。本电路中加入滤波模块,以消除干扰。RC 网络电阻R为451 kΩ,电容Cmos为110 fF,将数字信号延时50 ns 后释放,过滤掉脉冲宽度小于50 ns 的脉冲尖峰,增强抗干扰能力[15-16]。

在电子点火器电路设计中,CLK 为4.8 kHz,经过51 个周期计数分频后的频率约为94 Hz,周期为10.6 ms,符合设计指标。

2.4 电阻分压网络

本设计中采用的电阻分压网络为等比例电阻串联分压网络,结构简单,工艺实现成本低[17]。其电路设计如图6 所示。

图6 串联式电阻网络原理图Fig.6 Schematic diagram of series resistance network

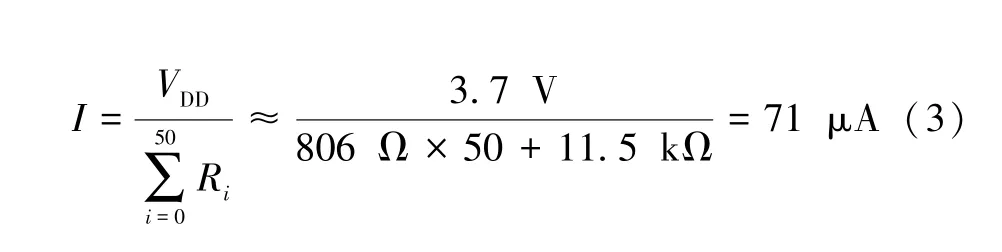

本结构由50 个等值电阻(R0~R49)串联来实现分压,电阻采用格罗方德工艺下ppolyf_u 电阻模型,宽长比为2 μm/10 μm,采用串联或并联的方式调整阻值均为806 Ω。为了节省功耗,电路中加入R50限流,其阻值设置为11.5 kΩ,本模块的电流为:

式中:I为电阻串联电路的电流;VDD为全局电源电压;Ri为下标i对应的电阻阻值。

本模块的电流值符合芯片的静态低功耗要求。

3 应用

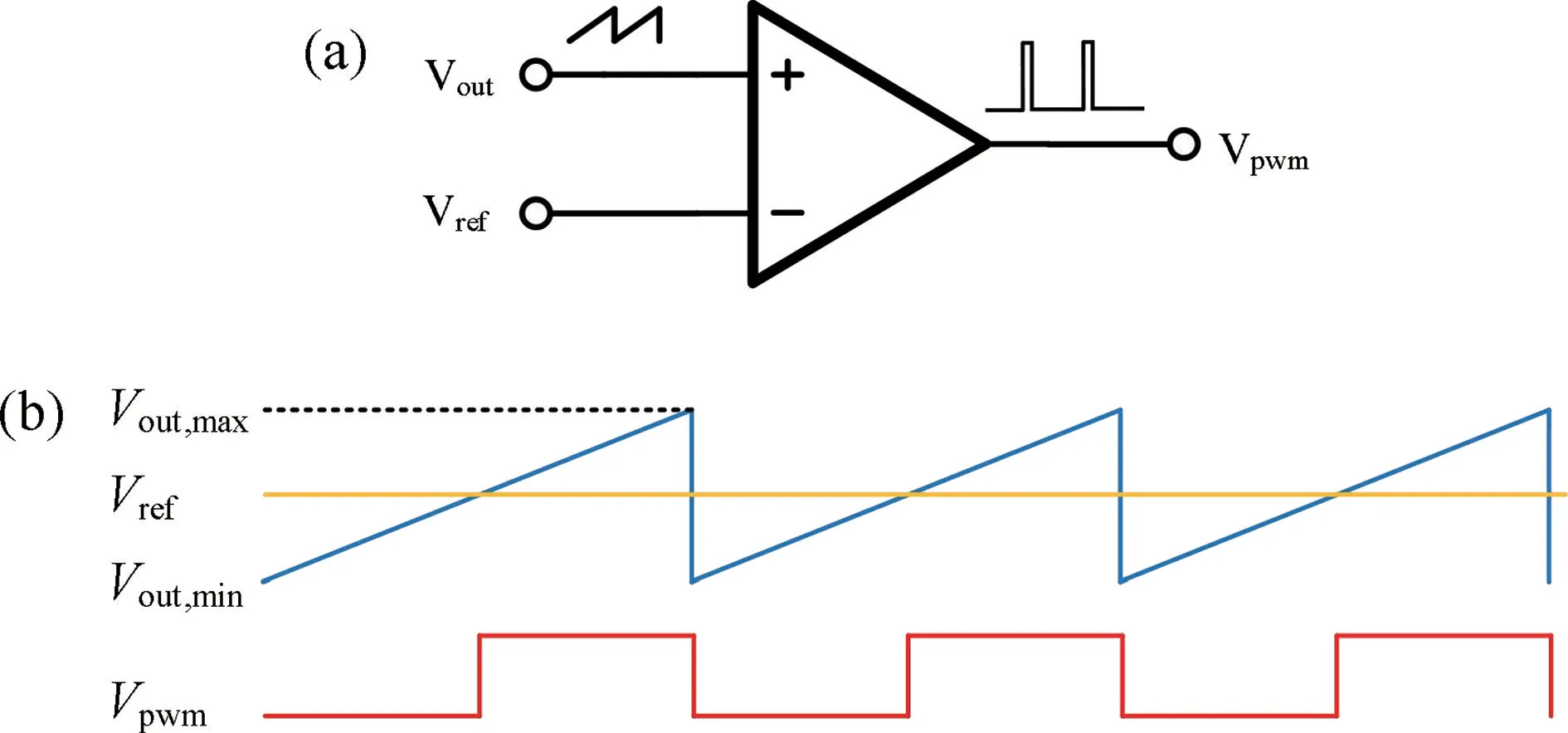

在电子点火器芯片中,使用PWM 信号控制加热丝输出端口的电压,保证输出端口电压的恒定。在低频锯齿波信号Vout生成之后,用比较电路处理后可得Vpwm[18]。Vpwm信号的生成电路和原理见图7。

图7 Vpwm生成电路和原理Fig.7 Generation circuit and principle of Vpwm

Vpwm占空比的计算公式为:

式中:D为Vpwm占空比;Vout,max为锯齿波电压最大值;Vout,min为锯齿波电压最小值;Vref为基准电压。通过调整锯齿波Vout的周期和幅值可以实现Vpwm占空比的调整,进而实现加热丝输出端口的电压的调整,使其保持恒定。

4 版图布局

采用格罗方德0.18 μm BCD 工艺流片,包含3 层金属,19 张掩膜版。芯片总面积为1 mm2,低频锯齿波生成电路版图布局如图8 所示。图中①②③④分别表示模块为:数字译码器、滤波反馈网络、双复位分频器和电阻分压网络。电子点火器控制芯片实物解剖照片如图9,白框内为低频锯齿波生成电路的实际位置。

图8 低频锯齿波电路版图Fig.8 Low frequency sawtooth circuit layout

图9 电子点火器芯片解剖图Fig.9 Anatomy of electronic igniter chip

5 电路仿真和测试结果

参考图2,设置CLK 频率为4.8 kHz,VDD=3.7 V,对该电路仿真后在Vout处得到仿真波形如图10。

图10 仿真波形图Fig.10 Simulation waveform

由仿真波形可以看出,梯形锯齿波经历51 阶,从4.1 mV 爬升到2.8761 V,其周期为10.598 ms。仿真结果和设计预期高度一致。

本文设计的低频锯齿波生成电路置于芯片内部无法直接测试,故采用间接测试的方式来证明其正确性。参考图7,PWM 波是由低频锯齿波生成的,二者的周期是一致的,所以可以通过测试芯片输出端口的PWM波形验证本文设计的低频锯齿波的周期。测试平台如图11,设置VDD为3.7 V,则预计输出端口应输出周期为6.2 ms 的PWM 波。

图11 芯片测试平台Fig.11 The platform of chip test

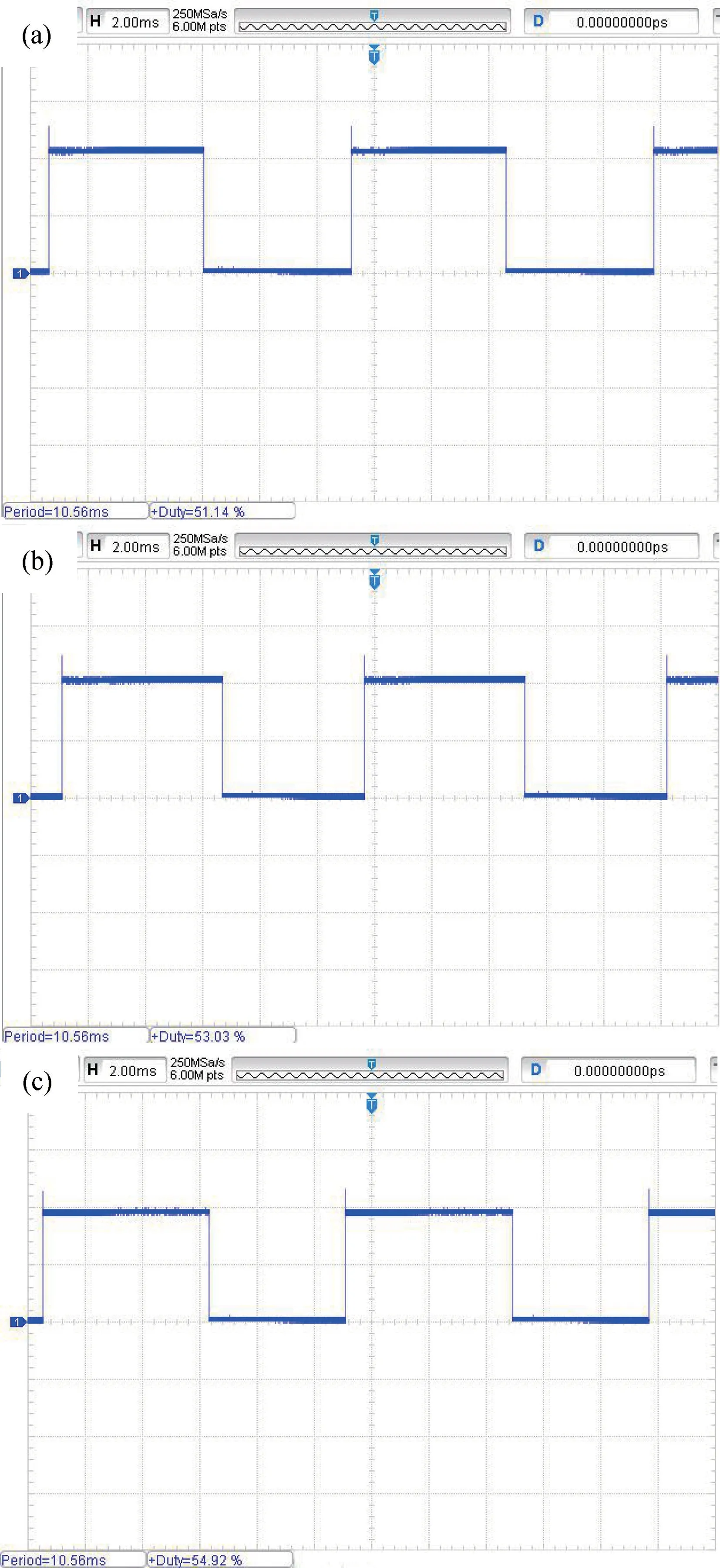

测试结果如图12 所示,(a),(b),(c)对应不同的PWM占空比,分别为 51.14%,53.03% 和54.92%。不同情况的PWM 周期均为10.56 ms,与仿真结果基本一致,误差为0.04 ms,在允许范围之内,证明本电路的正确性和实用性。

图12 芯片输出端口测试结果Fig.12 Test results of chip output port

6 结论

本文通过对传统锯齿波电路设计的改进,提出一种适用于电子点火器的低频锯齿波电路。采用数模混合设计,解决了单纯模拟设计耗费面积过大的问题。经过仿真和芯片的实际测试证明电路的正确性和实用性。本电路还可以通过修调滤波反馈网络来改变锯齿波的周期和幅值,具有较强的可移植性。