CMOS闩锁效应虚拟仿真实验设计

2021-04-27刘有耀

朱 筠,刘有耀,张 霞

(西安邮电大学电子工程学院,西安 710121)

0 引言

由于中国集成电路产业发展迅速,在集成电路产业带动下大量新兴产业快速发展、壮大,需要大量的集成电路设计和集成系统专业领域人才,对现有教学体系和实践平台建设提出了更高要求,要能够跟上最新产业的发展需求,才能培养出适合社会和企业需要的创新型人才[1-4]。

早在半个多世纪前就已经有学者开始研究CMOS电路闩锁效应。近几年,随着集成电路制造工艺水平的提高及计算机辅助设计工具的发展,对闩锁效应的研究工作越来越深入,能更直观全面的理解闩锁现象[5-6]。到21世纪,特征尺寸已进入亚微米级、甚至纳米级,人们不仅需要高精度仪器对CMOS电路进行定位、定量分析闩锁效应,更需要完善其理论,依靠计算机辅助工具预示出所设计的CMOS集成电路抗闩锁能力的强弱。虚拟仿真实验技术的发展和应用对闩锁效应的研究工作提供了坚实的工具基础[7-8]。

本文利用SILVACO TCAD软件设计了CMOS电路闩锁效应的虚拟仿真实验,通过交互式工具和可视化输出使学生对CMOS电路闩锁效应的发生及抑制有较全面和更直接的认识,同时对以后CMOS电路的分析设计打下坚实的基础。

1 CMOS闩锁效应分析

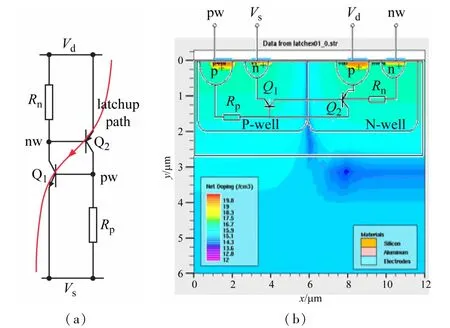

闩锁效应[9-10],是指CMOS 器件结构中寄生的双极晶体管(又称寄生可控硅,简称SCR)被触发导通后,会在电源VDD与地(GND)之间形成低阻抗大电流通路,有可能导致器件无法正常工作,严重时会造成CMOS电路的永久性损毁,如图1(a)所示。

图1 CMOS电路中的闩锁效应

图1(b)为发生闩锁时电流电压曲线图,起初外加一个较小的电压(U<Utrig),SCR在高阻抗状态下流过VDD~GND的电流是非常小的。当外加电压不断增加,增加到转折电压Utrig时,电压值大于CMOS结构中的反向偏置电压,产生了一个反向击穿电流,此电流流过阱(或衬底)中的寄生电阻Rn,使PNP管发射结正偏即Q2导通。继而Q1(NPN管)也导通,打开再生反馈机制。在图中这个过渡区域表示为负阻区,是不稳定的。若Q1和Q2的电流增益乘积大于1,正反馈机制得以维持,电流会不断增大,导致大电流从VDD~GND 流过,并锁定在极小电压[11-12]。

若产生的闩锁电流不受限制,则可以烧坏CMOS电路;即使闩锁电流是受限制的,CMOS电路没有永久性损害的发生,但是由于VDD和GND之间存在一条低阻抗路径,仍有导致电路故障的潜在危害。

2 闩锁效应仿真结构搭建及仿真

2.1 搭建闩锁效应仿真结构

本实验利用SILVACO TCAD软件对CMOS电路中由于SCR产生的闩锁效应进行虚拟仿真。如图1(a)所示,双阱CMOS 器件结构p 阱(P-well)中的NMOS器件源极接GND,漏极接输出端Output。当横向寄生的NPN管Q1导通时,首先是作为源极的N+端被触发,作为漏极的N+端对Q1的影响可以忽略[8]。因此,在应用ATHENA工艺仿真器进行建模仿真时,对比图2(a)略去NMOS器件中作为漏极的N+端,只形成一个n+掺杂区作为Q1的发射区,接电极Vs。

图2 CMOS电路闩锁效应仿真结构

同理,n阱(N-well)中的PMOS管源极接电源VDD,漏极接输出端Output。对于纵向寄生PNP管Q2,作为源极的P+端更易于触发,作为漏极的P+端对Q2的影响可以忽略。故搭建仿真结构时略去PMOS管的漏极P+端,只建立一个p+掺杂区,作为Q2管的发射区,接电极Vd。并分别在P-well中掺杂形成p+区接电极pw,N-well中掺杂形成n+区接电极nw,得到如图2(b)所示简化的CMOS电路闩锁效应仿真结构,采用双阱工艺,引出电极pw、Vs、Vd、nw,其中各部分掺杂及杂质浓度设置如表1所示。

2.2 闩所效应的触发仿真

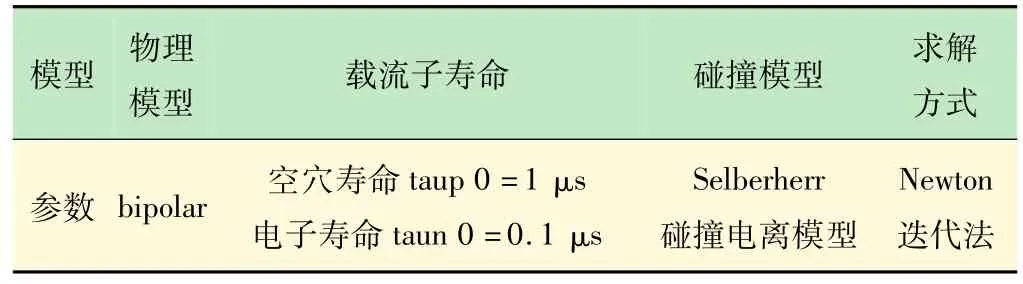

将ATHENA产生的CMOS结构导入ATLAS器件仿真器,并设置材料类型、模型参数、及载流子的寿命。电子寿命或空穴寿命的大小均会影响寄生SCR的电流增益,并同时考虑碰撞电离效应,具体参数设置见表2。

表1 ATHENA搭建的闩锁仿真结构各部分掺杂参数

表2 ATLAS仿真时设置的模型及参数

仿真时,当存在正常脉冲偏置电压时,闩锁效应被触发,刚开始时电流会缓慢增大;当电压大于转折电压后,电流增大幅度逐渐减小;但在快结束时电流又急剧增大,电流电压特性曲线如图1(b)所示。

图3给出了CMOS器件在加有偏置电压后的瞬态仿真,图中的INITIAL、INTERMEDIATE及FINAL分别为器件在触发前、触发中、以及触发后3种状态下的衬底电势及电流分布情况。

图3 触发闩锁时CMOS器件衬底电势分布图

INITIAL反映了刚加有偏置电压时衬底电势情况,由于在nw和Vd上加有正偏压(0~5 V),故N-well区域的电位最高,颜色表现为红色;而P-well区域电位最低为紫色。

INTERMEDIATE是触发3 ps后衬底的电势变化,并同时标识出了衬底中的位移电流线。脉冲电压的上升沿和下降沿,会在衬底和负载之间产生一定的电压差,从而在衬底中产生位移电流。当CMOS器件被闩锁触发后,从Vd到Vs之间会有明显的电流流过,由两个区域的电势颜色可明显看出,N-well区域的电势降低,而P-well区域的电势明显上升。

FINAL是闩锁触发后1ns时的衬底电势情况,闩锁效应发生后会改变器件衬底电势的分布情况,P-well区域电压从5 V减小至4 V左右(颜色由最初的红色变为最终的黄色),N-well区域的电压则从0增大到2 V左右(颜色从紫色变为蓝色和绿色)。

若闩锁效应不发生,器件应该在短暂的触发后回到初始状态,也就是说图3中FINAL和INITIAL的瞬态仿真应该相似,但事实上,图3中FINAL和INITIAL明显不同,这就是由闩锁效应所导致的。

3 抗闩锁结构的仿真

研究分析闩锁效应的产生及触发,是为了能够更好的避免闩锁效应的发生。CMOS电路中的闩锁效应是由寄生的NPN管和PNP管同时导通引起的,只要不满足产生闩锁的条件,就可以避免闩锁效应的发生。比如,若能使两个寄生晶体管放大增益的乘积小于1,则无法形成正反馈回路,两个晶体管无法同时导通,闩锁就可以防止。通过集成电路工艺技术及版图设计可以实现抑制闩锁效应的发生。本实验选取3种常用抗闩锁结构[13-15],设计其仿真结构并观察其闩锁触发的瞬态仿真结果。

3.1 深槽隔离结构

在CMOS 器件中P-well、N-well有源区的中间制作一个深的绝缘槽体,增大寄生晶体管的基区宽度,可以降低横向NPN管的增益,削弱PNPN的放电路径,能有效抑制闩锁效应的触发。如图4(a)、(b)所示,实验中选择绝缘体材料Si3N4填充深槽,槽的深度至少应大于阱的深度,才能起到抑制闩锁的作用。且槽深越大,抑制闩锁的能力越强、抑制效果越好。

3.2 保护环Guardring结构

分别在P-well区域和N-well区域内注入p+掺杂区和n+掺杂区作为多子保护环,搭建带有保护环的CMOS结构,如图4(d)、(e)所示。在衬底或阱中多子会形成电阻压降,或在注入到寄生晶体管的基区前就已经被保护环收集,因此,多子保护环短路了原本流向电极pw的电流,降低了多子电流在衬底上产生的电压降。相当于给原来的寄生电阻Rp并联一个阻值更小的电阻且连接到地,有效减小寄生电阻的阻值,防止形成闩锁。

3.3 绝缘体上硅技术(Silicon On Insulator,SOI)

SOI技术常采用3层夹心结构,最上层为制造器件的半导体薄层,中间层为用于隔离器件与衬底的隐埋氧化层,最下层为衬底硅,如图4(g)、(h)所示。SOI CMOS结构中加入隐埋氧化层后,增大了衬底的电阻阻抗,电子不会传输到下层进行迁移,电子束或电子本身的迁移速度增快,提高了整体CMOS电路的运行速度,芯片的集成度更高,功耗更低,有效改善整个芯片的电性能。由于氧化层阻断了寄生晶体管的正反馈路径的形成,从根本上避免了闩锁的形成。

图4 抗闩锁结构的仿真结果

由图4(c)、(f)、(i)显示的瞬态仿真截图看出,这3种抗闩锁结构在触发的前、中、后3个状态中衬底电势分布几乎是一样的。证明了带有Si3N4深槽隔离结构、Guardring结构、以及SOI CMOS结构均可以有效地抑制闩锁效应的触发,使得的FINAL和INITIAL是相似的。

抗闩锁效应的方法较多,有时候可以联合使用两种或几种抗闩锁措施。学生可在此实验的基础上,查询相关资料后选取合适的抗闩锁结构进行仿真,以帮助学生更深刻的理解CMOS闩锁触发条件及抑制方法。

4 结语

本文利用SILVACO TCAD软件设计了CMOS闩锁效应虚拟仿真实验,通过分析其触发条件及触发时刻衬底电流及电势分布情况,给出了常用3种抗闩锁结构的瞬态触发仿真结果。在课堂教学中充分利用虚拟仿真软件的强大功能,通过具体设置仿真结构和器件参数,以及可视化的图形界面,使原本抽象的触发过程变得具体形象,加深学生对理论知识的理解,把刚刚学到的理论知识利用计算机仿真形象化的再现出来,极大地激发了学生的学习热情和积极性,获得良好教学效果。