具有SLA结构的12位并行计数器架构的设计

2020-10-19张为,赵创,苗林

张 为,赵 创,苗 林

(1.天津大学微电子学院,天津 300072;2.长江存储科技有限公司设计部门,湖北武汉 430223)

0 引言

计数器是典型的时序逻辑电路[1],几乎应用于所有的数字电路和系统,如频率合成器、测量系统、模拟数字转换器和通信系统[2]。高速并行计数器在算术运算中有许多应用,包括神经网络和触发核仪器[3]。相比于大宽度的计数器,同步高速并行计数器应用更广泛[4]。在设计高速计数器的过程中,宽频带和高速的计数器会同时增大芯片面积,这是需要解决的问题。在VLSI规模下实现计数器的理想和重要的关键特性包括相对恒定的计数时间和更高的计数速度、数字输出和稳定的VLSI实现[5]。

1 D触发器的选择与设计

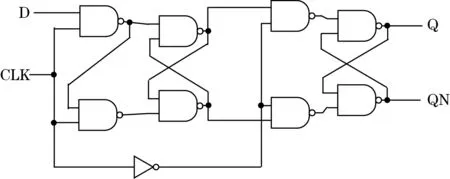

在时序逻辑电路中,基本存储元件是触发器,它可以在脉冲的上升沿或下降沿存储数据。传统的主从D触发器设计使用8个NAND门和一个反相器[6],如图1所示。

图1 传统主从D触发器

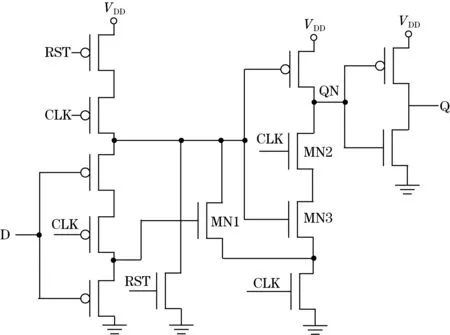

传统D触发器所含晶体管数目很多,使得其面积太大,所以需要设计一个含有少数目晶体管的D触发器,因此设计选择了正边沿触发TSPC(true single-phase clock)触发器。除此之外,TSPC触发器还具有功耗低和工作速度快的优点,但是缺点是有电荷共享现象且容易产生毛刺。

本文中选用一种消除毛刺和电荷共享的TSPC型D触发器,晶体管级的实现如图2所示[7],它由13个晶体管构成,分为3级,其中NMOS管MN1的尺寸大于NMOS管MN2的尺寸和NMOS管MN3的尺寸。当时钟信号为低电平时,第1级作为一个开启的锁存器接受输入信号,而第2级的输出节点被预充电,在此期间,第3级保持原来的输出状态。当时钟信号由低电平变换到高电平时,第1级不再开启且第2级开始定值,同时第3级变为开启而且将采样值传送到输出。在第1级加入一个PMOS管,第1级和第2级之间加入1个NMOS管,用来输入复位信号(RST)。其中MN1的尺寸要大于MN2和MN3的尺寸,以保证消除毛刺和电荷共享。

图2 TSPC型D触发器

2 并行计数器设计

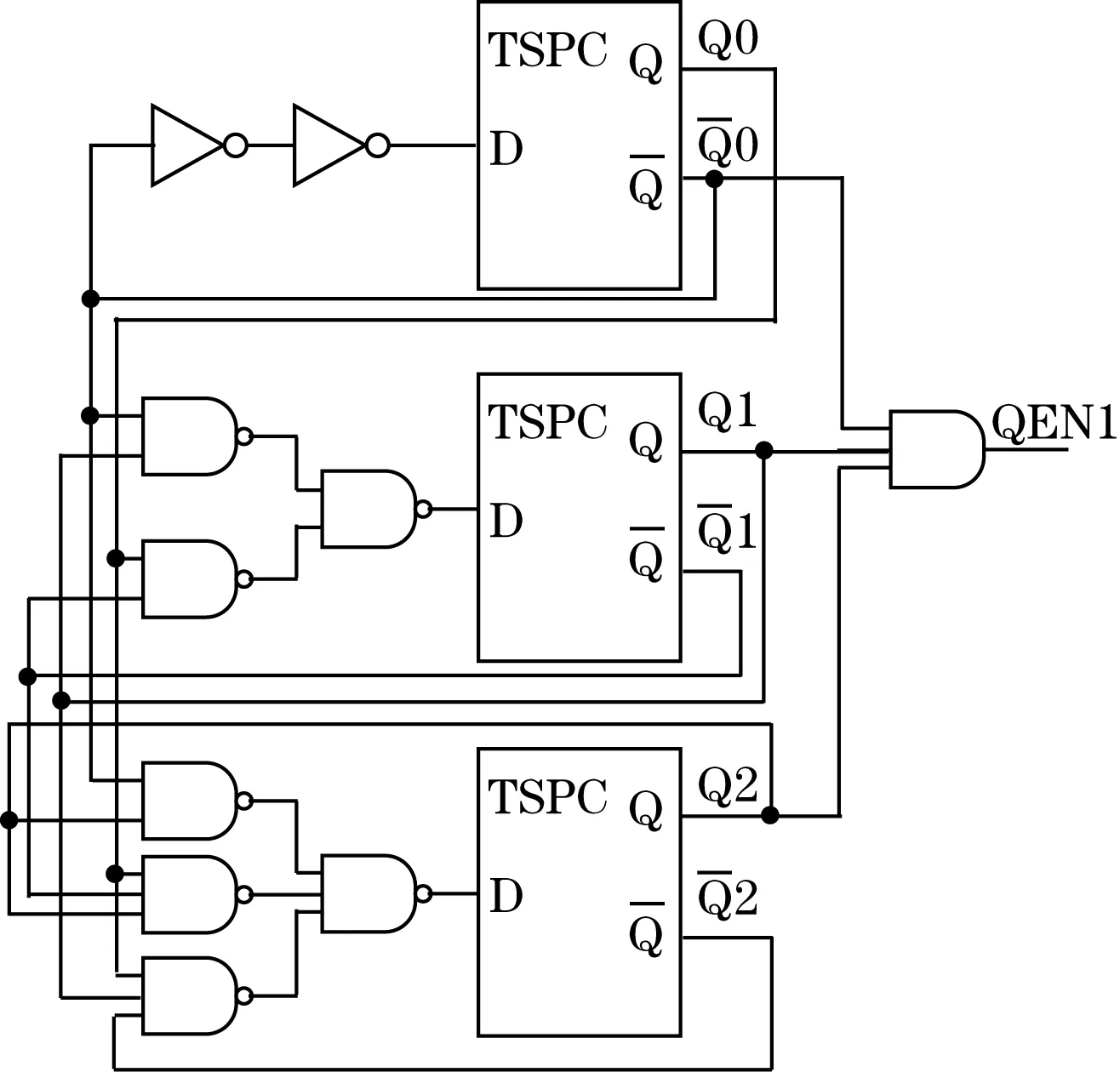

2.1 架构设计

本文提出的12位计数器的并行计数器架构如图3所示。主要结构包括SLA路径(虚线框内所有逻辑)和计数路径(在虚线框外的所有逻辑)[8],将计数器设计为单模式计数器,它通过固定的顺序排列一组预先指定的计数状态,其中计数状态依次表示计数器值。计数器被划分为统一的3位同步计数模块。使用来自SLA路径的激励,在状态转换之前的时钟周期上启用计数较高有效模块的状态转换。因此,所有计数模块在时钟下降沿同时转换到其下一个状态。该计数器共含有536个晶体管。

图3 具有SLA结构的12位并行计数器的功能框图

2.2 功能设计

计数路径的计数逻辑控制计数操作,SLA(state look ahead)路径的逻辑预测未来状态,从而为这些未来状态准备计数路径。图3显示了3种模块类型M1,M2_S(S=1,2,3),M3用于构造2条路径。模块M1和模块M2_S只存在计数路径中,均表示3位并行计数器,模块M2是正边沿触发的TSPC触发器,在两种路径中都存在。在计数路径中,每个M2之前都有一个关联的M3。M3有2个主要用途:生成与它们的有序位置相关联的所有计数器位;在随后的M2(更高的值)中启用(与来自SLA路径的激励相关联)未来状态。

(a)M1原理图

M3在计数路径中的位置对于计数器结构的新颖性至关重要。计算路径中的M3作为M1和M2_1以及后面的M2_S之间的通道 (见图3)。放置的M3通过消除冗长AND门的延迟和在大宽度并行计数器的大型AND门扇入和扇出,来增加计数器工作频率。因此,更高有效位的模块(M2_S)只是通过前一个M3和SLA逻辑来启用,而不是要求所有来自较低有效位模块的使能信号一起通过AND门。计数路径中的M3提供了一个用于触发M2_S的1-cycle循环的SLA机制,使M3对所有阶段保持恒定的延迟,所有M2在时钟上升沿并行计数。

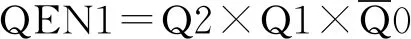

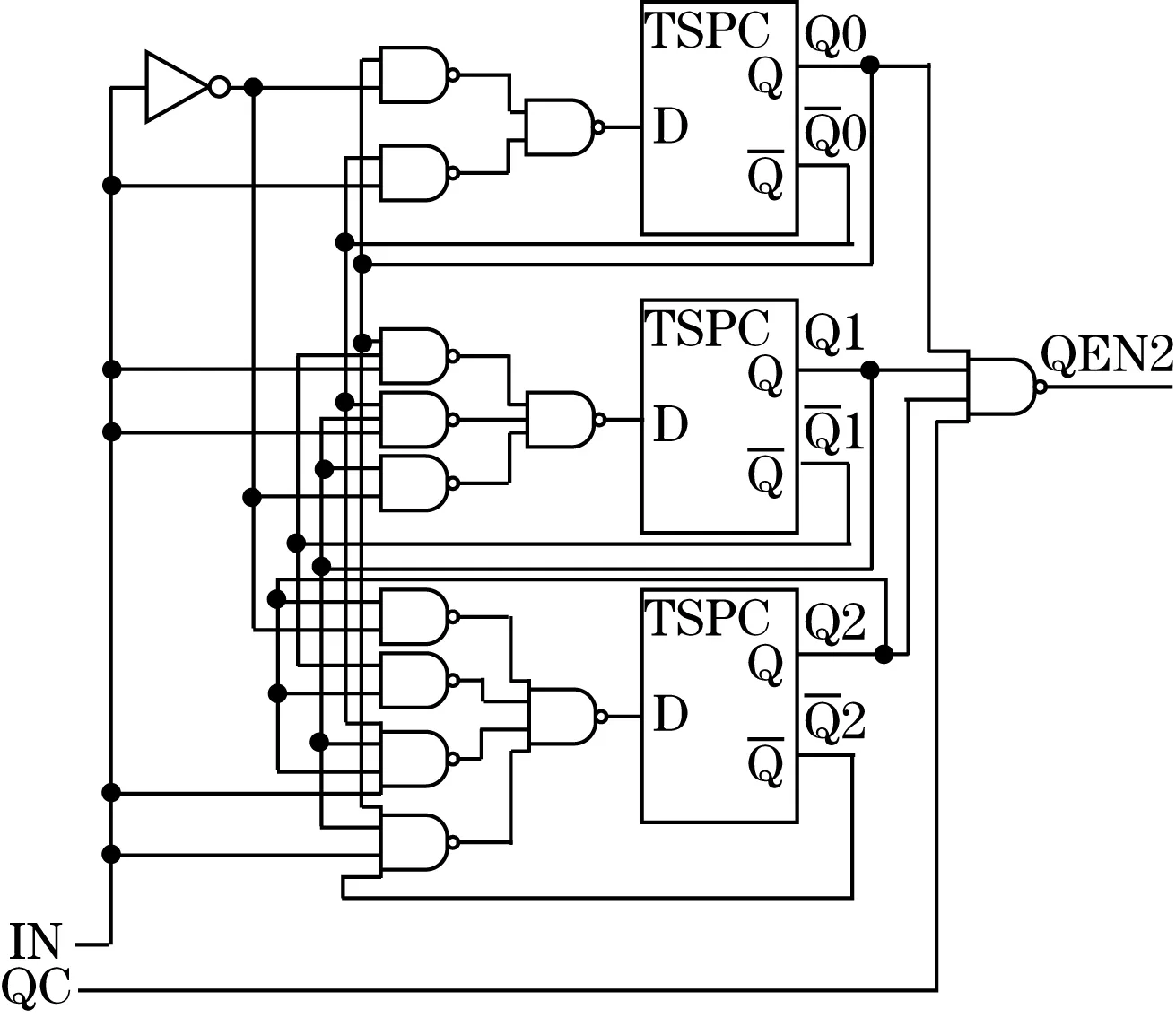

图5(a)为M2的硬件原理图,图5(b)为状态图,共含有117个晶体管。M2是一个并行同步二进制3位计数器,其计数由IN控制。IN连接到前面M3的输出Q。M2输出Q2,Q1和Q0,输出QEN2=Q2×Q1×Q0×QC。SLA逻辑提供QC输入,QEN2连接到后续M3的D输入,并提供单周期SLA机制。

(a)M2原理图

2.2.2 SLA路径

如图3所示,SLA路径的操作类似于进位预估加法器,因为它解码低阶计数状态,并在几个时钟周期内进行解码,以触发高阶计数状态。通过SLA路径中M3的时钟周期的早期溢出流水线操作,启用下一个状态的计数路径的高比特位。SLA逻辑等价于计数路径中的单周期SLA机制。这种SLA的逻辑组织和操作避免了使用额外延时检测电路,并对低阶模块进行解码,为高阶模块生成使能信号,并使所有模块在时钟上升沿同时触发,从而避免了毛刺和长延时。

3 时序图与延时分析

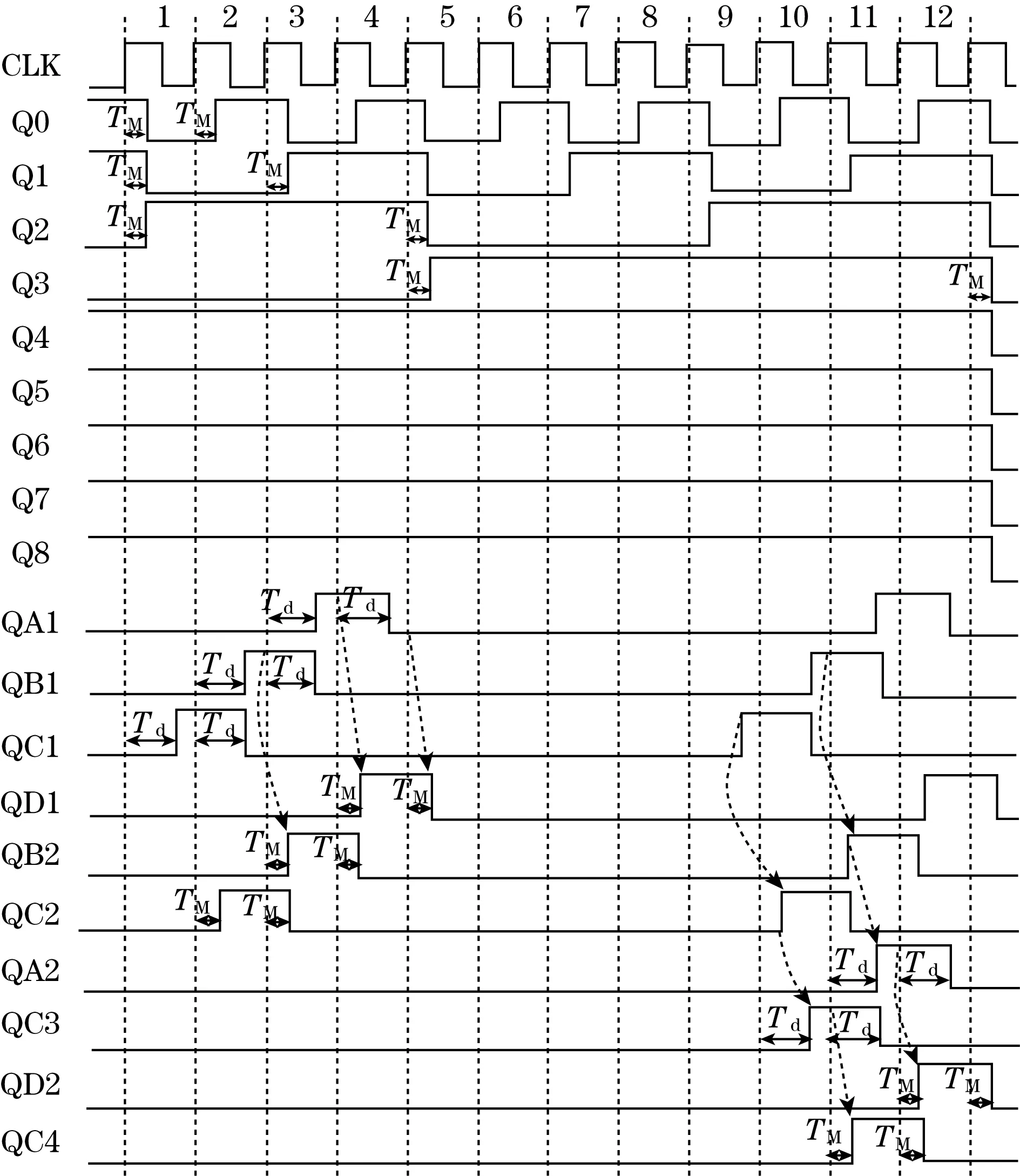

图6为图3中12位计数器的时序图,图6中的每个信号均在图3中表示出来,由于Q11Q10Q9跳变周期太长,因此只显示了前九位计数输出,开始计数状态为111110011(Q8~Q0),然后以111111111(Q8~Q0)计数状态结束的9个后续计数。假设所有模块的访问时间相等都为TM,AND门的单位延迟为TA,并且所有TSPC触发器都是正边缘触发的。

图6 时序图分析

在第1时钟周期的上升沿,经过TM的延时,计数状态更新为111110100。M1的Q2Q1Q0从011变为100,Q2Q1Q0的跳变触发了SLA路径的三输入AND门,经过Td(Td=TM+TA)的延迟,早期溢出检测信号QC1从0变为1。

在第2时钟周期的上升沿,经过TM的延时,计数状态更新为111110101。M1的Q2Q1Q0从100变为101,Q2Q1Q0的跳变触发了SLA路径的三输入AND门,经过Td(Td=TM+TA)的延迟,早期溢出检测信号QB1从0变为1。同时,SLA路径的QC2经过TM的延时从0变为1。流水线早期溢出检测信号在上一个时钟周期的QC1=1,而由于M1状态变化,QC1在Td的延迟后变为0。

又过了10分钟,门铃又响了。思雨打开门,这回真进来一位长发飘逸的美女。思雨急不可奈地拉着美女坐在床上,借着床头灯认真地看起她的头发。这位小姐的头发的确很美,在灯光下闪着栗红色的光泽。而且还飘出一股淡淡的香味,这大概是一种进口香水的味道。

在第3时钟周期的上升沿,经过TM的延时,计数状态更新为111110110.。经过Td的延时,Q2Q1Q0的变化触发了M1内的三输入AND门,使得QEN1=QA1=D=1(其中D为M1右边M3的输入)。同时,SLA路径的QB2经过TM的延时从0变为1,因此流水线早期溢出检测信号在上一个时钟周期的QB1=1,而由于M1状态变化,QB1在Td的延迟后变为0。

在第4时钟周期的上升沿,经过TM的延时,计数状态更新为111110111,M1的Q2Q1Q0从110变为111,计数路径上的QD1由0变为1,同时,由于M1的状态变化,计数路径上的QA1在Td的延迟后变为0。

第5时钟周期揭示了本文计数器的并行更新机制。在第5周期时钟边缘上升后,由于上个时钟周期QD1=1,根据图5的状态表,经过TM的延时,M2_1启动,计数状态更新到111111000。同时,由于上一周期QA1=0,因此QD1变为0。

第6到8个时钟周期,由于不涉及流水线早期溢出信号的跳变,因此不做分析。

在第9时钟周期的上升沿,经过TM延时,计数状态更新为111111100,Q2Q1Q0=100。Q2Q1Q0的跳变触发了SLA路径的三输入AND门,经过Td的延迟,QC1变为1。

在第10时钟周期的上升沿,经过TM延时,计数状态更新为111111101,M1的Q2Q1Q0=101,Q2Q1Q0的跳变触发了SLA路径的三输入AND门,经过Td的延迟,QB1=1。同时,SLA路径的QC2经过TM的延时从0变为1,此时Q5Q4Q3=111,因此经过Td的延迟,QC3=1。

在第11时钟周期的上升沿,经过TM延时,计数状态更新为111111110,经过Td的延时,Q2Q1Q0的变化触发了M1内的三输入AND门,使得QEN1=QA1=D=1(其中D为M2_1右边M3的输入)。同时,SLA路径的QB2经过TM的延时从0变为1,QB2=1作用于M2_1使得经过Td的延时,QA2=1。同时,上一个周期QC3=1,使得QC4经过TM的延时变为1。QB1和QC2在Td的延迟后变为0。

在第12时钟周期的上升沿,经过TM延时,计数状态更新为111111111,由于上一周期QA=1,因此QD1=1,同时QA1=QB2=QC4=0。同时,由于上一周期QA2=1,经过TM的延时,QD2=1,经过Td的延时,QA2=0。

4 电路设计验证

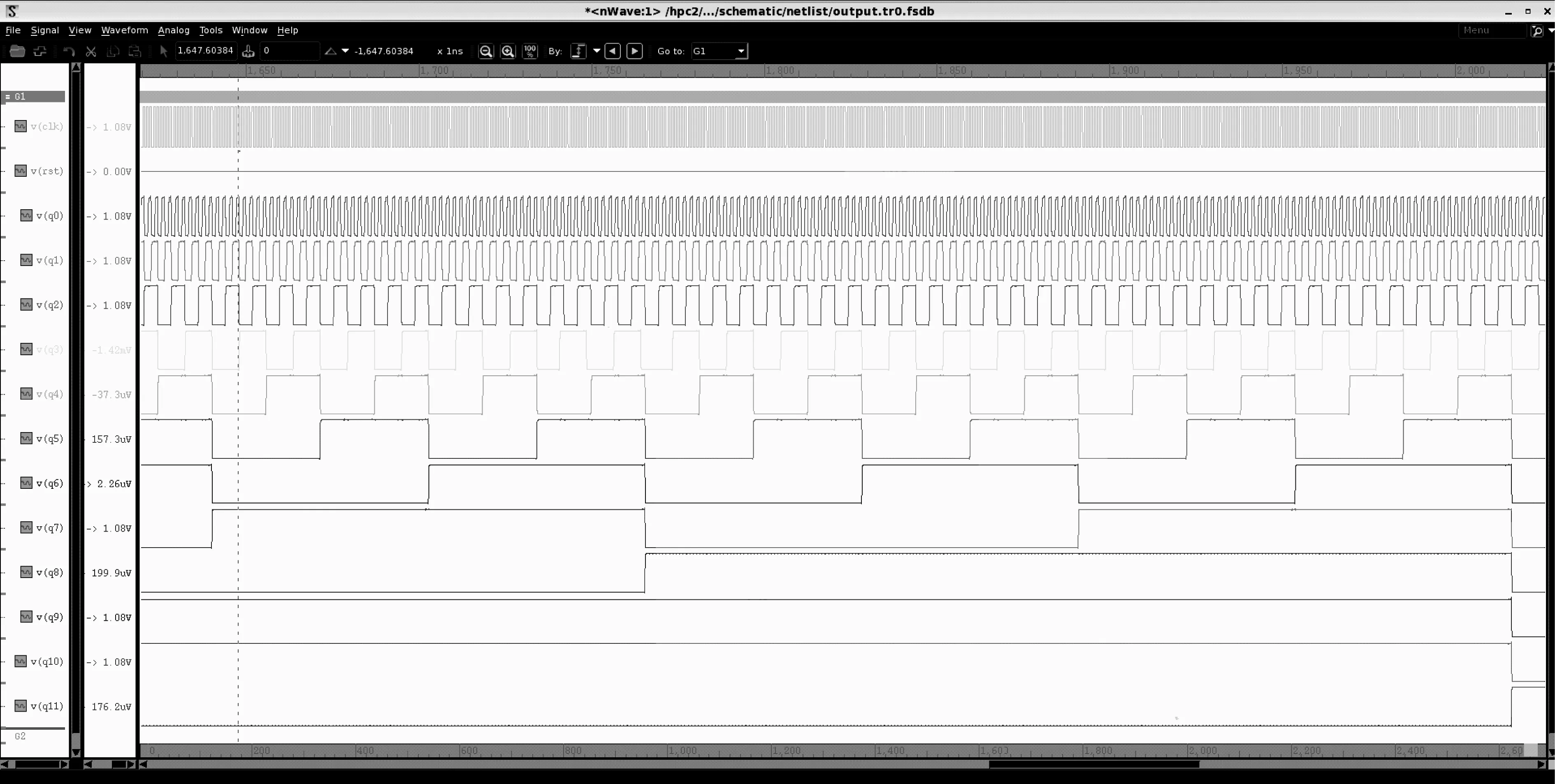

对于80 nm CMOS工艺的电路,正常工作条件是1.2 V和25 ℃,为了得到本设计的极限工作频率,在1.08 V和100 ℃条件下进行仿真。在Cadence Virtuoso中画出电路图后,生成电路网表,然后为了布局该并行计数器,使用了Perl脚本文件将寄生电阻和电容加入电路网表。采用HSPICE 80 nm CMOS技术在1.08 V和100 ℃下运行瞬态仿真,提供最坏情况下的工艺角。图7显示了使用Verdi波形查看器捕获的HSPICE仿真波形。HSPICE仿真结果显示了设计的12位并行计数器最高能达到1.03 GHz的工作频率,平均功耗为169.13 μW。

图7 12位并行计数器仿真波形

5 结束语

本文提出了一种基于数字CMOS门逻辑器件的12位高速并行计数器。计数器逻辑仅由3位并行计数模块,TSPC触发器和3个输入门组成。计数器结构的主要特性是流水线范式和SLA路径逻辑,它们的互操作在系统时钟边缘并发地激活所有模块,初始模块负责为更高位模块生成所有早期溢出状态,从而在完全相同的时间提供所有计数器状态值,产生均匀的频率延迟,而不会产生毛刺,计数器频率将显著提高。并且通过增加本设计计数路径的M2,M3和SLA路径中的M2的个数,可以构造12+3N(其中N≤4)位的宽长度的并行计数器。实验结果在80 nm CMOS工艺条件下,用HSPICE进行了1.08 V、100 ℃条件下的仿真。显示该工艺下极限工作频率为1.03 GHz,平均功耗为169.13 μW,达到了高频率、低功耗、性能稳定的要求。