关于74LS90计数器的Multisim仿真分析

2020-06-30张学文司佑全

张学文,司佑全

(湖北师范大学 物理与电子科学学院,湖北 黄石 435002)

0 前言

计数器是最常用的时序电路之一,它不仅可用于对脉冲进行计数,还可用于实现分频、定时、产生节拍脉冲以及其它时序信号[1]。常见的集成计数器为二进制和十进制计数器。在非二进制计数器中,最常用的是二-十进制计数器,74LS90是异步二-十进制计数器,利用其清零端或预置数端,外加适当的门电路就可以组成任意进制计数器。

本文用Multisim9对中规模集成芯片74LS90通过适当连接构成7进制计数器和15进制计数器进行仿真。

1 74LS90管脚及功能介绍

常用集成计数器分为二进制计数器(含同步、异步、加减和可逆)和非二进制计数器(含同步、异步、加减和可逆),74LS90计数器是一种中规模二-五-十进制异步计数器,管脚图如图1所示。

图1 74LS90管脚图

74LS90是异步二-五-十进制加法计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。通过不同的连接方式,74LS90可以实现四种不同的逻辑功能,而且还可借助R0(1)、R0(2)对计数器清零,借助S9(1)、S9(2)将计数器置9。其具体功能详述如下:

1)计数脉冲从CPA输入,QA作为输出端,为二进制计数器。

2)计数脉冲从CPB输入,QDQCQB作为输出端,为异步五进制加法计数器。(QD作为输出时,是十分频电路,占空比为20%,QC作为输出时,也是十分频电路,占空比为40%)

3)若将CPB和QA相连,计数脉冲由CPA输入,QD、QC、QB、QA作为输出端,则构成异步8421码十进制加法计数器。

4)若将CPA与QD相连,计数脉冲由CPB输入,QA、QD、QC、QB作为输出端,则构成异步5421码十进制加法计数器[2]。(QA作为输出时,是十分频电路,占空比为50%)

5)清零、置9功能。

a)异步清零

当R0(1)、R0(2)均为“1”;S9(1)、S9(2)中有“0”时,实现异步清零功能,即QDQCQBQA=0000.

b)置9功能

当S9(1)、S9(2)均为“1”;R0(1)、R0(2)中有“0”时,实现置9功能,即QDQCQBQA=1001.

应用N进制的集成计数器可以实现任意模值M(M

2 构成比模10小的7进制计数器

2.1 CPA端接输入脉冲信号

2.1.1 7进制计数器(清零法)

1)从0开始计数

输入端接入10Hz的时钟脉冲,输出端接入LED,通过观察LED灯亮暗的状态来观察实验的现象。输入端接入1kHz的时钟脉冲,输出接入四踪示波器观察输出端的时序波形。如图2所示。

(a)电路图

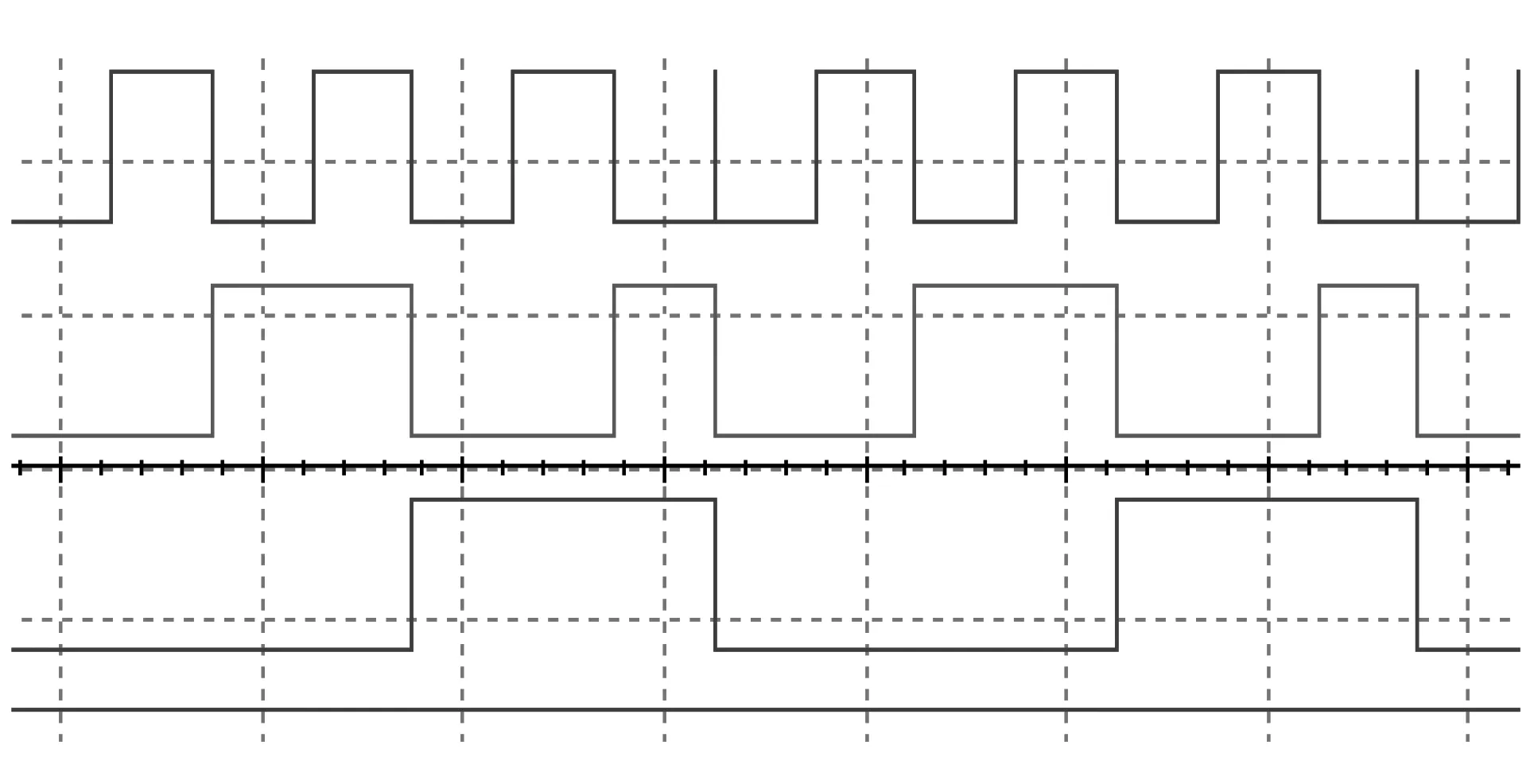

(b)时序图(从上至下依次为QAQBQCQD)

CPA端输入脉冲信号,CPB接QA端,2×5进制计数器,8421BCD码的10进制计数器,再用脉冲反馈法,令R0(1)=R0(2)=QCQBQA实现。第N(7)个CP脉冲后,由输出端的“1”去控制清零端。当计数器出现0111状态时,计数器迅速复位到0000状态,然后又开始从0000状态计数,从而实现0000~0110七进制计数。利用清零功能将0111、1000、1001这3个状态去掉。当QDQCQBQA=0111时,迅速复位到0000,然后又开始从0000状态计数。0111状态出现的时间极短,通常只有10ns左右,并不能看到。因而我们认为该电路是一个实现从0000-0110的七进制计数器[3]。由图2(b)可见,反馈清零法组成7进制计数器有一个瞬态。

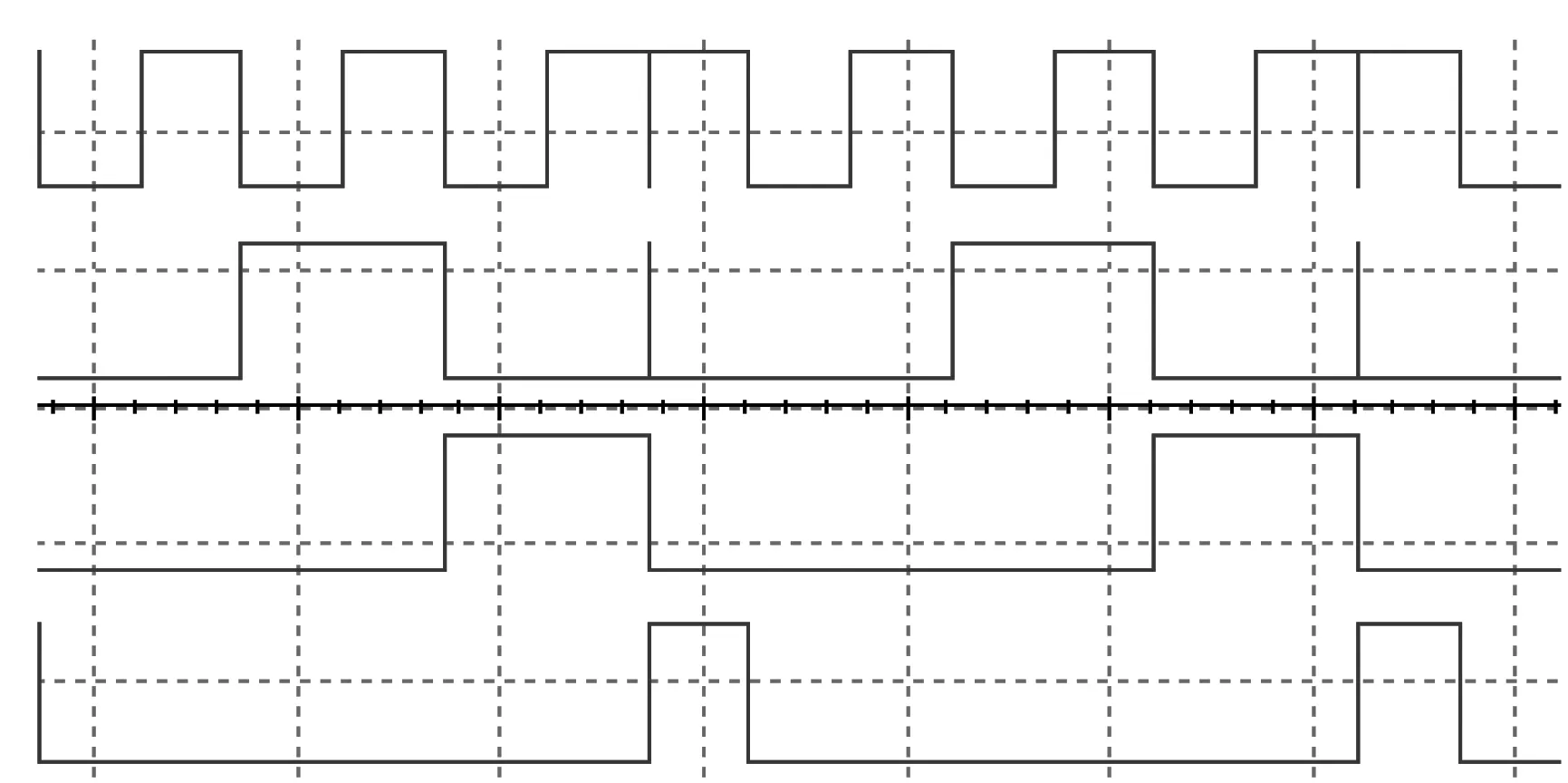

74LS90十进制计数器组成的7进制计数器, 用Multisim9仿真时出现了开机乱码现象, 电路在开始运行时,产生随机数,直到下一次脉冲信号到来,电路才从零开始计数,所以需要设计电路进行复位[4]。具体做法是增加上电清零功能,如图3(a)所示,在电路中加入清零开关和闭合开关,电路可在任意情况下清零;断开开关,计数器开始计数。确保7进制计数器电路能从0开始计数。

(a)电路图

(b)时序图(从上至下依次为QAQBQCQD)

2)从1开始计数

单片74LS90能实现十进制计数器(从0计数到9), 似乎可用其实现“9翻1”计数器, 但因9之后的第一个无效状态为0000,无为1的输出端, 而其又是加计数器, 无法获取反馈控制信号,故不能实现“9翻1”.74LS90并无置1端, 只有置9端和置0端,又该如何实现8以内的翻1?因为74LS90的十进制实际上是由其内部的二进制和五进制计数器级联实现的,若在二进制输出端加一个非门,同样还是一个二进制计数器, 这时再将改造后的二进制计数器的输出与其内部的五进制计数器级联,芯片的置0端,这时就转变为置1端。需注意的是,74LS10的输出应作为最低位, 而不是QA[5].如图4所示。

图4 7进制计数器(清零法)(8421 BCD码接法)从1开始计数

2.1.2 7进制计数器(异步置数法)

1)异步置数法7进制计数器(未加门电路)

(a)电路图

(b)时序图(从上至下依次为QAQBQCQD)

因为7的BCD代码为0111,所以只用两个复位0输入R0(1)、R0(2)来实现每7个输入脉冲的一次复位是不可能的,利用复位9输入R9(1)、R9(2)并使复位0输入R0(1)、R0(2)接地,QC、QB输出端分别接到R9(1)、R9(2)端(脚6、7)上,输出为0110时,QB=QC=1,S9(1)=S9(2)=1,置9(1001)。输出QDQCQBQA依次为0000→0001→0010→0011→0100→0101→1001之后再从0000开始循环[6~8]。

2)异步置数法7进制计数器(加门电路)

(a)电路图

(b)时序图(从上至下依次为QAQBQCQD)

异步置数法7进制计数器,当计数器QDQCQBQA为0110(6)时,立即产生“置9”信号,使R9(1)=R9(2)=1,将电路置成QDQCQBQA=1001,因此电路在0-1……5-9这七个状态之间循环,电路为7进制计数器。0110是过渡状态,0110、0111、1110、1111这4个状态是过渡状态[9]。

缺点0101→1001变化过程中转换时间过短。改进方法:在电路中加入一个RS触发器延长时间,使其正常(图7所示)。

图7 异步置数法7进制计数器改进电路

3)异步置数法7进制计数器改进电路

利用与门产生清零信号,此信号随着计数器清零而立即消失,持续时间极短,如果触发器的复位速度有快有慢,则可能动作慢的触发器还未来得及复0,清零信号已经消失,导致电路产生逻辑错误。因此,这种接法的电路可靠性不高。修正电路:反馈信号与清零端之间接一个基本RS触发器。既保证了在第7个计数脉冲下降沿到来时,R0(1)、R0(2)为高电平,亦提高了计数器置0复位时状态转换的速率。使得清0复位信号有足够的作用时间使计数器可靠地清“0”.

2.2 CPB端输入脉冲信号

2.2.1 CPA与QD相连,清零法

1)不接门电路

CPB端输入脉冲信号,CPA接QD端,5421码输出(QAQDQCQB),如图8所示。

(a)电路图

(b)时序图(从上至下依次为QBQCQDQA)

2)接门电路

从上至下依次为QBQCQDQA,在0,1,2,3,4,5,6之间循环,6(1001)之后出现了一个输出端有短暂的过渡态(“毛刺”), 这是异步清零产生的。

CPB端输入脉冲信号,CPA接QD端,5421码输出(QAQDQCQB),如图9所示。

(a)电路图

(b)时序图(从上至下依次为QBQCQDQA)

2.2.2 CPA与QD相连,7进制计数器(置数法) 因为7的BCD代码为0111,所以只用两个复位0输入R0(1)、R0(2)来实现每7个输入脉冲的一次复位是不可能的,但利用复位9输入R9(1)、R9(2),并使复位0输入R0(1)、R0(2)接地,QC、QB输出端分别接到R9(1)、R9(2)端(脚6、7)上,这时计数器就能对0、1、2、3、4、5、9、0…等等进行计数,由输出端QC或QD就可以得到非对称的7进制输出[6],如图10所示。

(a)电路图

(b)时序图(从上至下依次为QBQCQDQA)

2.2.3 CPA与QC相连,7进制计数器(清零法) 从上至下依次为QBQCQDQA,CPB端输入脉冲信号,CPA接QC端,5421码(QAQDQCQB), 在0-1-2-3-9-5-6-0这七个状态之间循环,电路为7进制计数器。6(1001)之后出现了一个输出端有短暂的过渡态(“毛刺”),这是异步清零产生的,如图11所示。

图11 7进制计数器(清零法)(CPA接QC端)

3 用74LS90实现模为15的计数器

用74LS90实现模为15的计数器,有两种方法。

1)方法一:反馈归零法(复位法)

2)方法二:级联法,M为15;15=3×5,用两片74LS90,一片实现3进制,一片实现5进制,再将两片进行级联即可。

3.1 反馈归零法15进制计数器

3.1.1 百进制计数器 用两片74LS90构成百进制计数器。每片74LS90芯片连接实现8421十进制输出,输出状态排列为QDQCQBQA输出值为0000~1001,构成十进制计数器。(74LS90 为下降沿触发,低位清零时,进位信号由“1”到“0”,使高位进位,不用外加其他电路。)用低位片的高位输出QD作为高位片时钟输入,即当低位片输出状态由1001回到0000时,让高位片时钟脉冲出现工作点(下降沿),则高位片同时计数一次。低位片计数一个周期,低位片QD发出进位信号,高位片计数一次,计数起点8421码为0000 0000,终点为1001 1001,转化为十进制后为00~99,实现百进制计数。如图12所示。

图12 百进制计数器

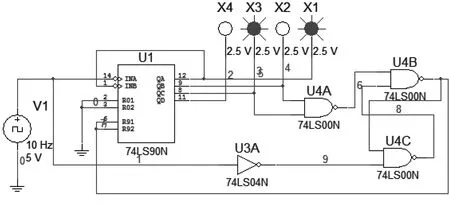

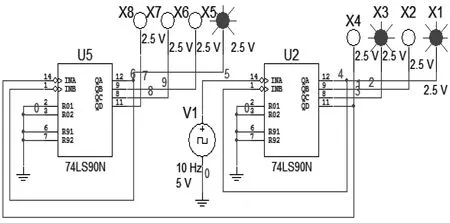

图13 15进制计数器(级联)(整体清零法构成15进制计数电路)

3.1.2 15进制计数器 两个74LS90组成百进制计数器之后,将状态“0001 0101”通过反馈与门输出至异步清零端,从而实现15进制计数器。如图13所示。

两个74LS90 芯片的清零端 R0(1)、R0(2)在出现15这个数时对其进行纳秒级的清零动作,所以查看计数过程中不会出现 15 这个数[10]。

个位片的R0(1)必须和十位片R0(1)连接在一起;个位片的R0(2)也要和十位片的R0(2)连接在一起;只有这么连接,才可能使两片74LS90同时清零。

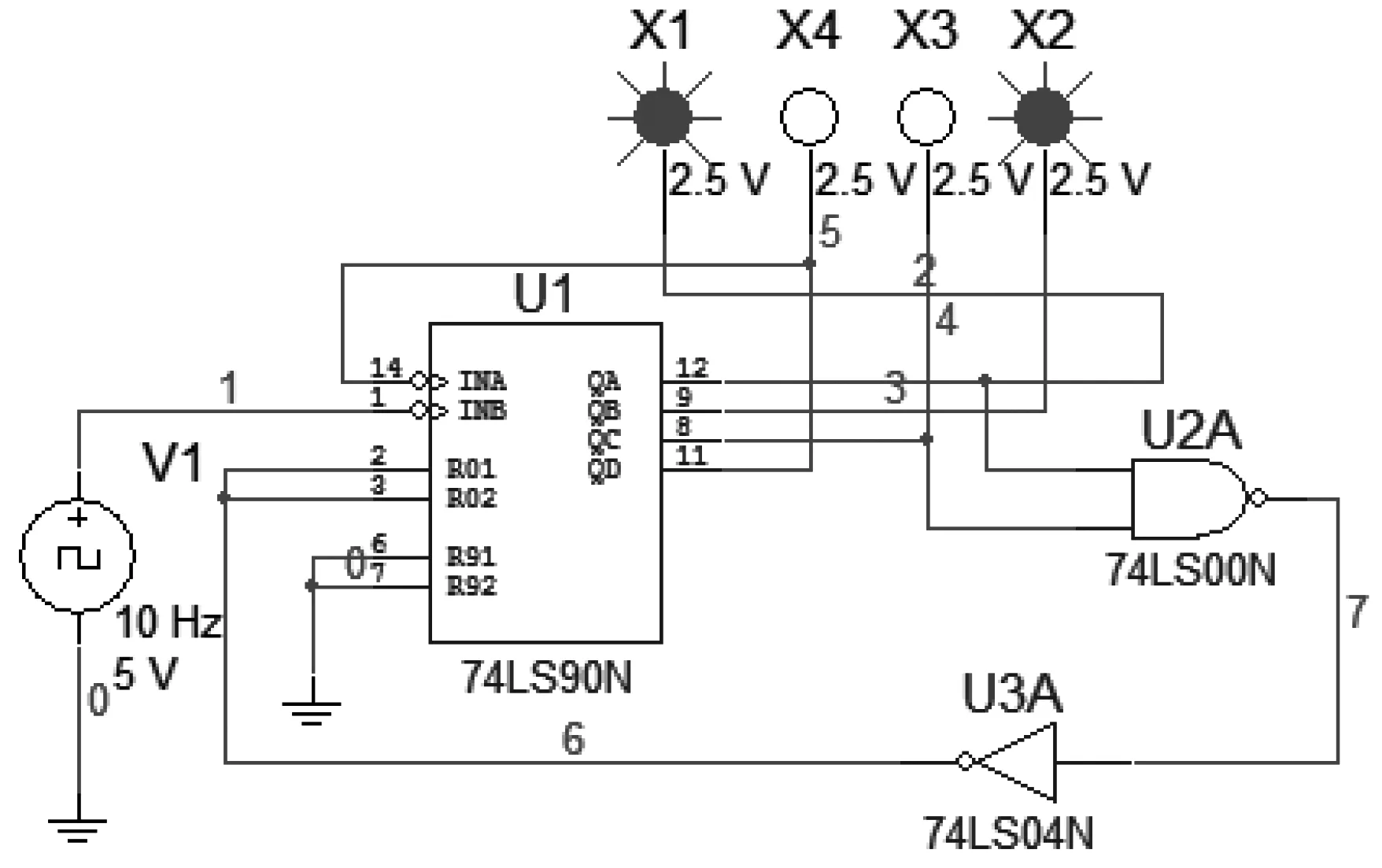

3.2 级联法15进制计数器

级联法,M为15;15=3×5,用两片74LS90,一片实现3进制,一片实现5进制,采用串行进位级联方式将两片级联起来。即将低位片计数器QC的输出信号作为高位片计数器的计数输入脉冲。

实际连接电路后发现图14电路为20进制计数器,而且0011、0111、1111这几个状态没有出现。

设计电路时,不能确定CP和QB哪个先改变状态,则不能正确确定电路的状态转换关系。要保证CP的下降沿在QB的新状态稳定后才到达,在QB到CP的传输通道增加延迟环节,使总的延迟时间足够长即可[11~12]。在图14电路中增加一个RC延时电路,如图15所示,0011、0111、1111这几个状态出现了,电路为20进制计数器,但还不是15进制计数器。

图14 15进制计数器(级联)

图15 15进制计数器(级联)(加RC延时)

改进电路如图16所示。将图16中X4、X3、X2、X1接4与非门74LS20的4个输入端后接非门74LS04之后再接入5进制的R01端。

图16 15进制计数器(级联)(改进电路)

4 总结

当7进制计数器BCD码中高电平的输出端不超过2个时,可以直接将其相应端接入74LS90的清零端或置数端,不需要另外接入门电路。

QD与CPA相连组成5421码进制外,QC与CPA相连同样可以组成5421码进制输出。

仿真中出现开机乱码,在电路中加入清零开关,闭合开关,电路可在任意情况下清零;断开开关,计数器开始计数。确保7进制计数器电路能从0开始计数。计数器漏跳时,可以加入RS触发器、增加RC延时电路来解决。

15进制级联时,按照电路原理,第一级3进制,第二级5进制,两级相连,分别清零即可。但实际电路需要将1111状态整体清零。

由此可见,使用集成计数器设计任意进制计数器时,需要结合芯片的功能表,并根据电路的实际应用场合采用合适的连接方式。利用Multisim9仿真软件进行分析,有助于直观地观察电路运行结果,利于及时发现错误,修改方便,便于验证,帮助熟练掌握任意进制计数器的设计方法。

实践证明,引入仿真验证环节,学生对任意进制计数器的分析和设计理解更加清晰透彻,该方法有效地提高了教学效果和质量[13~17]。