直接序列扩频伪码同步技术的研究与实现

2020-05-22张庆顺于凯张锁良

张庆顺,于凯,张锁良

(河北大学 电子信息工程学院,河北 保定 071002)

扩频通信是从军事通信中发展起来的一种高性能的通信技术,具有很强的抗窄带干扰、抗多径干扰能力,并且具有信息隐蔽、多址保密通信[1]等优点,在移动通信和卫星通信中得到了广泛的应用[2-3].在实际的直接序列扩频通信的信息接收过程中,由于受到由收发两端距离的不确定、晶振的不一致、收发两端时钟相位的不同、多普勒效应等引起的频率的不确定性的影响,所传递信息数据会在接收时产生失真现象[4].因此,为了准确的将发端信息恢复出来,伪码解扩的同步环节成为直接序列扩频通信中至关重要的一个环节.伪码的同步一般分为2个阶段,第1个阶段捕获伪码,即粗同步,在接收机刚开始工作时,在一定的频率和时间范围内搜索有用信号,通过调整伪码时钟使本地伪码与发端伪码的相位误差小于1个码元长度.第2个阶段跟踪伪码,即细同步,在初始达成同步条件的情况下,持续地对接收信息进行跟踪,并对本地的码相位进行校准,进一步减小收发2端伪码相位之间可能存在的相位差,与此同时,继续维持本地伪码与发端扩频码相位的同步状态.FPGA 器件具有速度快、密度高、功耗低、可配置性强等特点,并且可以简化系统设计、提高系统的稳定性和缩短开发周期,其最大的特点就是具有高度的灵活性,可以实现想实现的任何数字电路,也可以定制各种电路,而且它强大的逻辑资源和寄存器资源可以让设计师轻松的去发挥设计理念.由于其硬件实现的方式是并行执行的,因此可以应对设计中大量的高速电子线路设计需求.随着大规模集成电路、现场可编程器件的不断发展,可以利用大规模现场可编程器件来实现高度灵活的数字直接序列扩频接收机[5-6].针对直接序列扩频系统中实现扩频伪码同步的问题,本系统在延迟锁相环的基础上,结合滑动相关法理论来实现直接序列扩频系统伪码的同步算法,并基于 Xilinx 公司的 FPGA芯片加以具体实现.

1 理论分析

1.1 PN 伪码的捕获原理

扩频系统接收端信号可以表示为

(1)

式(1)中Pr是接收信号的功率,D(t)是信息码,PN(t)是伪码,n(t)是传输过程中的加性噪声,τd是码时钟延迟.扩频接收端的任务是去除伪码和载波,然后可以得到有效信息数据D(t).

在直接序列扩频系统接收端,伪码的同步技术基于伪码的高度自相关性,长度为N的m序列的自相关函数可以写为[5]

(2)

从方程(2)知道,当本地伪码与发端扩频伪码的相位偏差在1个码元宽度之内时,2者的相关性可以接近最大,同时接收端信号数据与本地伪码的相关运算会输出1个很大的峰值[7],它们的相位偏差越大,相关性越小,即相关值的大小反映了发端扩频码与本地伪码的对齐程度.

1.2 滑动相关法基本原理

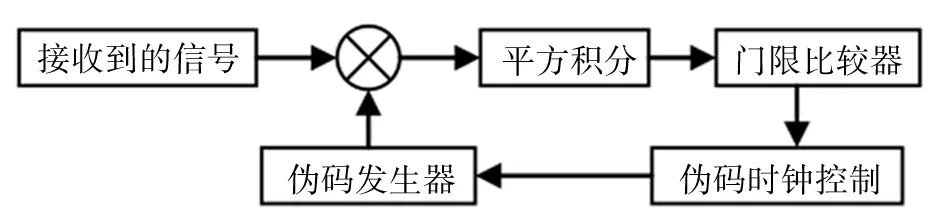

所谓滑动相关法,就是通过对本地伪码时钟的调整,使得本地伪码的相位较发端扩频伪码的相位有一个相对滑动的过程.在此过程中,接收到的信息数据和本地伪码进行相关运算.当本地扩频码和发端扩频码相位误差小于1个码元时,即相关累加器输出相关峰值且通过门限比较,表示完成了伪码的粗同步.滑动相关法实现过程如图 1 所示.接收到的信号经过相关处理、积分处理后,积分值给到门限比较器与门限值比较,高于门限值则送往跟踪模块处理,否则门限比较器输出一个信号到伪码时钟控制电路中以半个码元的步长改变本地伪码的相位,然后重新进行上述过程.滑动相关法是一种最简单、最实用的捕获方法.但当接收扩频码序列过长或者与本地伪码失配量很大时,滑动搜索时间可能很长,且解扩后系统的带宽越窄,捕获时间就越长.

图1 滑动相关法Fig.1 Sliding correlation method

1.3 延迟锁相环基本原理

当同步系统捕获到有用信号之后,即收发端扩频码序列相位相差在1个码元内时,伪码同步系统转入细同步阶段.当扩频通信系统受到外界因素而引起收发2端扩频码相位发生偏移时,伪码的细同步总能使收端扩频码跟踪发端扩频码的相位,从而来维持同步系统的稳定运行.因此,细同步的作用和反馈都是闭环运行的.当收发2端伪码相位产生误差时,跟踪环路总能根据收发2端扩频码的相位误差进行自动调节以缩小收发2端伪码序列之间的相位误差.因此,伪码的跟踪环路多采用延迟锁相技术.

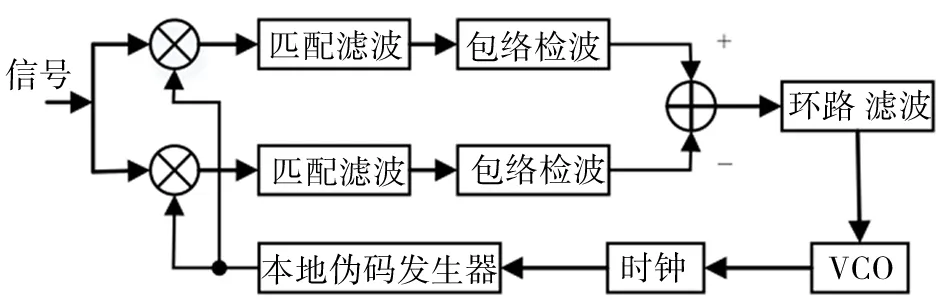

跟踪环路可分为相关和非相关2种.在实际的连续信号扩频通信系统中,常采用非相关延迟锁相环技术[8]来实现伪码的细同步.图 2 为一种基于 BPSK 调制的直扩系统扩频信号的非相关延迟锁相跟踪环,由2个并联的相关支路构成的锁相环路.系统接收到的信号分别和本地2路伪码进行相关运算,这2路本地伪码在相位上相差1个位.基于扩频伪码的相关特性,输入信号和本地扩频伪码的相关特性应为三角波.又由于2个相关支路的本地扩频码在相位上相差1个位,因此2个支路的三角波的峰值也会相差1位,如图 3 所示,在相关器输出波形以及合成波形中,可以观察到,如果收到的信号相对于本地伪码超前或者滞后,则相应加法器的输出就会为正电压或者负电压,然后此电压会通过环路滤波器去影响本地的压控振荡器(VCO),从而对产生本地伪码的码时钟进行控制,以调整本地伪码发生器产生的本地伪码相位[9],这就是延迟锁相环的基本工作原理.

图2 延迟锁相环Fig.2 Delayed phase locked loop

a.相关器1的相关波形;b.相关器2的相关波形;c.合成的相关波形.图3 相关器波形Fig.3 Correlator waveform

2 伪码同步的 FPGA 实现

通过以上原理,可以知道:滑动相关法可以使系统在开始工作的时候搜索有用信号,通过对本地伪码发生器时钟的调整,使本地伪码相对于接收信息有一个相对滑动的过程,当本地伪码与发端扩频码相位误差小于1个码元时,进行解扩输出处理,这就实现了对伪码的粗同步.而当同步系统捕获到有效信息之后,延迟锁相环可以根据超前-滞后信号相位的信息,使本地伪码在相位上做一个超前或滞后的调整,从而达到本地伪码跟踪发端扩频码相位的目的.

延迟锁相环不仅能起到跟踪的作用,如果结合滑动相关法的概念,使本地伪码相对于接收信号产生一定的滑动,也能起到对扩频伪码进行捕获的作用[3].基于这一想法,在本系统中,结合滑动相关法理论,基于延迟锁相环直接来实现直接序列扩频系统中伪码的同步.伪码同步原理如图 4 所示.

图4 基于延迟锁相环的伪码同步系统Fig.4 Pseudo-code synchronization system based on delay phase-locked loop

通常,在实际同步系统的实现过程中,为了提高系统的捕获性能,采用 I、Q 2路来实现扩频伪码的同步算法.首先,将系统的接收端收到信号通过正交、同相处理将信号分成 I、Q 2路,然后通过匹配滤波器,将高频噪声滤掉,为了减少系统的运算量,取信号的高4位数据,并将高4位数据存于移位寄存器之中.由于伪码的跟踪需要产生3路信号,因此使用低倍的时钟分别对 I、Q 2路信号进行3路采样,第1路相当于超前路,第2路相当于即时路,第3路相当于滞后路[10].最后,6路采样信号分别与事先存好的本地伪码进行相关运算.

在做相关运算时,不再滑动本地伪码,而是从事先存好的本地伪码存储器中直接读取进行相关运算.I、Q 2路中的即时路信号的相关值用于伪码的捕获,它们的平方和作为幅度值,送给门限判决模块进行门限判决.当某次采样后,其平方和大于设定的门限值的时候,表明伪码捕获成功,输出解扩结果,并输出捕获成功信号使系统进入伪码跟踪的状态.否则,基于滑动相关法的理念以及采样频率与信号频率不同的处理方式,在下一时刻继续对移位寄存器相同的地址位置进行重新采样,直到2个即时路的相关值的平方和大于所设置的门限值,即捕获成功.

I、Q 2路中的超前、滞后4路信号的相关值用于伪码的跟踪.当同步系统收到捕获成功信号之后,伪码的同步系统进入跟踪阶段.此时相位误差提取模块就会根据其超前、滞后4路信号的相关值来得到相位误差,来重新确定对移位寄存器采样的地址位置,这就会使发端扩频码与本地扩频码产生了码相位差,从而使本地伪码的相位较发端扩频码相位产生相对滑动,并使相关峰不断趋近于最大值并且维持此状态,从而达到伪码跟踪的目的.

3 同步系统的模块介绍

3.1 数据存储器

数据存储单元由移位寄存器构成,在系统时钟驱动下,接收信号按地址顺序存于移位寄存器中.读取移位寄存器数据的时钟是做相关运算的计算时钟,在此速率不是很快的时候,读取数据宽度也可以扩展为接收数据宽度的整数倍,一次读取多个接收数据参与相关运算,这样串行运算变为了并行运算,极大提高了数据的处理速度[11].

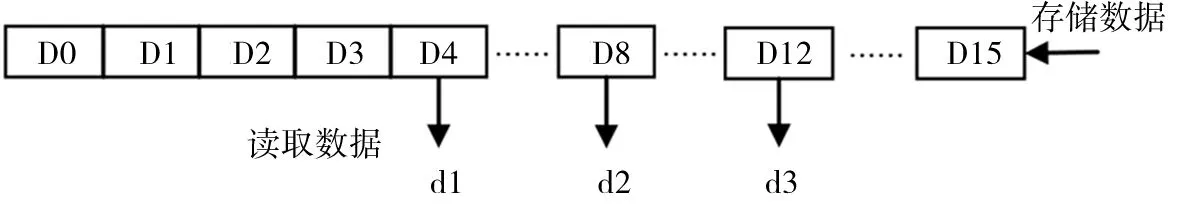

在此系统实现方案中,为了减小系统处理数据的复杂度,在接收信号中截取了带一个符号位的高4位数据,然后将数据存储于移位寄存器之中.由于本地伪码的时钟为 10 MHz,发端采样后数据频率是 80 MHz,所以存储数据的时钟频率设置为 80 MHz,采样时钟设置为10 MHz.如图 5 所示,将所截取数据按从 D0 到 D15 的顺序存储于移位寄存器之中,每次间隔地读取3个移位寄存器地址的数据.由于采样时钟频率是数据存储时钟频率的1/8,则每经过8个采样时钟就对移位寄存器的3个地址位置采样1次,采样数据与本地 PN码进行并行的相关运算.采样系统开始工作时,对 D4、D8、D12 持续进行采样,直到捕获成功.系统转入跟踪状态后,采样的地址位置才会根据跟踪信号进行重新调整.

图 5 采样原理Fig.5 Sampling schematic

3.2 相关运算

为了得到用于伪码捕获以及跟踪阶段的相关峰值,相关运算模块对接收数据与本地 PN码采用非相干的方法.接收到的6路采样数据首先和事先存好的本地伪码对应位进行相乘相加,然后再对累加结果求平方和作为输出峰值,最后将即时路的相关峰值送与门限判决模块与设置好的门限值比较,如果相关峰值和大于所设置的门限值,则输出解扩结果,否则继续进行捕获步骤的操作.

3.3 相位误差提取

通常在伪码跟踪的时候,将接收数据和本地伪码的相关运算结果送与码鉴相器,鉴相误差通过环路滤波器控制 VCO 来调整伪码发生器,从而达到本地伪码跟踪发端扩频码变化的目的.

对于深深淹没在随机高斯白噪声中的伪随机序列信号的相位,可以通过采用相干的中频累积法来快速提取[12].因此在本系统跟踪的实现过程中,当捕获到有用信号之后,跟踪系统会通过 I、Q 2路的超前、滞后4路信号的相关值的数值大小来对移位寄存器的采样位置进行重新调整,即改变信号的采样位置,使本地伪码相位较发端扩频码相位产生了相对移动,从而使相关峰不断地趋近最大值,并且维持这种状态.使本地伪码相位较发端扩频码相位产生相对滑动的过程中,系统省去了复杂的码鉴相器、压控振荡器等控制模块,减少了系统的反馈时间,这将对系统跟踪性能的提高有所帮助.

3.4 门限值设置

门限值的设置可以通过多次测试由经验值得出.由于伪码序列具有很好的自相关特性,当本地伪码与发端频码相位误差在1个码元之内时,相关峰值会明显大于其他时刻,并且误差越小峰值越大.在实际应用场合中由于噪声大小不同,峰值也不是固定值,因此要根据具体情况进行仿真设定一个比较合适的门限值.门限值过大会引发漏警现象,而过小会引发虚警现象.在实际的操作系统中,一般通过多次测试,把门限值设置稍大有利于系统正常稳定的工作.

4 仿真结果与分析

基于以上所介绍的相关原理,本系统以 FPGA 为硬件控制平台,使用 Verilog 硬件描述语言在 Xilinx 公司 Vivado 2017.3 软件开发平台上实现直接序列扩频系统伪码的同步技术.通过对伪码同步系统的仿真测试,验证了基于延迟锁相环的伪码同步方法的可行性.

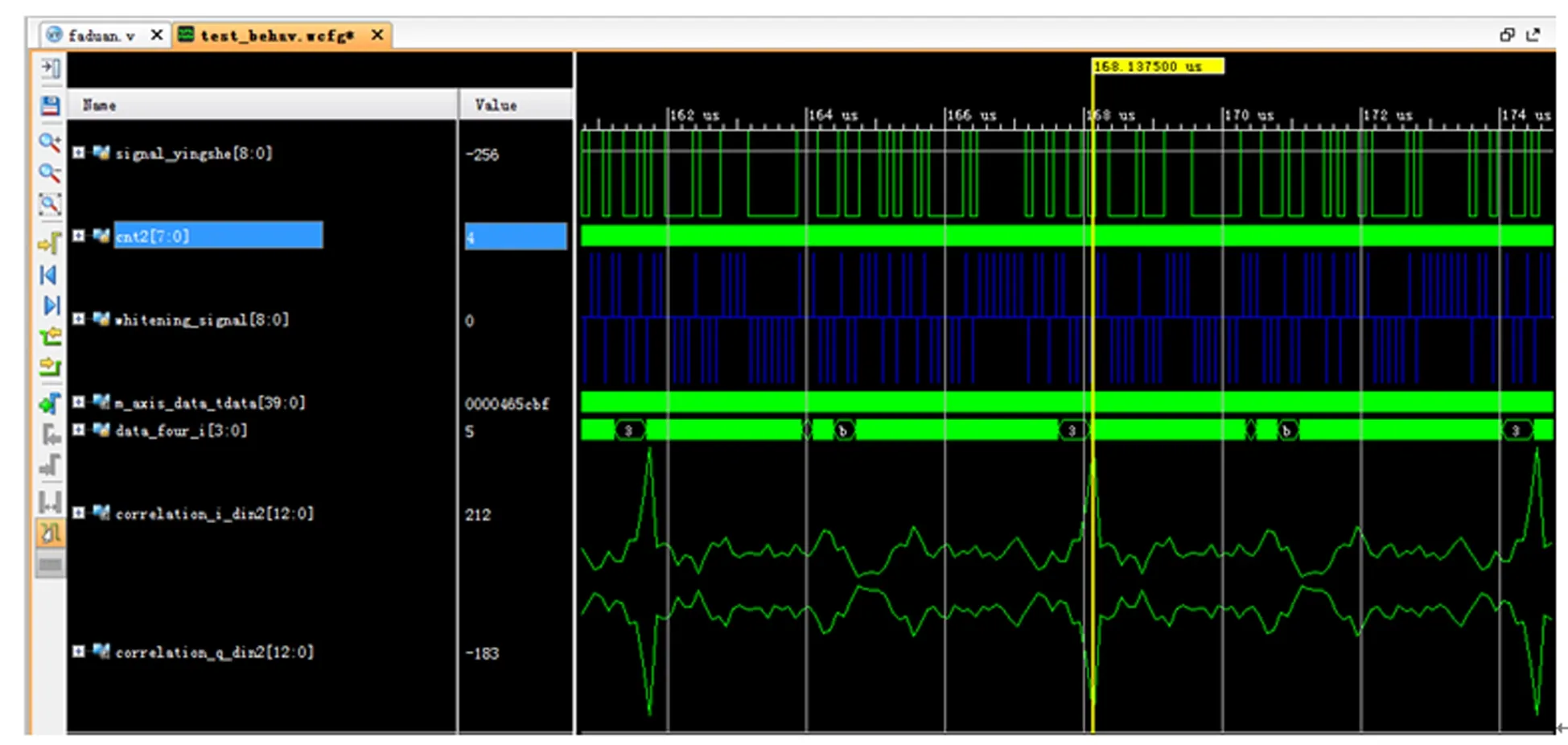

在本文实现伪码同步的过程中,采用对接收数据进行采样的方式代替常规的滑动相关法.对 I 路数据来说,首先将所取的高4位数据进行存储,共存储 16 个数据,以供采样位置的调整.如图 6 中 d0、d4、d8 所示,分别为移位寄存器里 D4、D8 和 D12 的数据,然后对移位寄存器中的数据进行3路采样,如图 6 中 dout1、dout2、dout3 所示,dout2 为即时路,dout1相当于超前支路,dout3 相当于滞后支路.

图6 3路采样输出Fig.6 Three channel sampling output

4.1 伪码的捕获

伪码同步算法首先就是进行伪码的捕获.通过采用低倍的时钟对移位寄存器进行不断的读取信号数据,从而来搜索相位,即时路的采样数据如图 6 中 dout2 所示,当本地伪码与发端扩频码的相位误差小于1个码元时,相关运算的结果输出相关峰,则表明捕获到了有用信号.I、Q 2路即时路的相关输出如图 7 中信号 correlation_i_din2 和 correlation_q_din2 所示.由于扩频伪码序列具有良好的自相关特性,当发端扩频码与本地伪码的相位相差小于1个码元时,即时路的相关输出峰值大小会明显大于其他时刻,这为门限判决输出的稳定性提供了可靠的基础.

在进行捕获门限判决的时候,计算出 I、Q 2路中即时路相关输出的平方和,如式 3所示,sum 作为相关峰给到门限判决模块,进行判决输出.由于相关峰为2路即时路相关输出的平方和,其相关峰值会远远高于未捕获时刻.如果再对判决门限值进行合理的设置,系统就会明显降低捕获虚警和漏警现象.

sum=(correlation_i_din2)2+(correlation_q_din2)2.

(3)

图7 I、Q 即时路的相关输出Fig.7 I,Q real-time related output

4.2 伪码的跟踪

由于伪码的捕获和跟踪都在延迟锁相环中完成,每当捕获系统输出一个相关峰的时候,捕获系统会输出一个捕获信号 capture,迅速使系统进入伪码的跟踪状态.系统跟踪信号如图 8 所示,当跟踪系统检测到 capture 为 1 时,相位误差提取模块就会对超前-滞后4路中频累积的结果进行计算比较,判断最大相关峰位置的方向.图8中信号 data_e 就是根据此原理变化的,并且根据信号 data_e 的变化,移位寄存器的采样地址位置开始被调整.当 data_e数值加1的时候,3路采样位置同时向右平移1位,当 data_e 数值减1的时候,3路采样位置同时向左平移1位,否则,3路采样位置的不变.在此状态下,系统通过对移位寄存器采样位置的调整,不断地缩小本地扩频码与发端扩频码相位之间可能存在的误差,使相关峰达到最大值并且维持此状态,从而使本地伪码牢牢地跟踪发端扩频码相位的变化.这样,就完成了伪码的跟踪.

图8 跟踪信号Fig.8 Tracking signal

5 总结

本文对伪码的捕获原理、滑动相关法理论、延迟锁相环理论以及同步系统的重要模块进行了详细的介绍.基于 Xilinx 公司的 FPGA 芯片,本文结合滑动相关法的概念,实现了基于延迟锁相环技术的扩频伪码的同步,并在实现过程中运用了多种机制改进了伪码捕获及伪码跟踪环节的部分实现方式.测试结果表明,此系统能够有效地实现伪码的捕获以及伪码的跟踪.本文中只涉及了实现伪码同步方法的可行性,在今后研究中将对其性能做进一步的测试.