高压直流输电控制系统不同锁相环特性对比

2021-09-24刘静佳李欢于华龙魏伟张海棠黄松强龚英明王子民傅闯

刘静佳,李欢,于华龙,魏伟,张海棠,黄松强,龚英明,王子民,傅闯

(1. 直流输电技术国家重点实验室(南方电网科学研究院),广州510663;2. 中国南方电网有限责任公司,广州510663)

0 引言

目前国内在运常规直流输电线路有30多条,直流输电已成为影响中国大电网安全稳定运行的关键因素。这些直流工程中,常规直流输电工程的阀控系统均采用以锁相环为基础的等间隔触发方式,尽管其不主动控制直流系统,但其作为直流控制系统的基础,直接影响控制系统的控制效果。而阀控系统触发以锁相环为基础,其控制效果严重依赖于锁相环对交流电压的相位跟踪能力[1-3]。

基于αβ坐标变换的传统锁相环(αβ-PLL),因结构简单、易于实现、在系统对称工况下的锁相性能较好而被广泛应用于高压直流输电工程中。但当电网电压不平衡或畸变时其锁相精度下降[4]。通过调整PI参数[5]或在其内部引入低通滤波器[6]来降低带宽,可以减小谐波分量对锁相同步过程的影响,但其动态响应速度会随之降低。而近年来众多文献研究了各种新型锁相环,基于复系数滤波器[7]、自适应陷波器[8]的锁相环能解决电网三相电压不平衡下的锁相问题,但在谐波含量较大时锁相的性能较差。基于滑动平均滤波法[9]、级联延迟信号消除法[10]、并联延迟信号消去法[11]的锁相环均因滤波而导致动态响应变慢。

文献[1]提出的基于广义二阶积分器的单相锁相环(single-PLL),具有较强的谐波和负序电流抑制能力,其与分相触发控制结合,能够在三相不对称工况下减小常规直流各阀实际触发角的差异,控制灵活,可有效降低交流故障恢复过程发生后续换相失败的概率。文献[4]指出采用MDSC前置滤波器的新型锁相环(MDSC-PLL)具有更宽的频率适应性,在各种故障工况下均能快速准确锁定相位,且能有效降低高压直流输电系统发生后续换相失败的机率。但各文献仅局限于其所提锁相环之优点,缺乏各种锁相环间的横向对比数据。

鉴于文献[1]所提新型单相锁相环和文献[4]所提新型三相锁相环均有降低高压直流输电系统换相失败机率的优势,本文对比分析传统基于αβ坐标变换锁相环(αβ-PLL)、基于SOGI-QSG的新单相锁相环(single-PLL)、基于MDSC前置滤波器的新型三相锁相环(MDSC-PLL)3种锁相环的优缺点,及对常规高压直流输电控制系统的影响,通过RTDS验证3种锁相环在各种典型工况下的响应特征,对比分析各锁相环在抗谐波、抗负序、宽频率适应性、交流故障穿越方面的优越性。

1 锁相环在高压直流输电系统中的应用

常规直流换流站大多采用整流侧控制直流电流、逆变侧控制直流电压的控制策略,两侧设置相同的控制器但配置不同的控制参数,输出不同的触发角,实现两侧协调运行。两侧阀控系统在触发相位控制作用下,根据各自的触发角和换相电压波形确定换流阀的开通时刻,完成控制任务。

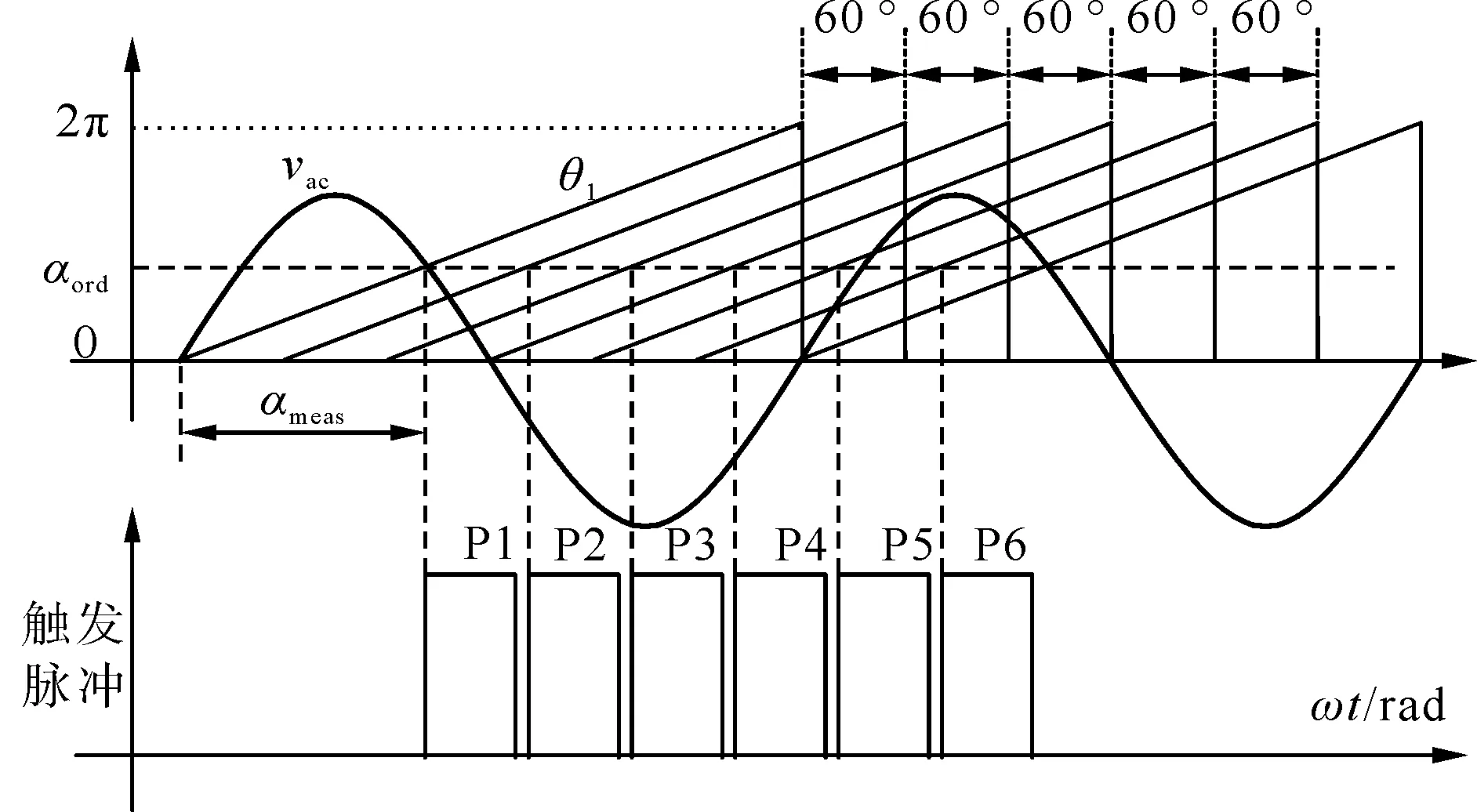

目前世界上在运常规直流输电工程均采用该触发控制技术,即等间隔触发控制。工程中采用的一种等间隔触发控制发法原理如图1所示,利用锁相环输出阀1换相电压Vac的同步相位θ,将该相位采用延迟的办法形成等相位间隔,并直接利用触发角指令和同步相位进行比较生成触发脉冲。

图1 等间隔触发控制原理图Fig.1 Control principle diagram of equal-inteval trigger

当锁相环精度不高时,实际触发角与触发角指令值不符,即αord≠αmeas,阀实际响应特征与控制期望不符,影响直流系统的稳定运行。二者偏差过大时,甚至会出现触发脉冲发出时,阀承受反向电压,不具备导通条件的极端工况。

当交流系统发生故障时,交流电压发生畸变,锁相环若不能快速跟踪相位,其输出的相位角将与实际相位角偏差很大。若在逆变侧,阀触发脉冲信号极易产生较大的故障延迟,导致即将关断的阀的关断时间过小,阀无法恢复阻断能力继而持续导通,最终造成换相失败。

由此可见,作为触发控制的关键因素,锁相环的锁相精度将直接影响触发脉冲的生成,进一步影响控制系统的控制效果。因此研究对比锁相环的锁相能力对保证直流输电控制系统稳定、提升直流输电控制系统故障应对能力至关重要。

2 锁相环数学模型

2.1 基于αβ坐标变换锁相环

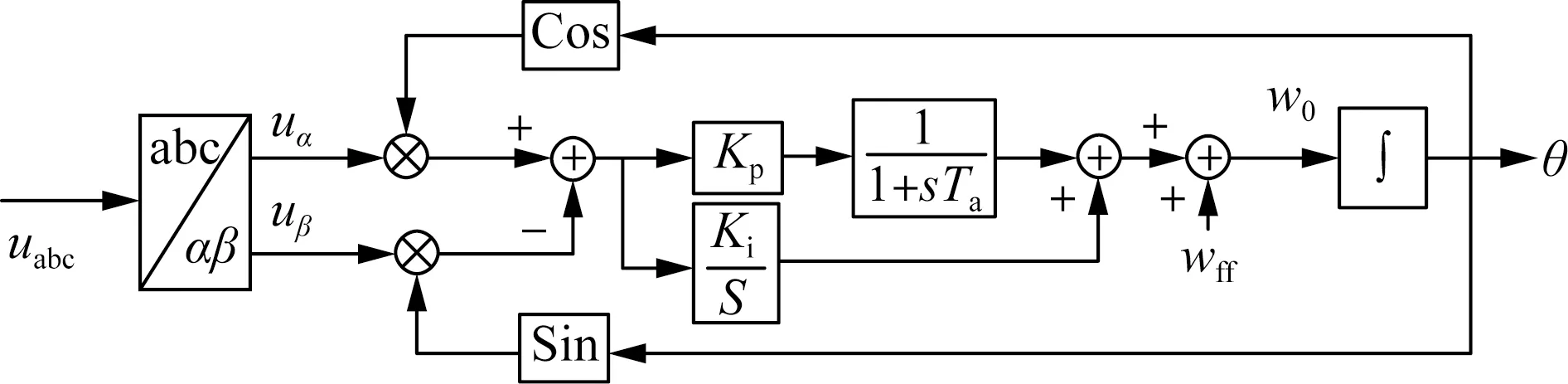

传统基于αβ坐标变换锁相环为高压直流输电系统中常用的锁相环之一,其工作原理如图2所示。

图2 基于αβ坐标变换的锁相环原理Fig.2 Principle of PLL based on αβ coordinate transformation

基于αβ坐标变换的锁相环采用Clark变换得到αβ坐标系下的电压分量uα和uβ,将uαcosθ-uβsinθ送入PI控制器,叠加计算步长对应的基波角频率值,经过积分器后得到电压相位θ,当输出相位θ与三相交流电压uabc相位α一致时,uαcosθ-uβsinθ为0,PI控制器停止调节,θ锁定跟随α。同时在比例环节后设置低通滤波环节,抑制谐波干扰。

该锁相环结构简单,易于实现,在系统对称工况下的锁相性能较好,正常情况下,PLL能准确跟踪基频正序电压分量的相位;但当输入的三相电压不平衡或发生畸变时,锁相环的跟踪性能会受到谐波的影响,通常将PLL的带宽设置得很小来减小谐波分量对锁相同步过程的影响,但会相应地降低其动态响应速度。

2.2 基于二阶广义积分器的单相锁相环

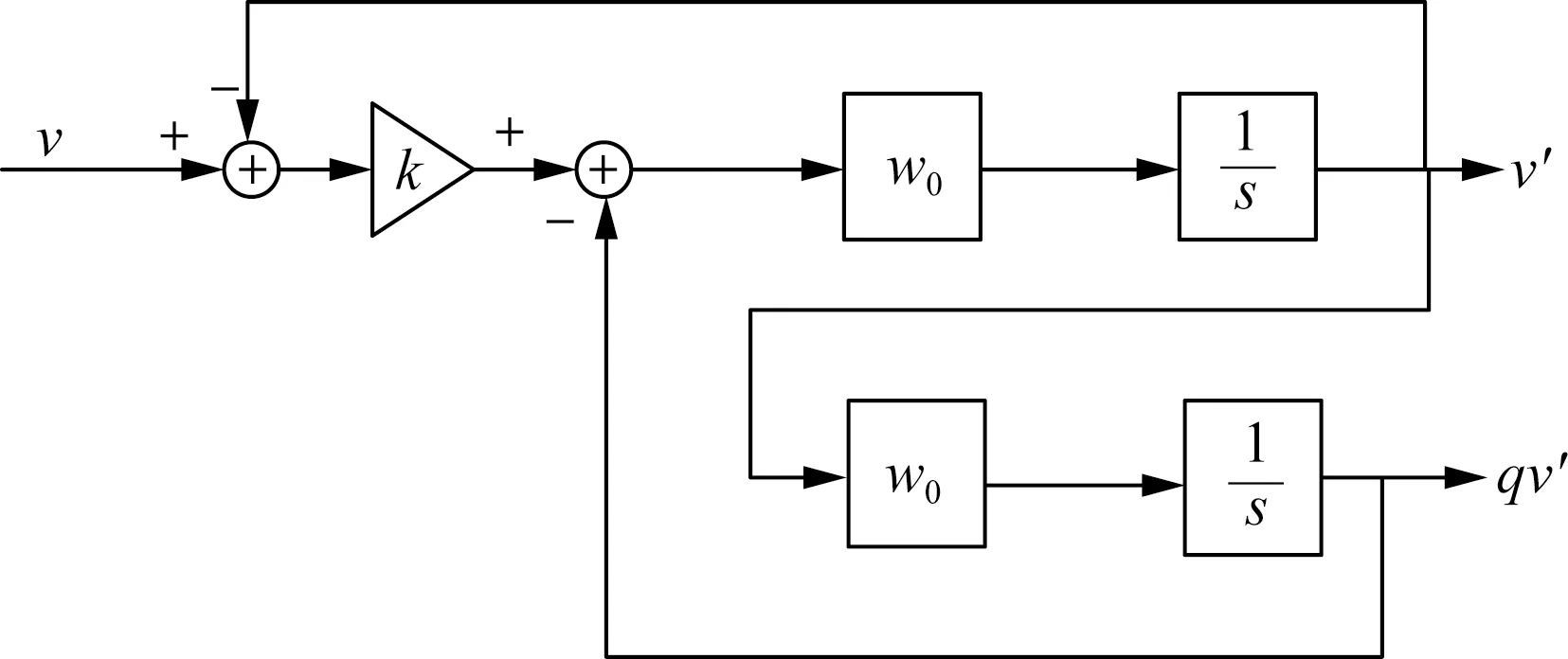

二阶广义积分器原理图如图3所示。

图3 SOGI-QSG原理图Fig.3 Principle diagram of SOGI-QSG

基于二阶广义积分器的单相锁相环原理如图4所示。

图4 基于SOGI-QSG的单相锁相环原理图Fig.4 Principle diagram of SPLL based on SOGI-QSG

二阶广义积分器中,输出信号v′可以实现对输入信号v中角频率为w0的正弦信号无静差跟踪,qv′总是滞后v′ 90 °。基于上述原理的单相锁相环以v′和qv′做αβ/dq变换,变换后的d轴分量进入PI得到相位,因v′仅含有v中角频率为w的正弦信号,因此锁相环滤波效果良好。同时当输入信号角频率ω与ω0不同时,锁相环输出的频率反馈至SOGI-QSG中,作为其谐振频率,可以实现频率自适应。

在常规直流输电系统中,SPLL与分相触发方案结合[1],即分别对换相电压Vac、Vba、Vcb进行锁相,将输出的相位θac、θba、θcb与触发角指令值进行比较,得到阀P1、P3、P5的触发脉冲,将输出的相位θac、θba、θcb延时180 °与触发角指令值进行比较,得到阀P4、P6、P2的触发脉冲。该触发方式较传统基于过零点检测的分相触发方式,触发参考相位更准确,不会直接受过零点波动的影响;与目前工程常用的等间隔触发方式相比,具有独立的触发相位控制电路,控制灵活,具有抗负序电压干扰、抗谐波干扰能力。

2.3 采用MDSC前置滤波器的新型三相锁相环

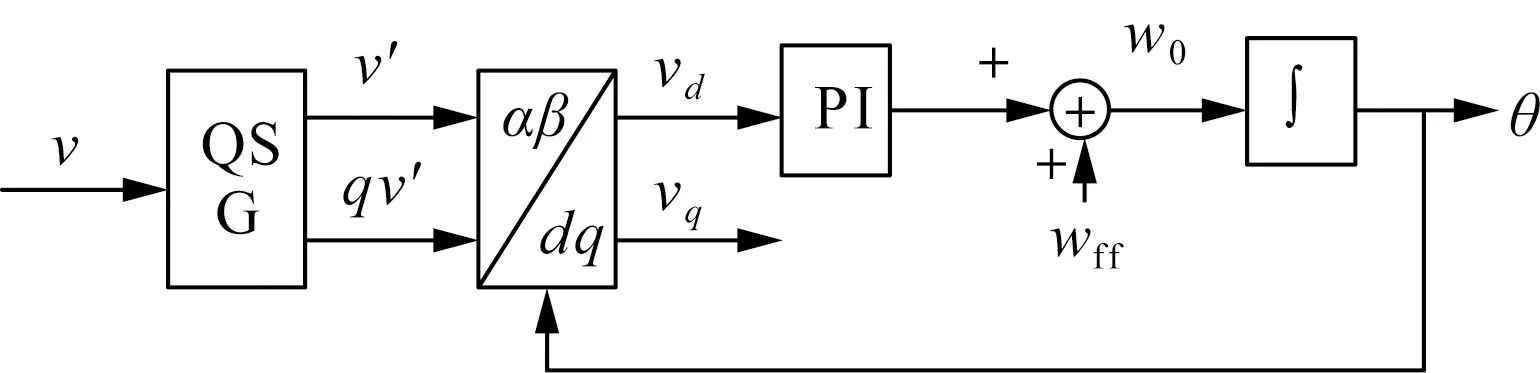

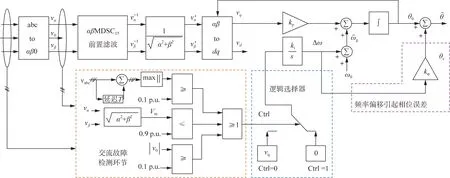

采用MDSC前置滤波器的新型三相锁相环原理如图5所示。

图5 采用MDSC滤波的锁相环原理图Fig.5 Principle diagram of PLL with MDSC filter

该新型三相锁相环在基于dq坐标变换锁相环基础上,增加了滤波、频率适应、故障处理环节,以抵抗谐波干扰、扩宽频率适应性、增强交流故障适应能力。

1)增加MDSC15前置滤波器,坐标变换后的αβ分量经滤波器提取纯净的基波正序分量,增加滤波功能的同时,又保证了动态响应的速度及稳定性。

2)增加频率偏移补偿,当电网频率发生偏移Δωg时,基波电压正序分量将产生-Δkφωg的相位偏移。因此将PI控制器积分环节的输出作为频率偏移量Δω,乘以kφ得到相位偏移量,将其补偿到锁相环输出的同步相位中去,保证锁相环在频率发生偏移时还能准确地跟踪电压相位。

3)增加故障检测环节,当发生故障时,通过逻辑选择器将PI控制器的积分环节的输入由vq变为0,使得锁相环输出的频率固定为故障之前的频率,实现了对锁相环相位检测和频率检测的解耦,加速PLL在故障暂态过程中对电压相位的锁定。

3 高压直流工程RTDS试验平台

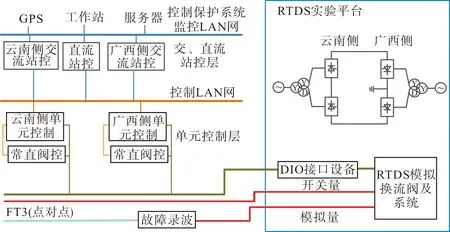

为横向对比上述3种锁相环的优缺点,方便各个工程因地制宜选择合适的锁相环,本文借助鲁西背靠背直流输电工程RTDS硬件闭环试验平台对上述3种锁相环进行测试分析。

试验平台的系统示意图如图6所示。

图6 RTDS闭环试验平台示意图Fig.6 Schematic diagram of RTDS closed-loop test platform

图中左框为控制保护装置,自上而下依次为监控层、交直流站控层、单元控制层。各装置全部采用高压直流输电系列装置—采用高性能多核DSP+大容量FPGA集成技术,满足高压直流输电系统对大量信号的高精度、快速处理需求。右框为RTDS仿真设备,在RTDS软件中搭建一次回路模型,接收控制保护装置发出的控制指令,完成主回路一次设备的模拟运算,并输送实时变量至控制保护装置和录波装置。其中一次回路参数如表1所示。

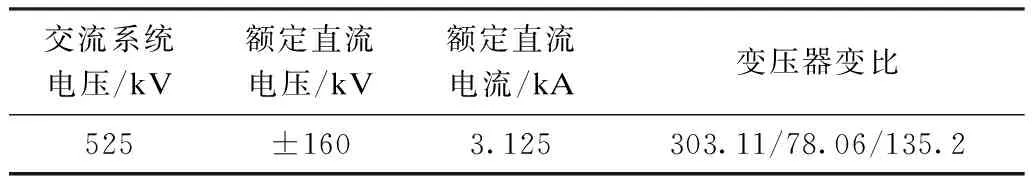

表1 RTDS测试平台参数Tab.1 Parameter of RTDS test platform

本文在上述测试平台上修改单元控制层装置中锁相环及阀触发逻辑涉及的DSP及FPGA程序,实现上述3种锁相环,在相同的工况下测试各个锁相环的锁相性能及其对控制系统的影响。

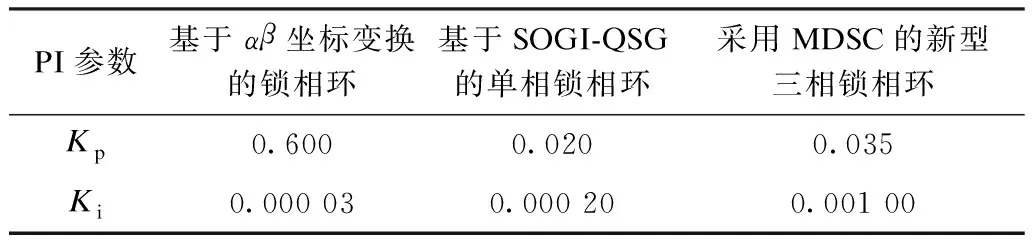

高压交流电网可能出现相位跳变、电压不平衡跌落、频率偏移、谐波以及电压负序分量等问题。因此,本文设计以下7种测试工况来考察新型锁相环的稳态和暂态性能。各个锁相环中均带有PI控制器,PI参数直接决定锁相环的动态和稳态响应性能。因此本文先在相同的交流电压相位阶跃工况下,调节各个锁相环的PI参数,以达到基本相同的动态响应性能,并在该参数下进行后续工况测试,最终各个锁相环PI参数如表2所示。

表2 各个锁相环PI参数表Tab.2 PI Parameter of PLLs

4 锁相环RTDS测试分析

4.1 交流电压相位阶跃测试

在满功率运行时,在RTDS上更改广西侧交流电压初始相位值由0 °突变为90 °,测试波形如图7所示。

图7 交流电压相位阶跃测试波形Fig.7 Test waveforms during AC-voltage phase mutation

图中可见,当交流电压相位阶跃时,3种锁相环均能快速跟踪相位,PI输出调节至稳定时间一致。

在交流电压相位阶跃时,直流功率发生波动,从阶跃开始至直流功率恢复至阶跃前90%,3种锁相环均需要220 ms左右,但采用Single-PLL时直流功率由0开始增大时间明显短于其他2种锁相环。

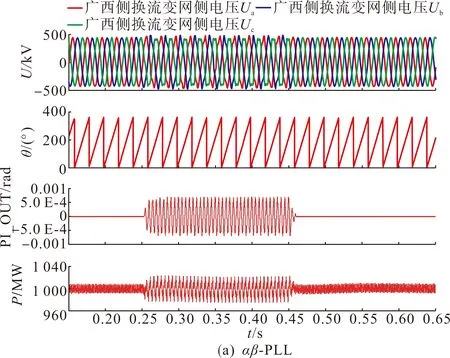

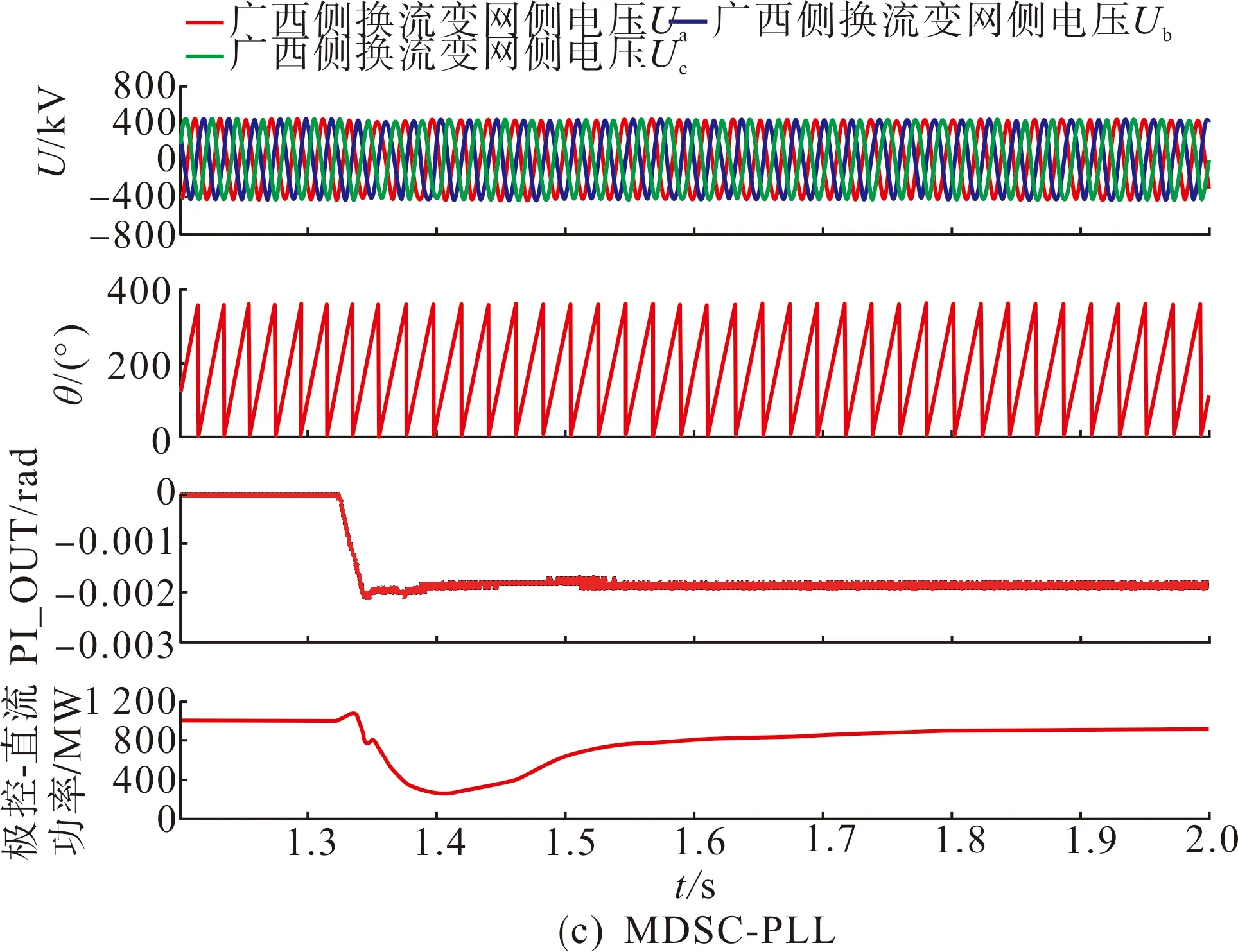

4.2 抗谐波性能测试

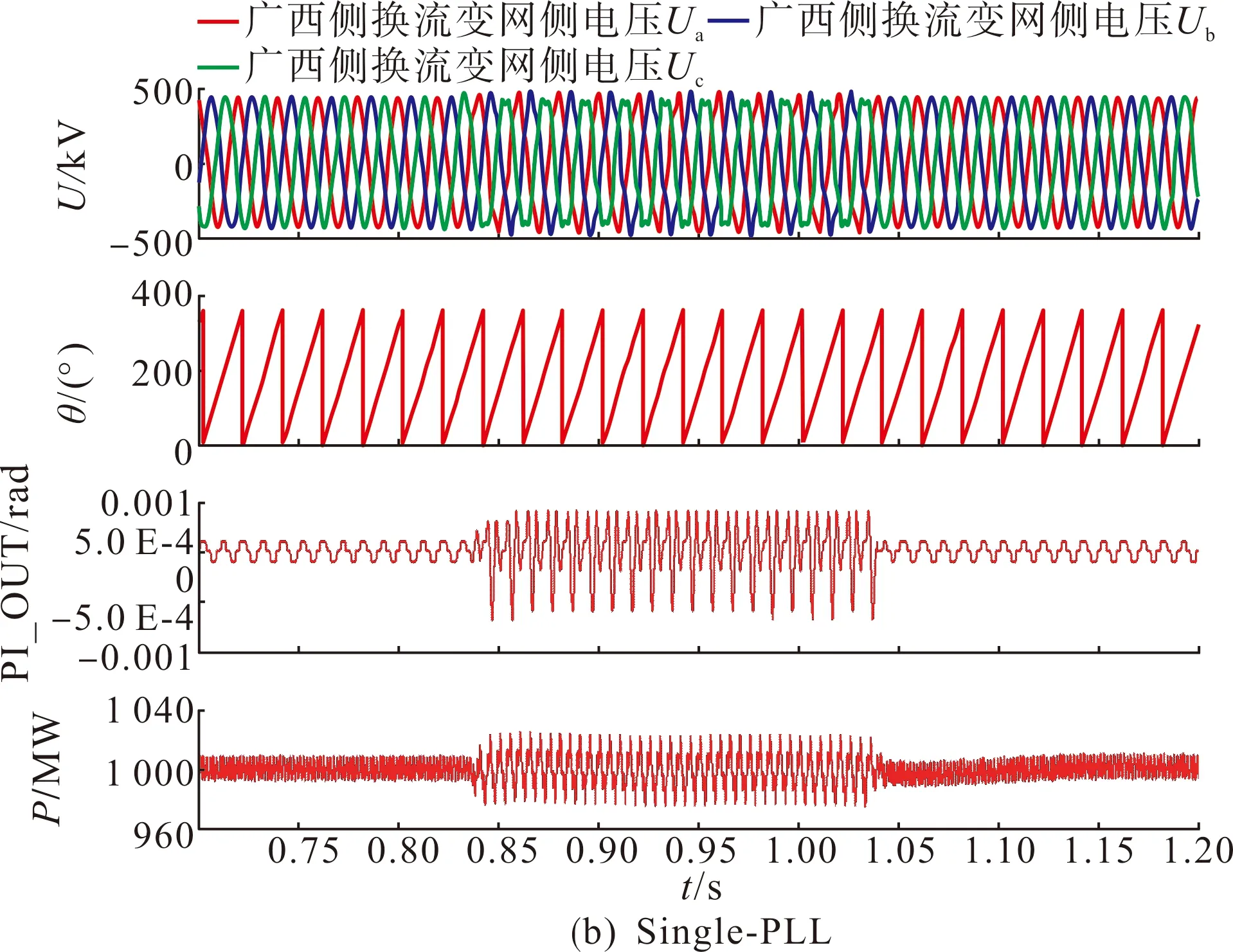

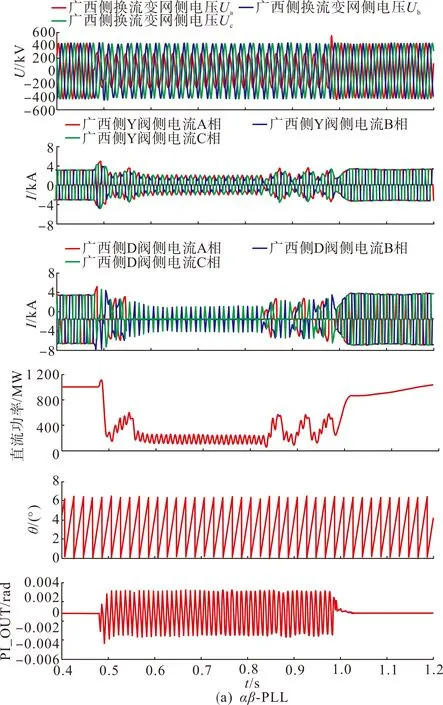

在满功率运行时,在RTDS中设置广西侧交流电压加入10%的5次谐波,持续时间200 ms,测试波形如图8所示。

图8 交流电压带谐波时测试波形Fig.8 Test waveforms during AC-voltage with harmonic wave

根据图8可见,在5次谐波影响下,传统αβ-PLL的PI输出出现4倍频波动,波动幅值约为0.000 7 rad;Single-PLL的PI输出出现2频波动,波动幅值为0.000 7 rad;MDSC-PLL的PI输出波动最小,幅值为0.000 3 rad。

在交流系统加入谐波分量时,直流功率均会出现波动,波动量一致,谐波消除后功率均立即恢复稳定。

可见,相较于传统锁相环,新型单相锁相环和MDSC-PLL均具有更优异的抗谐波干扰能力,其中MDSC-PLL性能最优。

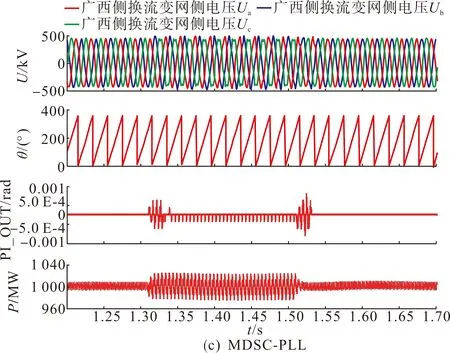

4.3 抗负序性能测试

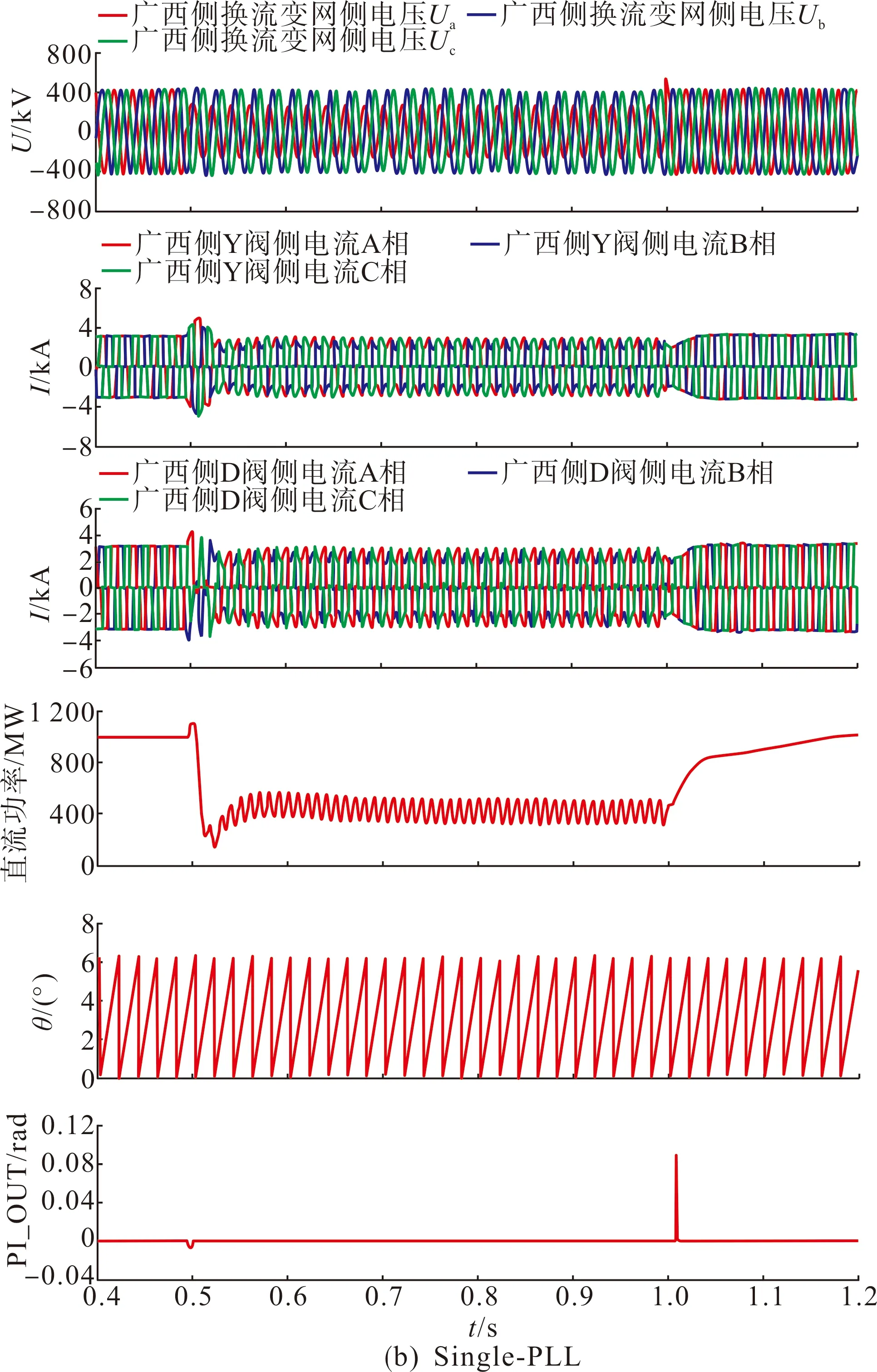

在满功率运行时,在RTDS中设置广西侧交流电压加入10%的负序分量,持续时间200 ms,测试波形如图9所示。

图9 交流电压带负序时测试波形Fig.9 Test waveforms during AC-voltage with negative sequence

图中可见,传统αβ-PLL在负序干扰过程中有较明显的2倍频波动;Single-PLL和MDSC-PLL仅在负序干扰开始和结束时有波动,可快速达到稳定状态。

在负序干扰工况下,直流功率均出现跌落,采用传统αβ-PLL和Single-PLL时,直流功率恢复至故障前功率水平均需要95 ms左右;而采用MDSC-PLL时仅需85 ms。相较于传统αβ-PLL,Single-PLL和MDSC-PLL具有优异的抗负序效果。

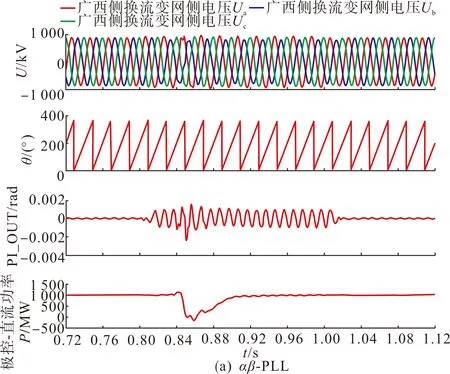

4.4 频率阶跃测试

在满功率运行时,在RTDS中设置广西侧交流电压频率突变至47 Hz,测试波形如图10所示。

图10 交流电压频率阶跃至47 Hz测试波形Fig.10 Test waveforms during AC-voltage frequency step up to 47 Hz

图中可见,频率阶跃至47 Hz后,传统αβ-PLL和MDSC-PLL的PI输出负向偏置,无波动,能稳定跟踪相位;Single-PLL的PI输出负向偏置的同时,存在幅值为0.001 2的2倍频波动。

在47 Hz频率扰动工况下,直流功率均出现跌落,采用Single-PLL时控制系统在429 ms内恢复至故障前功率水平;MDSC-PLL需要468 ms恢复稳定;传统αβ-PLL恢复至突变前功率水平需要509 ms。

传统αβ-PLL和MDSC-PLL加入47 Hz频率扰动后,无波动,对频率偏差的适应性好。

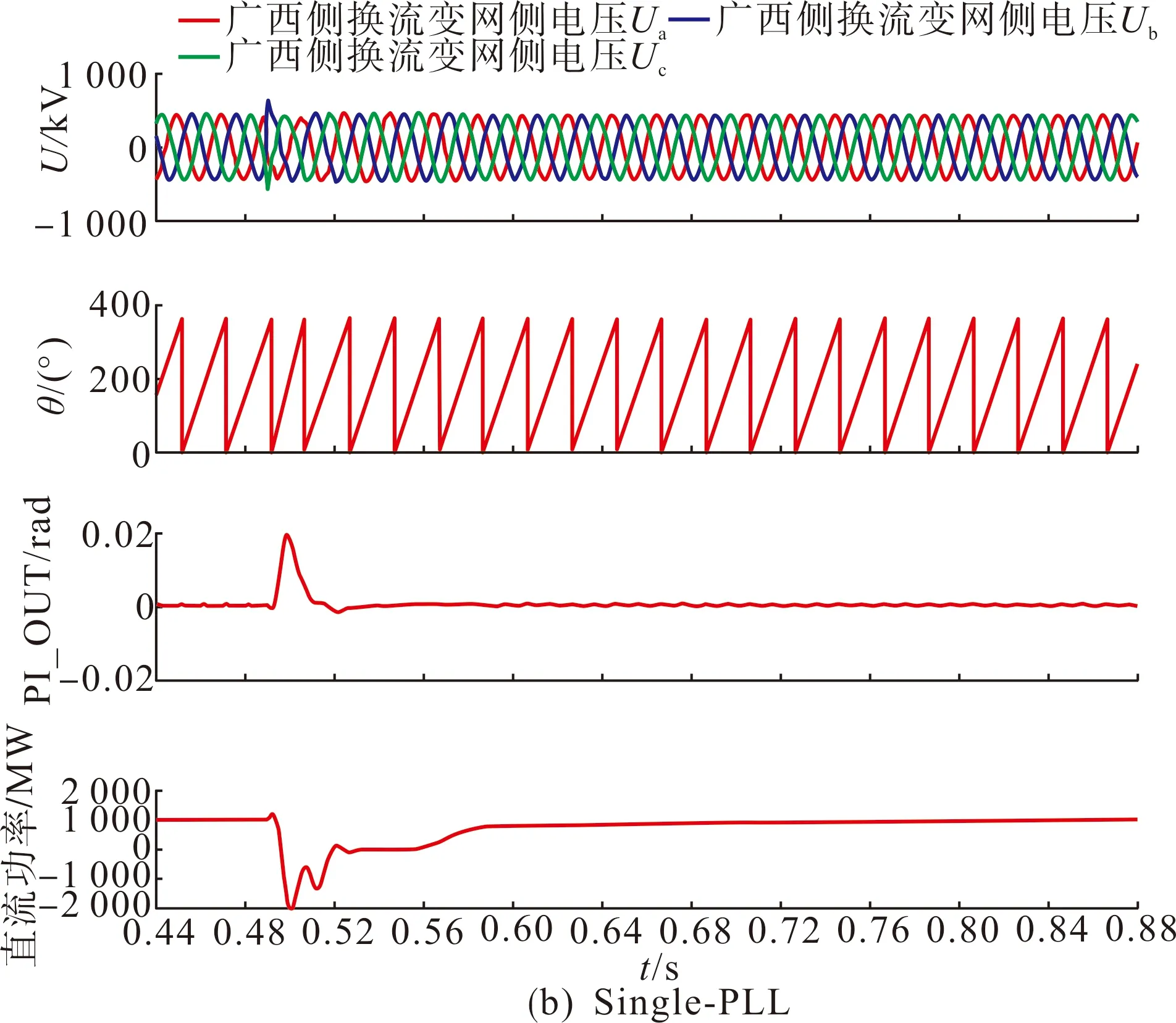

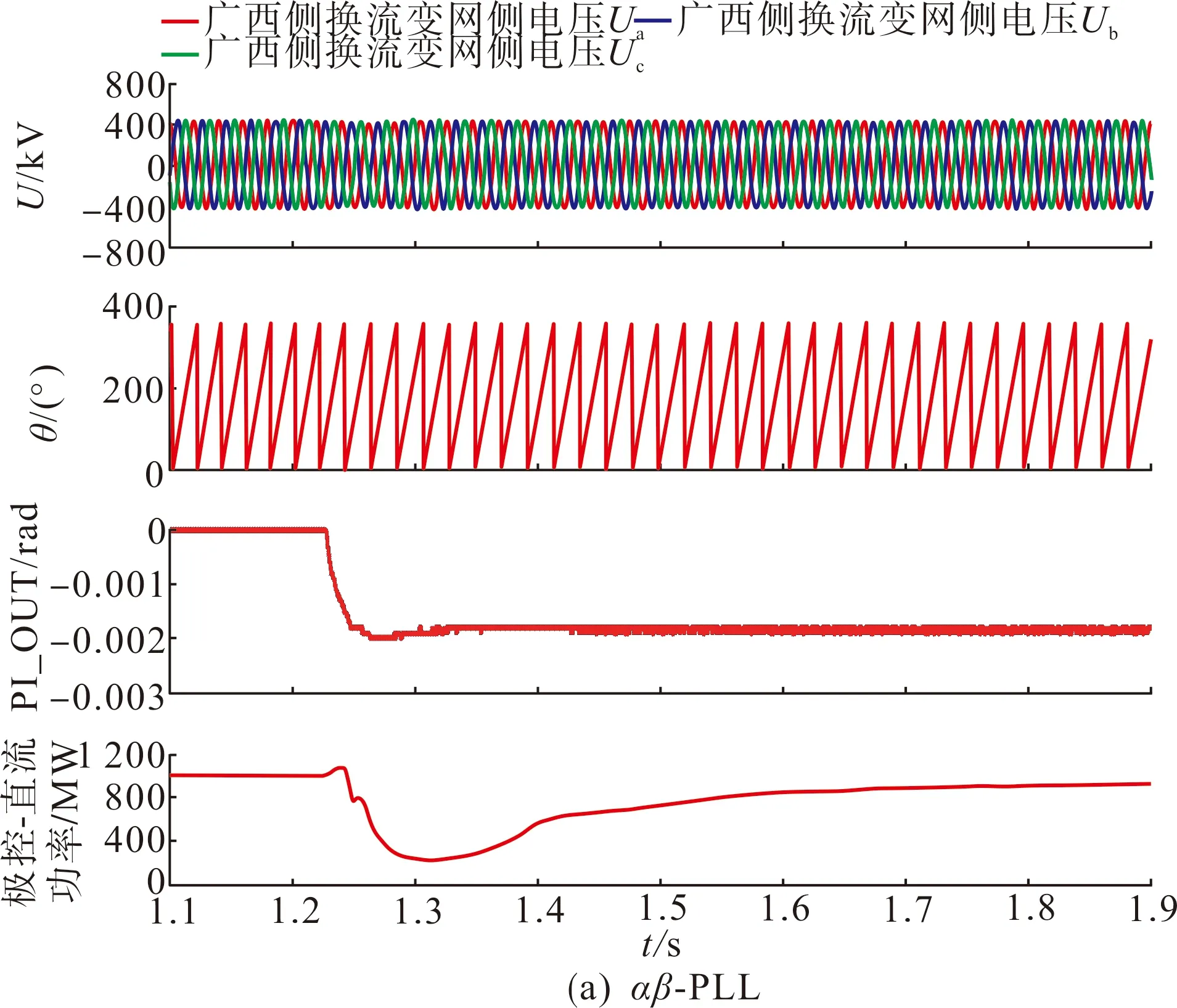

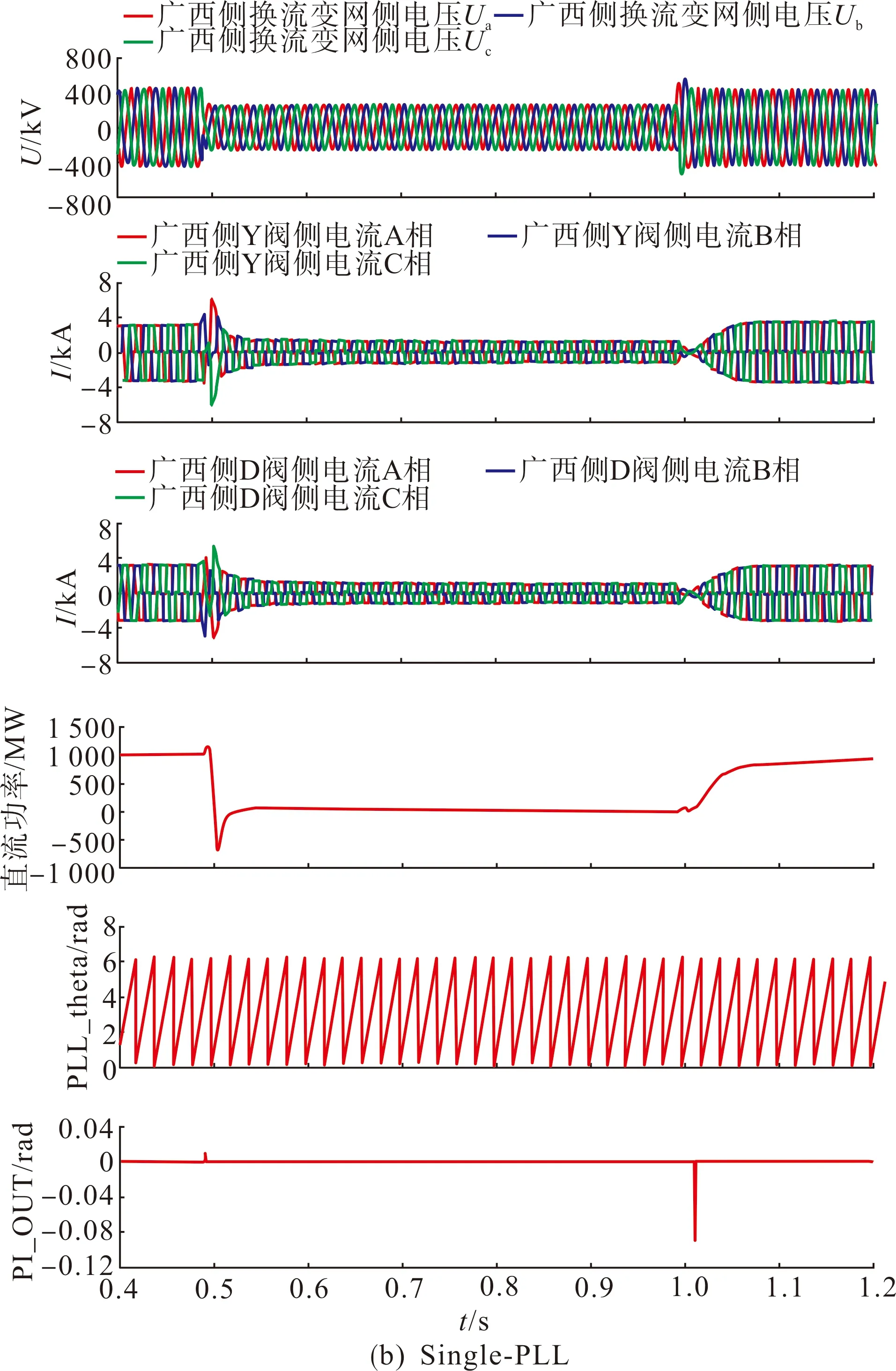

4.5 单相交流故障测试

在满功率运行时,在RTDS中设置广西侧交流A相跌落60%,测试波形如图11所示。

图11 交流电压单相接地故障时测试波形Fig.11 Test waveforms during AC-voltage single phase ground fault

图中可见,在单相交流故障期间传统αβ-PLL的PI输出有较明显的二倍频波动;Single-PLL同MDSC-PLL仅在故障开始及恢复瞬间快速调节,无振荡。

单相交流故障期间,采用传统αβ-PLL锁相环时,发生长时间换相失败,直流功率因此大幅波动;而采用新型Single-PLL及MDSC-PLL锁相环时,仅在故障开始瞬间发生短时间换相失败,直流功率相对平稳。

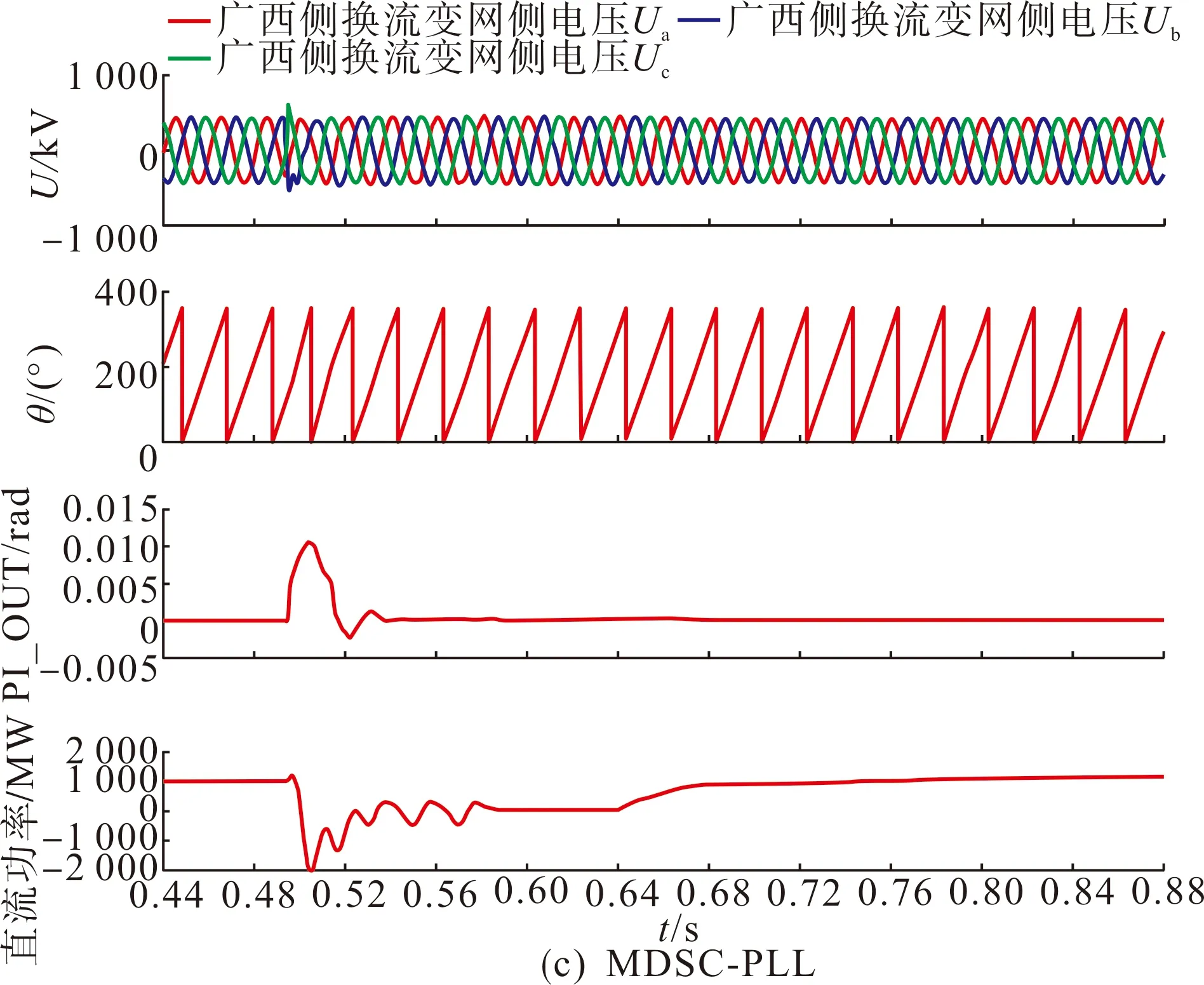

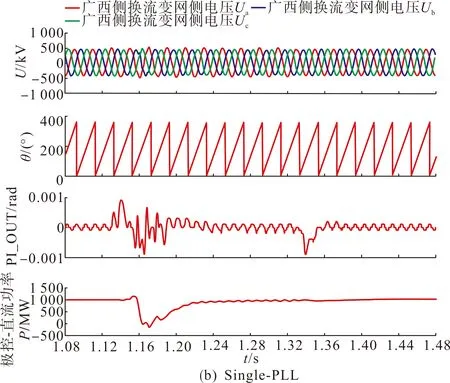

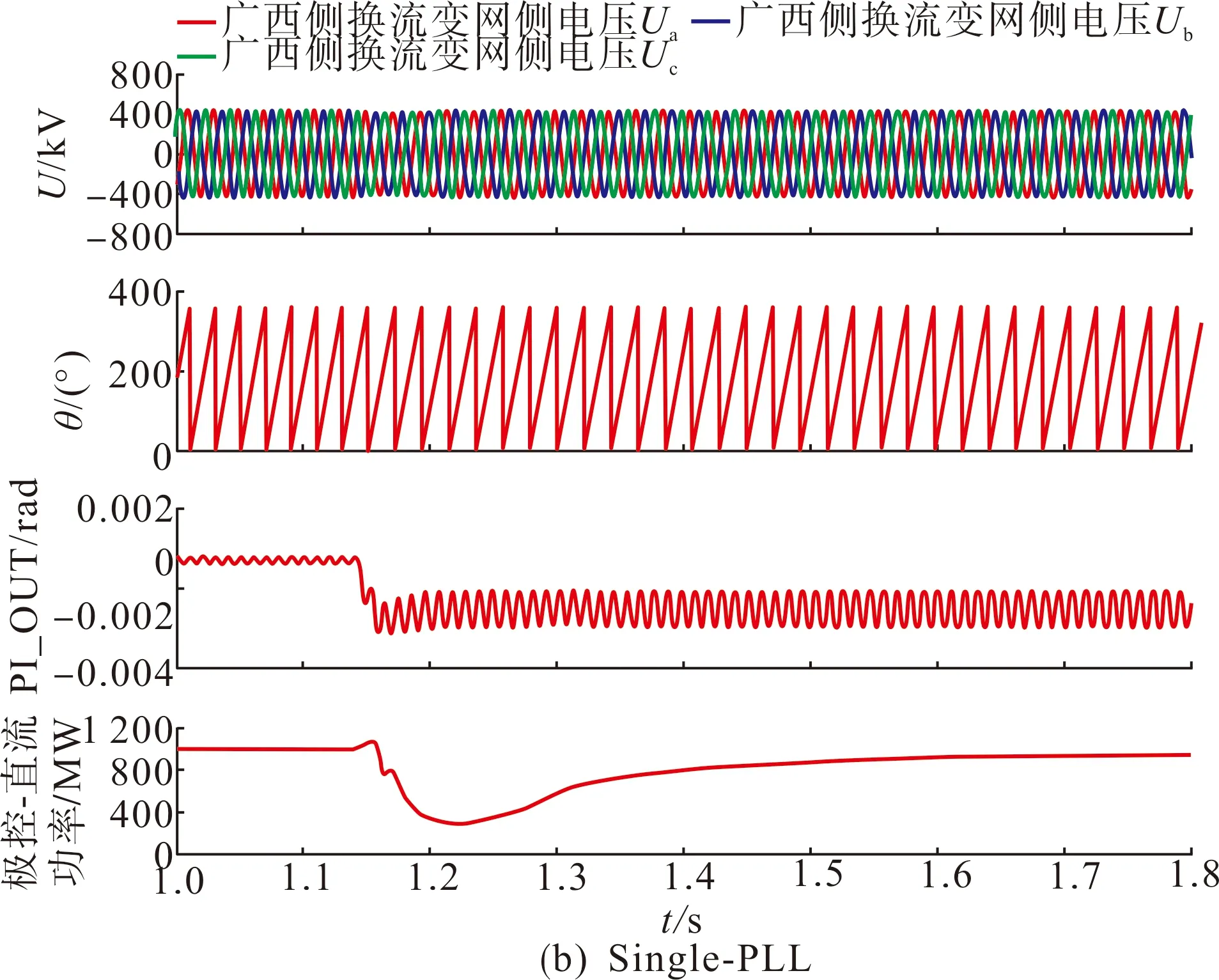

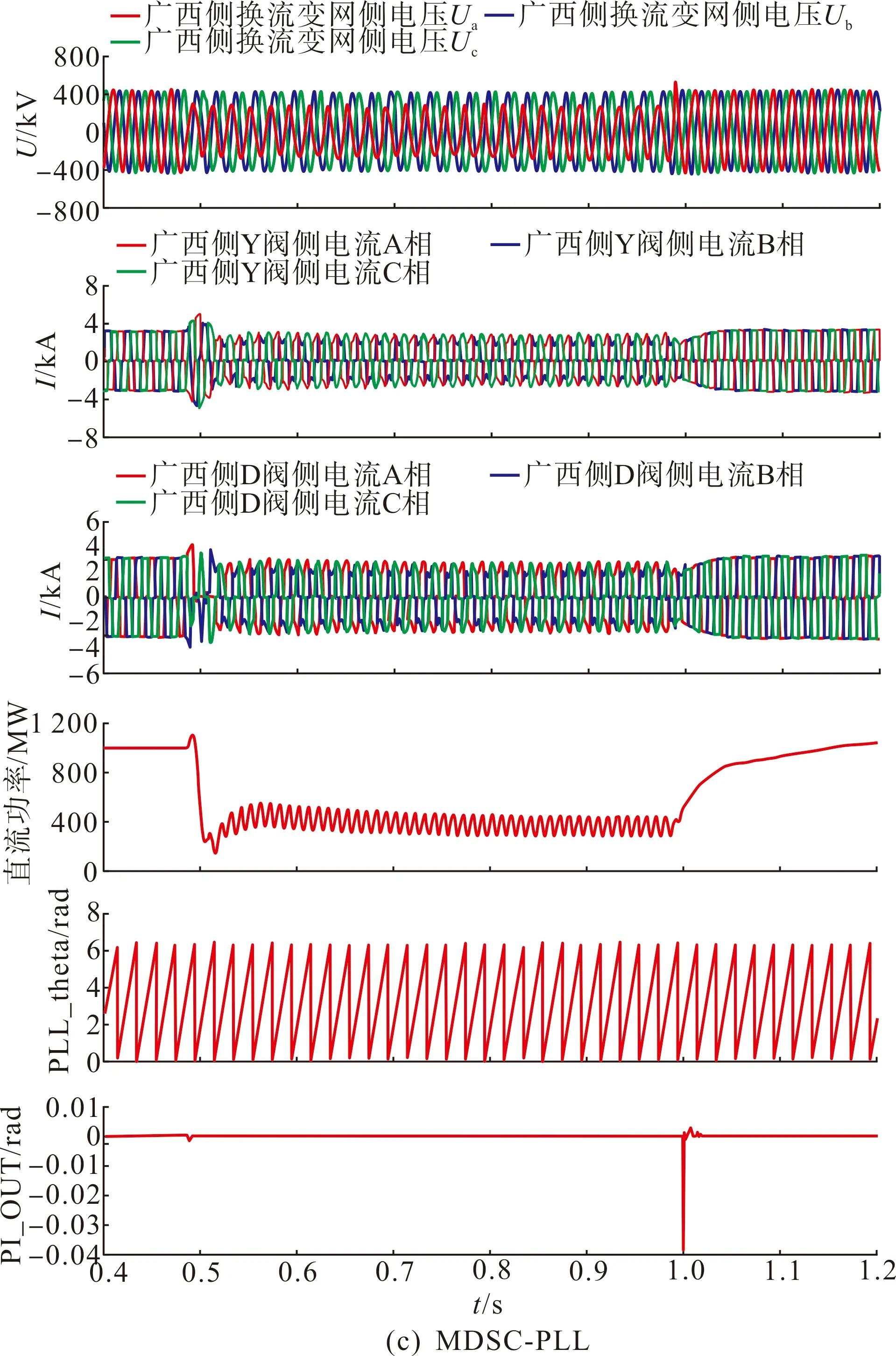

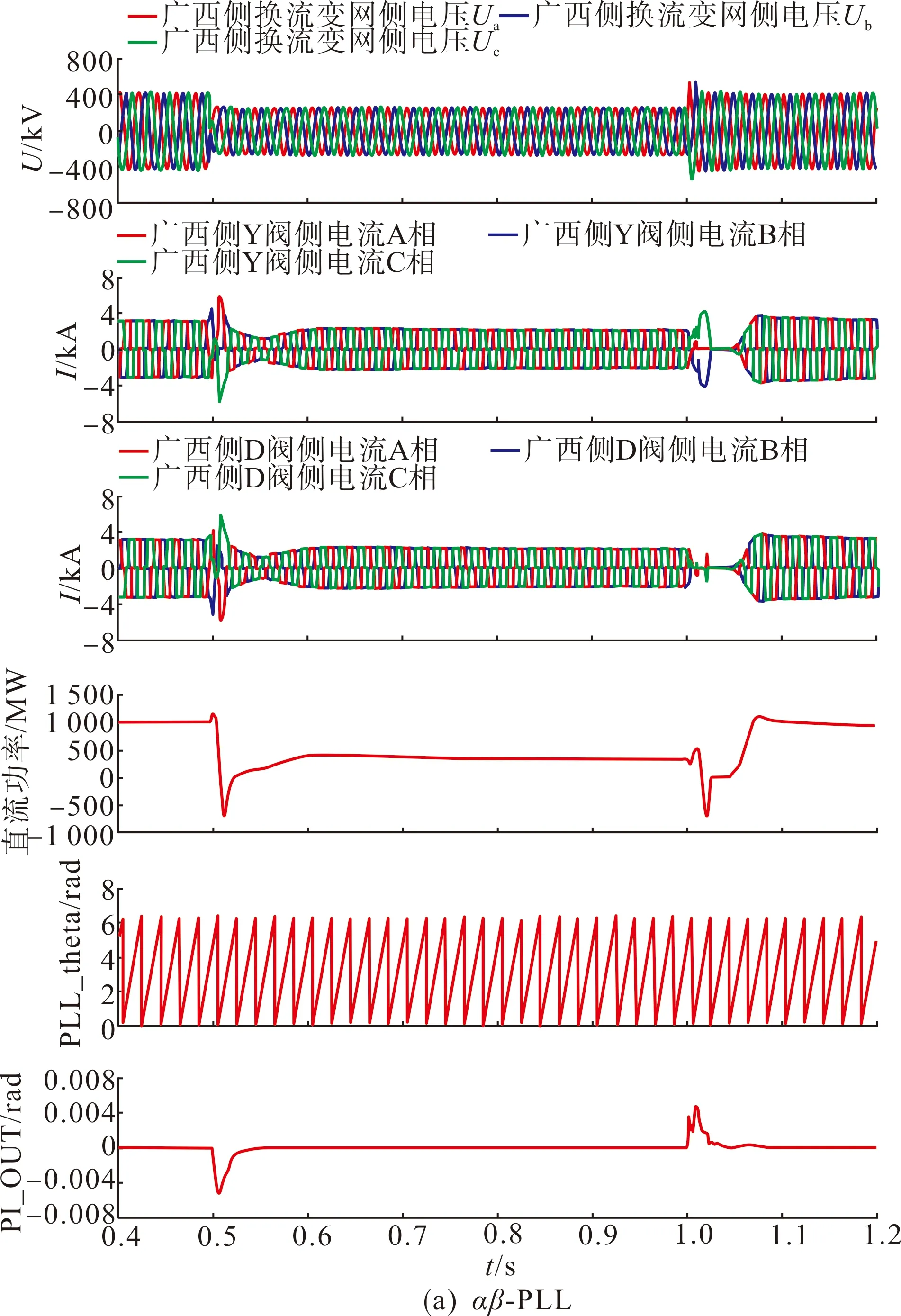

4.6 两相交流故障测试

在满功率运行时,在RTDS中设置广西侧交流两相跌落60%,测试波形如图12所示。

图12 交流电压两相接地故障时测试波形Fig.12 Test waveforms during AC-voltage two phase ground fault

图中可见,故障期间传统αβ-PLL的PI输出有较明显的二倍频波动;Single-PLL同MDSC-PLL仅在故障开始及恢复瞬间快速调节,无振荡。

两相交流故障期间,采用传统αβ-PLL锁相环时,发生长时间换相失败;而采用新型Single-PLL及MDSC-PLL锁相环时,仅在故障开始瞬间发生短时间换相失败。

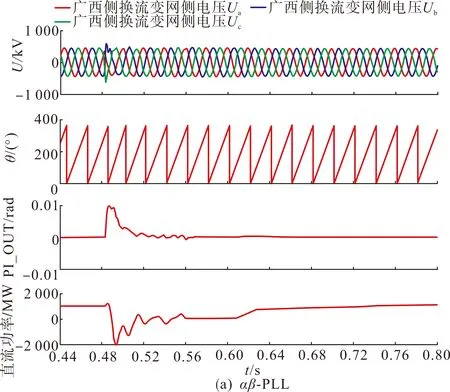

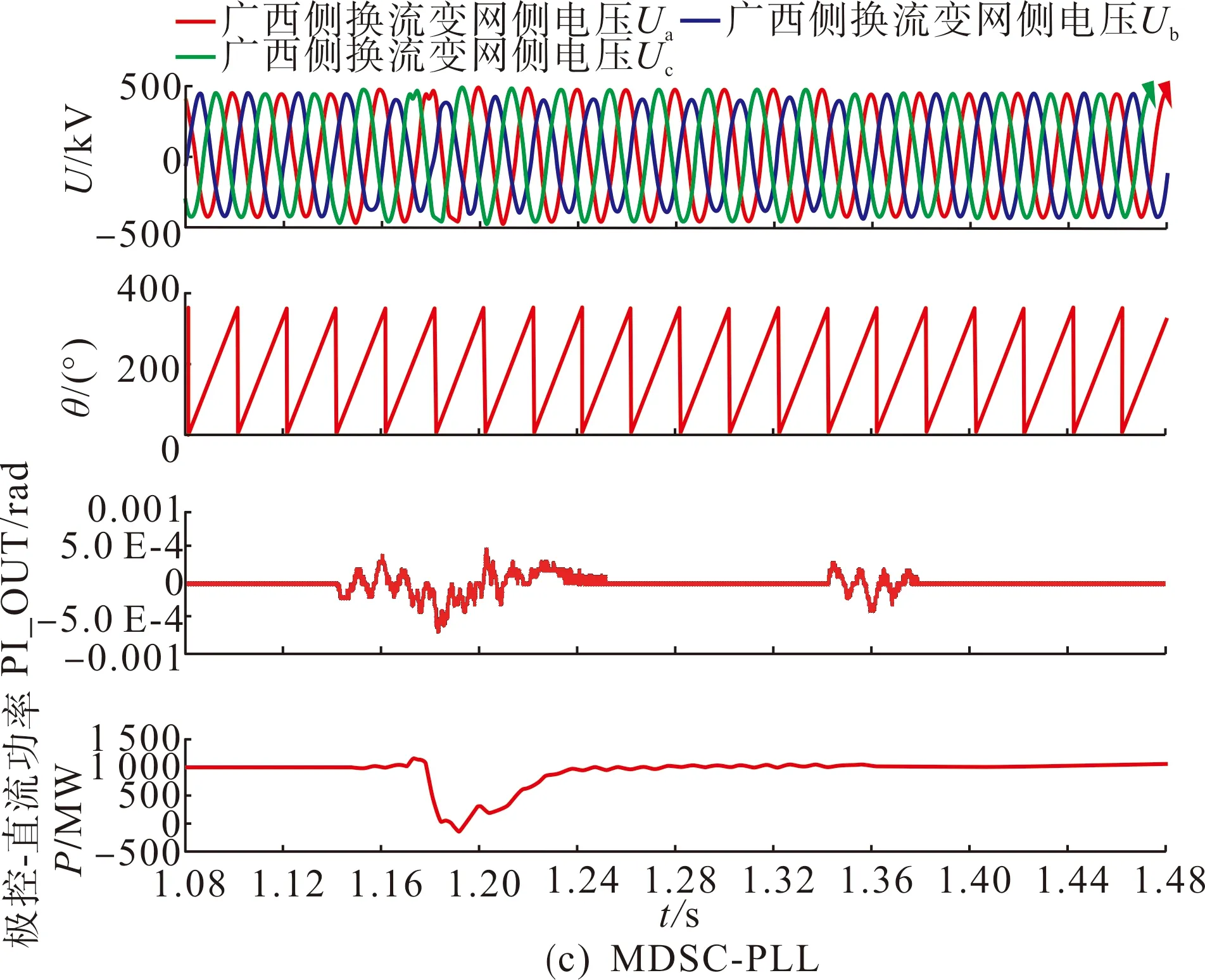

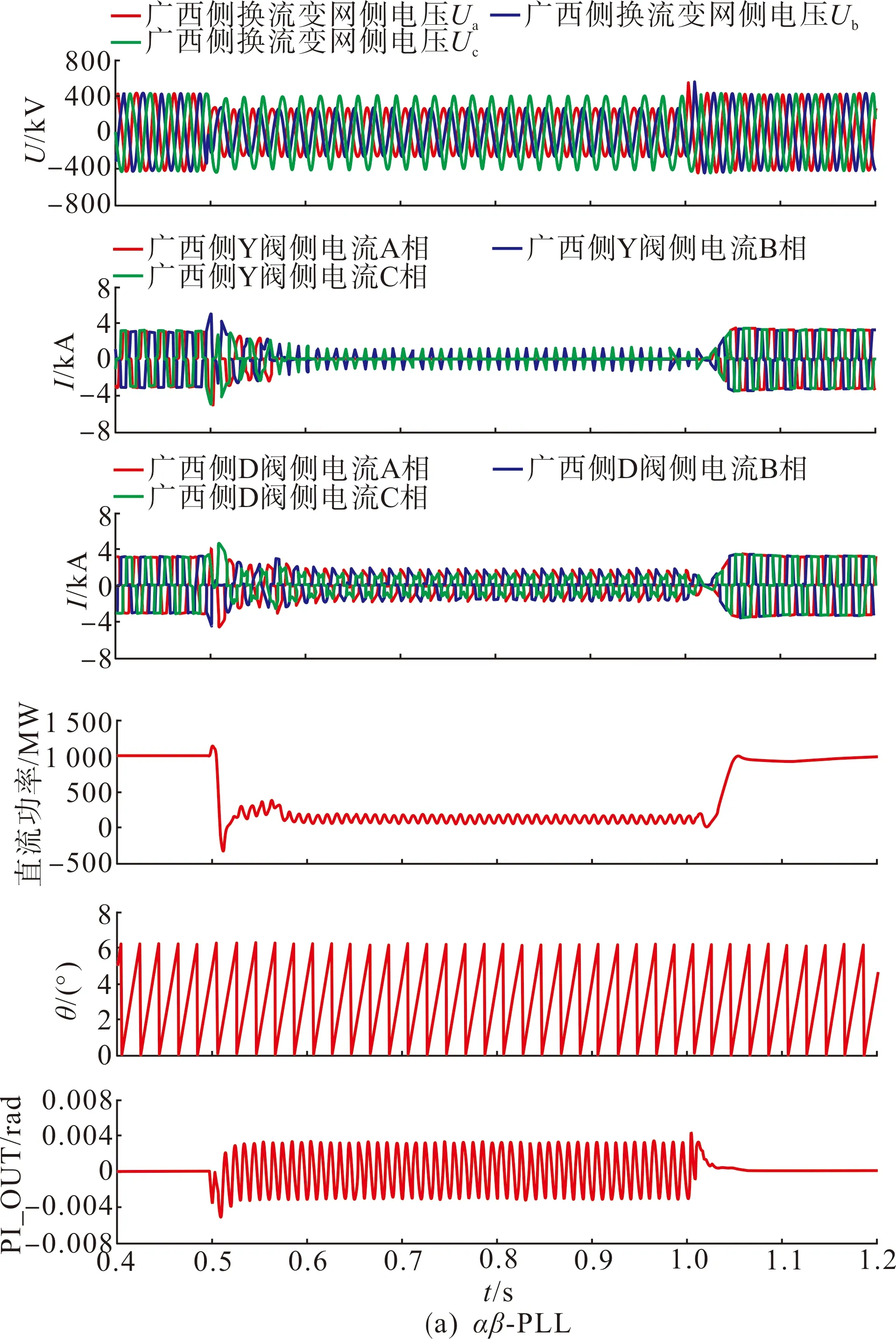

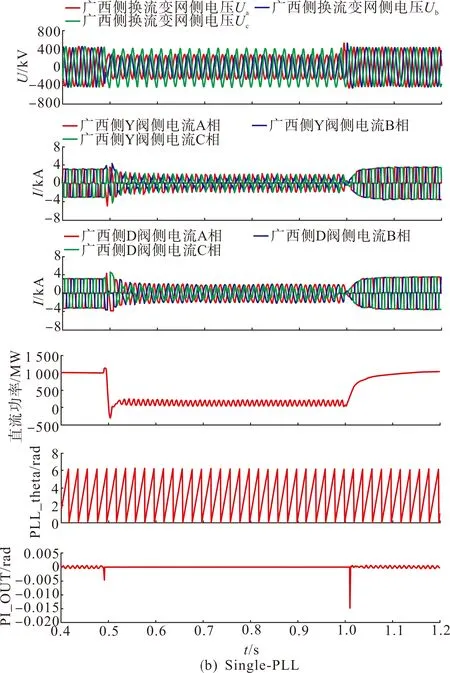

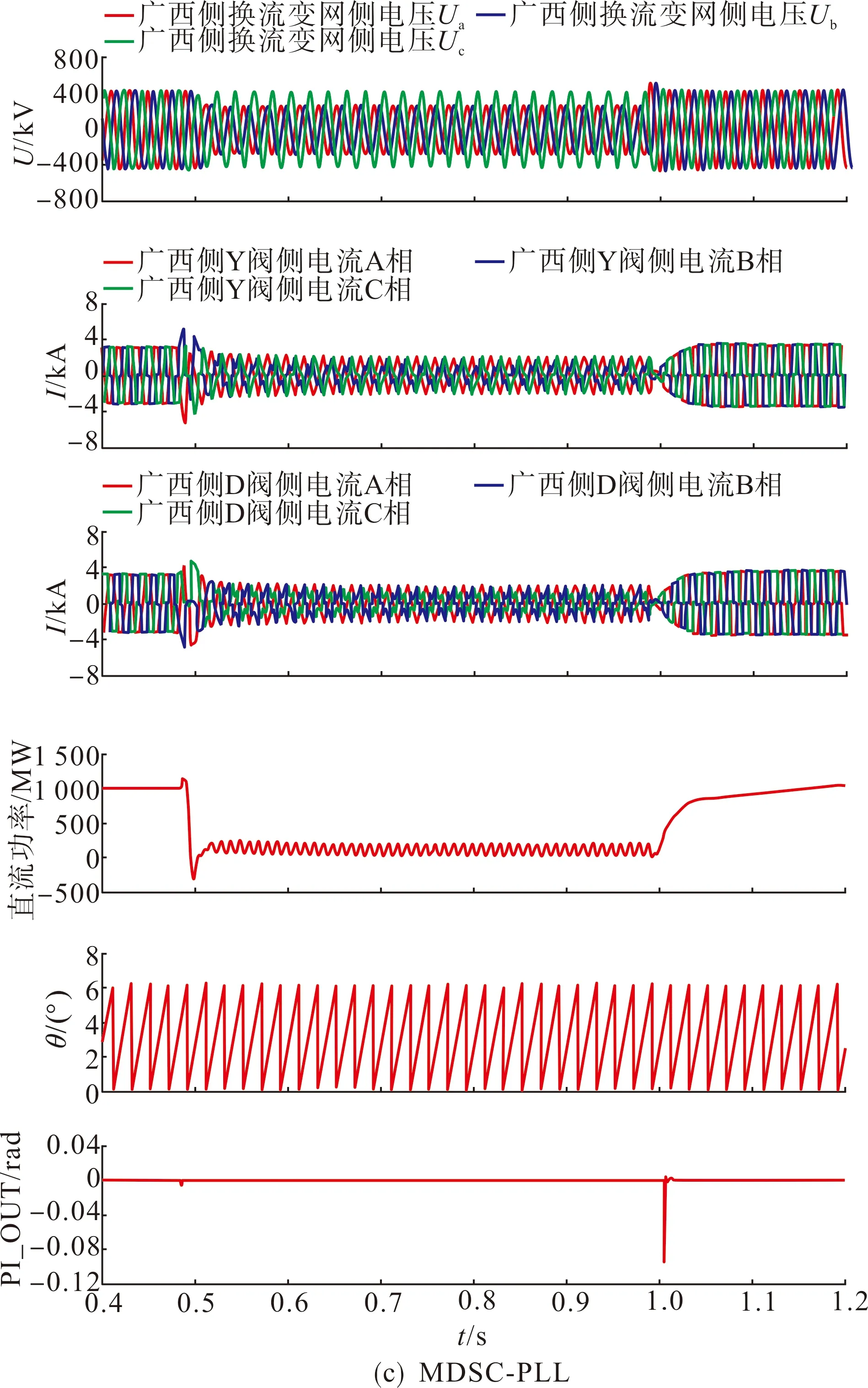

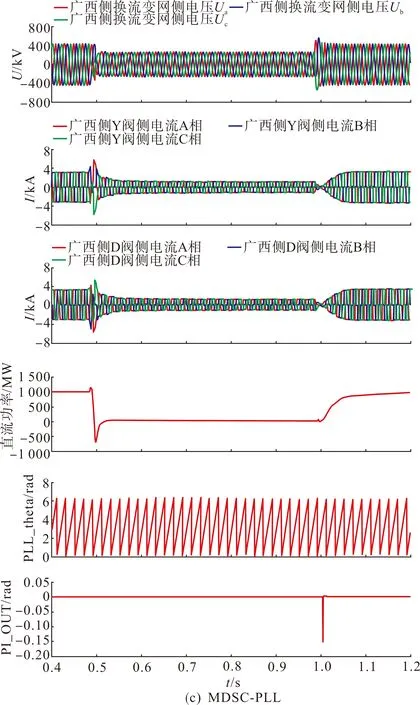

4.7 三相交流故障测试

在满功率运行时,在RTDS中设置广西侧交流三相跌落60%,测试波形如图13所示。

图13 交流电压三相接地故障时测试波形Fig.13 Test waveforms during AC-voltage three phase ground fault

图中可见,在三相对称交流故障期间3种锁相环均快速调节,但传统αβ-PLL调节速度较慢。

采用传统αβ-PLL锁相环时,在故障开始及故障恢复时均发生换相失败;而采用新型Single-PLL及MDSC-PLL锁相环时,仅在故障开始时发生短时间换相失败。受换相失败影响,采用传统锁相环时,故障恢复瞬间直流功率再次发生大幅跌落。

4.8 三种锁相环综合对比分析

根据前述理论分析及RTDS测试结果,可得出如下结论。

1)交流电压相位阶跃,3种锁相环响应时间相近,阶跃后系统有功功率恢复速度相近;

2)抗谐波性能方面,3种锁相环均具有一定的抗谐波干扰能力,新型MDSC锁相环抗谐波能力最强,传统锁相环抗谐波干扰能力最差;

3)抗负序性能方面,新型MDSC锁相环和新型单相锁相环的抗负序能力均强于传统锁相环;

4)频率适应性方面,新型单相锁相环的频率适应性较差,传统锁相环和新型MDSC锁相环的频率适应性较好;

5)交流故障期间,新型单相锁相环和新型MDSC锁相环的锁相准确性更高,且能明显减小故障期间的换相失败次数。

由此可见,传统锁相环在交流系统谐波、交流故障等工况下,跟踪相位能力较差,应用于实际工程时,需考虑增加其抗谐波干扰能力及应对交流故障处理;基于SOGI-QSG的新型单相锁相环在高压直流输电中可与分相触发控制结合,提升高压直流输电系统的抗谐波及抗负序能力、减少换相失败的发生,但其频率适应性较差,实际应用时可考虑工程实际情况增加频率适应环节;基于MDSC的新型三相锁相环各方面性能优异,适宜在实际工程推广应用。

5 结语

本文分析了传统αβ锁相环、基于SOGI-QSG的单相锁相环、采用MDSC的新型三相锁相环的工作原理及优缺点,将其应用于高压直流输电控制系统中,并在传统高压直流输电系统的RTDS硬件闭环测试平台上,横向对比测试了交流电压出现常见故障时3种锁相环的响应特性,分析了各个锁相环的优缺点。认为传统αβ锁相环跟踪相位能力较差,基于SOGI-QSG的单相锁相环的频率适应性较差,而采用MDSC的新型三相锁相环各方面性能优异。本文结论可为后续工程选择适宜的锁相环提供理论及试验依据。