基于同步异构DSP的CLA模块的脉冲均分算法研究*

2020-03-10梁磊磊何高清

梁磊磊,何高清

(合肥工业大学 机械工程学院,安徽 合肥 230009)

0 引 言

插补算法的质量直接影响数控系统的精度和速度, 是数控机床的重要技术指标。插补器是数控系统用来完成运动轨迹拟合的程序或硬件。数控系统的插补算法大致分为:脉冲当量法与数字积分法[1]。(1)脉冲当量法适用对速度与精度要求不高,以步进电机为主要控制对象的开环数控系统[2];而现在的数控系统大都采用数字积分法插补,相较于脉冲当量插补,数字积分法拥有更高的插补速度与精度。(2)数字积分法包括粗插补与精插补,其中粗插补是将给定的轨迹分割为较大的段,完成插补的预处理;精插补是将粗插补算出的直线段再细分,进行插补运算,并形成最后的脉冲输出,从而精确地控制电机的运动。精插补的关键在于实现输出脉冲的均匀化,若只采用CPU完成精插补,则会消耗CPU大量的时间资源,影响其他通讯与控制程序的执行,降低系统的实时性。为了提高系统的实时性,同时完成输出脉冲均匀化的运动控制,当前主流的解决方案是由主CPU完成粗插补,再由CPLD、FPGA或运动控制卡等模块,独立完成精插补程序[3-8]。但是,这种结构增加了控制系统的硬件与软件的复杂度,开发难度大,不利于在空间要求高的紧凑型数控系统中使用。

本研究提出一种基于同步异构DSP的CLA模块的脉冲均分插补器(CLA是TMS320F28377芯片中可以独立于CPU运行的内嵌模块,通过主控制器与CLA模块并行处理任务,即主控制器发送指令触发CLA软中断,CLA模块上运行脉冲均分算法执行精插补器的任务,输出脉冲;这种结构无需外接其他控制组件,可降低系统的复杂度,提高系统的可靠性与实时性[9])。

1 CLA模块原理与特性

内置于同步异构DSP的模块,通过引入并行处理的功能,扩展了主CPU的能力,用于对时间要求严格的控制,实现了更快的系统响应和更高频率的控制回路;通过将CLA用于对时间敏感的关键任务,可以释放主CPU去执行其他系统任务和通信,从而提高了系统的实时性。

目前,为了实现精插补过程中,保持输出脉冲的均匀化,同时不降低系统的实时性,往往采用CPU外接运动控制模块来实现。相较于传统的解决方案,采用同步异构数字信号处理器的CLA模块来实现脉冲均分算法,具有以下优势:

(1)CLA模块与CPU共用系统时钟源,即拥有相同的时钟速率,无需为外置模块配置独立的时钟信号源;

(2)CLA模块建立于独立的构架,其任务由CPU软件触发或由硬件中断触发,无需配置复杂的数据与控制总线;

(3)CLA模块拥有GPIO等外设的操作权限,这些权限由CPU分配给CLA,因此CLA可以绕过CPU直接控制CPIO,不必通过CPU来控制运动控制模块输出脉冲,减少了消息传递的跨度,提高了系统的可靠性与实时性;

(4)CLA模块与CPU的程序都可以采用C语言编写,且可以在相同的开发环境下进行程序的编写、调试与下载,降低了开发难度,提高了开发效率与系统的可维护性。而如DSP+FPGA、ARM+CPLD等方案,需要针对每个主芯片,采用不同的开发方式与环境[10],难度较大的VHDL等硬件描述语言,更是增加了控制系统的研发成本与时间。

2 精插补脉冲均匀化算法的设计

精插补脉冲均匀化算法是服务于数字积分法的精插补部分。由于计算机系统是离散的,在精插补的过程中,直线段细分的结果可能得不到整型数,导致计算机无法处理。在计算机中,最直接的方法是对结果进行取整,但这样会导致在每个插补周期脉冲周期偏小,即脉冲周期内会有一段时间没有脉冲产生,即为空行程,从而导致了脉冲不均匀,会对电机运行的稳定性产生消极的影响。

以插补周期为4 ms, GPIO输出脉冲最小翻转时间为1 us为例,则有:

(1)

式中:Nmax—插补周期内的最大脉冲数;T1—插补周期时间;Tmin—输出脉冲最小翻转时间。

插补周期内的脉冲周期为:

(2)

式中:N—插补周期内输出的脉冲数量。

脉冲输出的时间占插补周期的比值可以量化输出脉冲均匀化的水平,其值愈小,则输出脉冲愈不均匀,其数学表述为:

(3)

式中:μ—脉冲不均匀水平;δ—脉冲均匀化水平。

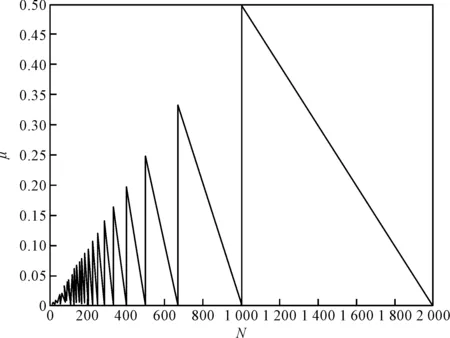

通过式(3),可得脉冲不均匀水平μ与脉冲数N的关系,如图1所示。

图1 脉冲不均匀水平μ与脉冲数N的关系

由图1可知:在脉冲数N=1 001时,脉冲不均匀水平μ可达到最高值0.499 5;且在N的多数取值中都出现了脉冲不均匀现象,故有必要采取算法消除脉冲不均匀的现象。

通常情况下,若输出脉冲的周期变化小于驱动器允许脉冲输入的最小周期时,就可以认为输出脉冲周期是均匀的。以此为依据,在插补周期内,设置2个脉冲周期,两者之间相差1个输出脉冲最小周期,即驱动器允许脉冲输入的最高频率为 500 kHz,则有方程组:

(4)

解得:

(5)

式中:TP1—脉冲周期1;N1—周期为TP1的脉冲数;TP2—插补周期2;N2—周期为TP2的脉冲数。

将TB=2 us与T1=4 ms代入式(5),可得:

(6)

本文通过设置这2个插补周期TP1与TP2,进行精插补运算,可以在算法层面彻底消除脉冲输出脉冲不均匀的现象。

3 基于CLA模块的脉冲均分算法实现

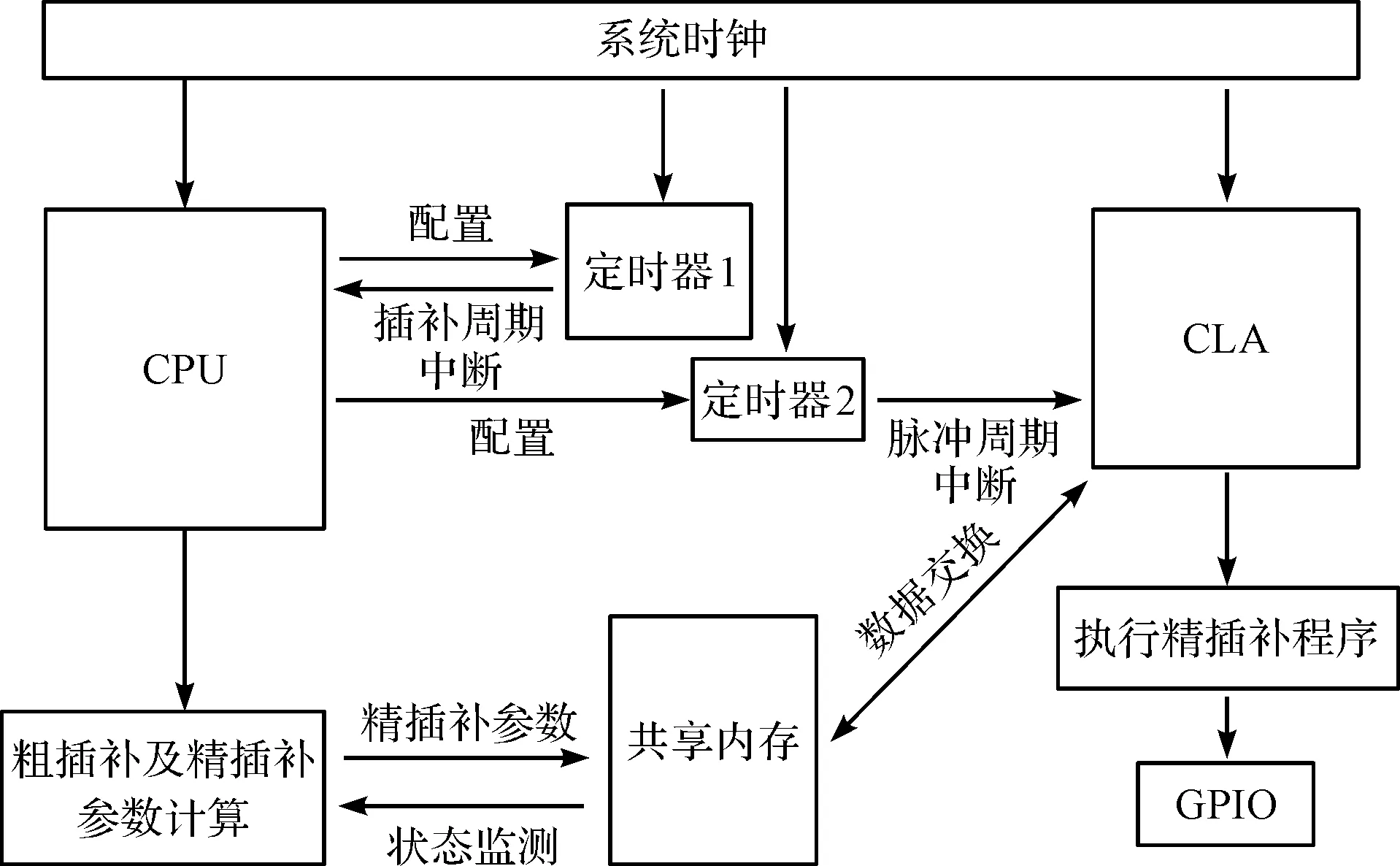

基于同步异构DSP的CLA模块,本文构建的双脉冲周期精插补脉冲均匀化算法的硬件系统结构图如图2所示。

图2 硬件系统结构

由图2可知:控制系统同时为CPU与CLA提供时钟源与存储空间,通过主CPU配置定时器2的定时中断,为CLA模块提供插补的基准频率,触发CLA模块来执行精插补运算。同时,控制系统分配给CLA模块控制GPIO的权限,用来输出插补的脉冲。

TMS320F28377的定时器1的定时中断周期设置为4 ms,用于提供插补周期,由主CPU来执行该中断服务程序;定时器2的定时中断周期为1 us,为最小脉冲的电平翻转时间,即基准频率,由此得出精插补器输出的最小脉冲周期为2 us。

CLA的插补任务由定时中断来触发,在定时器2的每个定时中断服务程序中,CLA可以选择脉冲的发送使能或停止,从而控制输出脉冲的周期;执行精插补程序变量存储在CPU与CLA的共享内存区域,CPU与CLA都可以直接读取与修改这些变量,以加快数据传输的速度。

在每个插补周期中,精插补中2个插补周期的长度与脉冲数,由主CPU计算得出,再传递给CLA,这部分的C语言源程序如下:

PulseA=2 000/N;

PulseB=PA+1;

CountA=(PulseA+1)*N-2000;

CountB=2 000-PulseA*N;

其中:N—插补周期内需要输出的脉冲数;PulseA—脉冲的电平翻转时间1;PulseB—脉冲的电平翻转时间2;CountA—翻转时间为PulseA的脉冲计数;CountB—翻转时间为PulseB的脉冲计数。

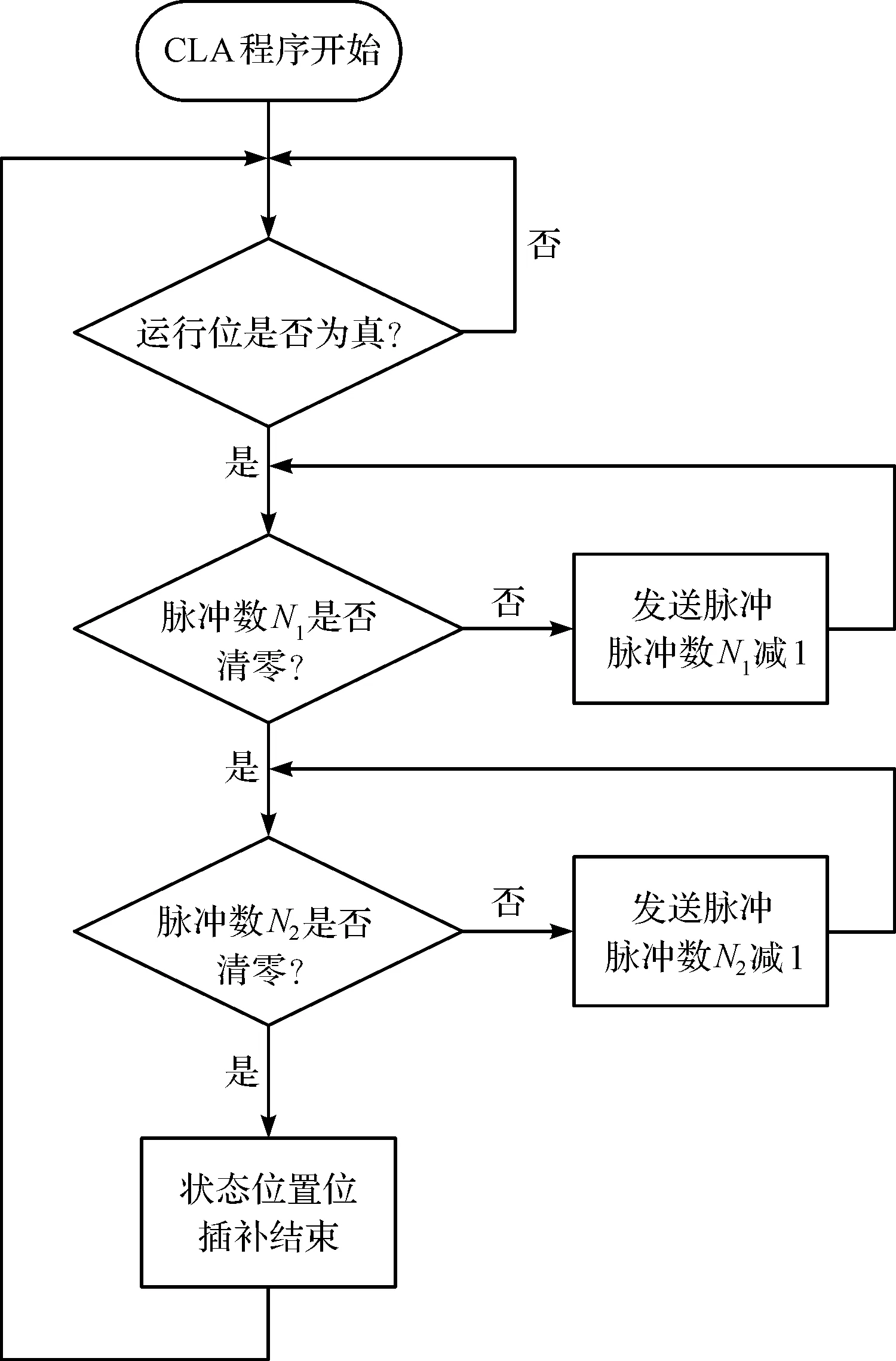

使用CLA模块,实现脉冲均分算法的流程简图如图3所示。

图3 脉冲均分算法的流程简图

由图3可知:CLA通过接受主CPU通过共享内存传递过来的参数,来执行精插补。

当一个插补周期开始时,设置运行位为真,CLA便以定时器2的定时中断为基准,开始执行2个插补周期与脉冲数的插补指令,插补完成以后,以状态位置位来通知主CPU当前的插补周期任务已经完成,CLA接着开始等待下一个插补周期的任务。

4 仿真与实验

本文使用CCS(code composer studio)软件的在线调试功能,以TMS320F28377S为硬件实验平台,在插补周期为,GPIO输出脉冲的最小周期为的条件下,选取插补周期内输出的脉冲数N=1 001与667这两个会导致脉冲不均匀水平较大的取值,进行单脉冲周期精插补算法,并与基于CLA的双脉冲周期精插补算法进行对比实验。

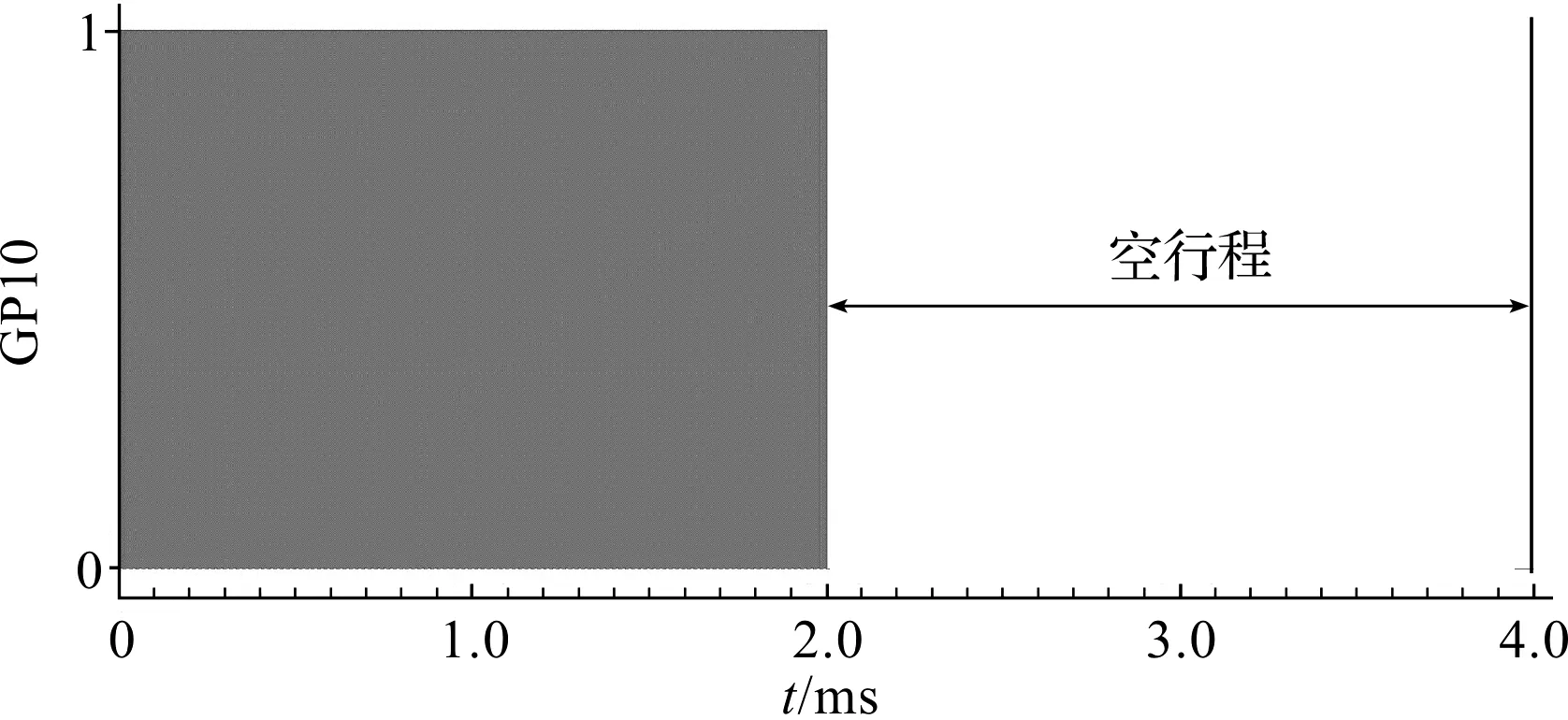

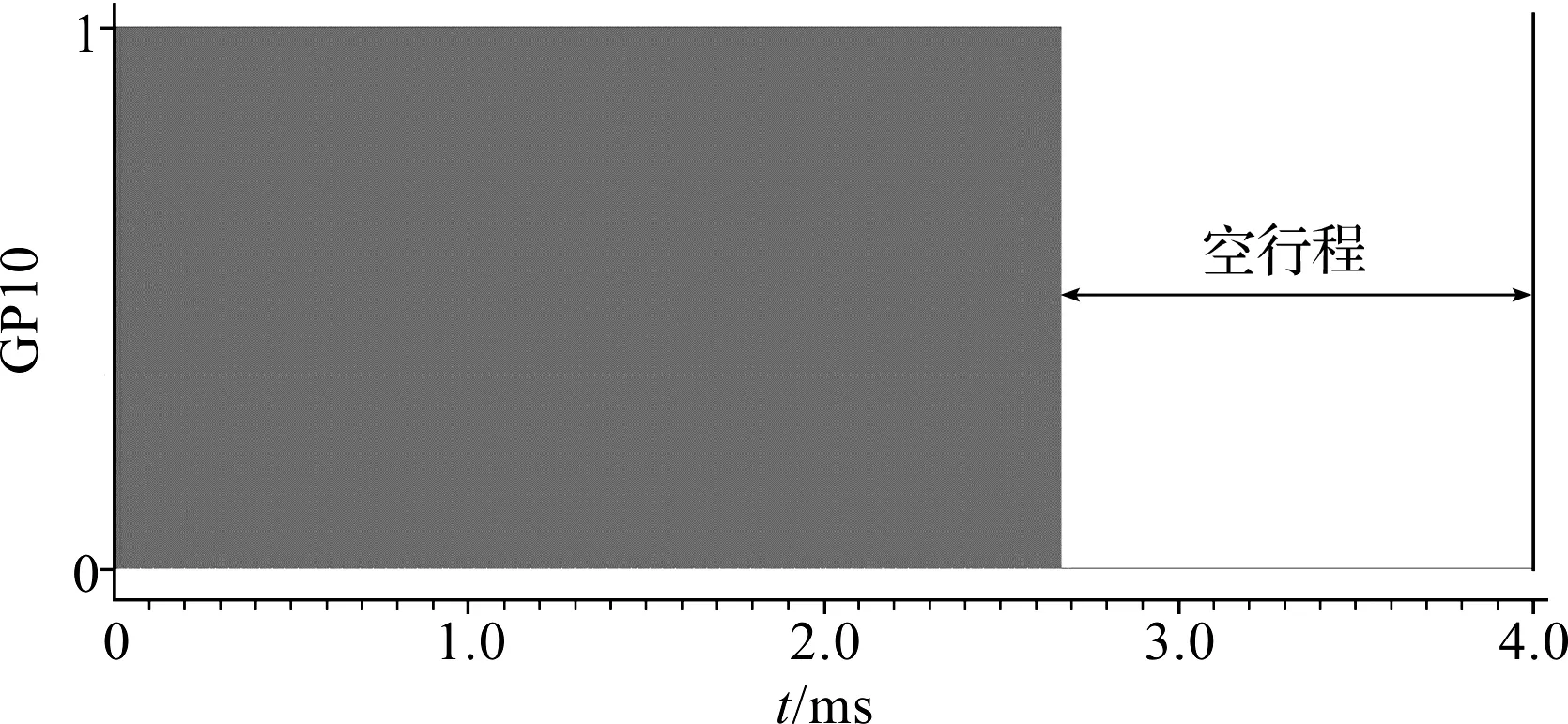

当N=1 001时,使用单脉冲周期精插补算法后,脉冲在插补周期内的分布情况如图4所示(这种情况下脉冲分布的不均匀程度最严重,空行程时间占据了脉冲周期的49.95%)。

图4 当N=1 001时使用单脉冲周期精插补算法后脉冲在插补周期内的分布情况

由图4可知:在整个插补周期内,脉冲只分布在0~2 ms这一时间段,在该时间段内已经输出了1 001个脉冲;在2 ms~4 ms时间段内没有脉冲输出,即空行程时间占脉冲周期的比例约为50%。由此可见,在误差允许的范围内,该结果与理论结果(空行程时间占据了脉冲周期的49.95%)相符合。

当N=667时,使用单脉冲周期精插补算法后,脉冲在插补周期内的分布情况如图5所示。

图5 当N=667时使用单脉冲周期精插补算法后脉冲在插补周期内的分布情况

由图5可知:在整个插补周期内,闲置时间占据了脉冲周期的比例约为1.33/4=33.25%。由此可见,在误差允许的范围内,该结果与由式(3)得出的理论值33.33%相符合。

这些实验结果证明,采用单脉冲周期精插补算法会出现输出脉冲分布不均匀的情况。

理论上,采用改进的双脉冲周期精插补脉冲均匀化算法后,在的取值范围内,脉冲输出时间都会占据整个插补周期的100%,从而可以消除输出脉冲不均匀的现象。

由式(6)可得,当N=1 001、667时,脉冲均分算法的运行参数如表1所示。

表1 当N=1 001、667时脉冲均分算法的运行参数

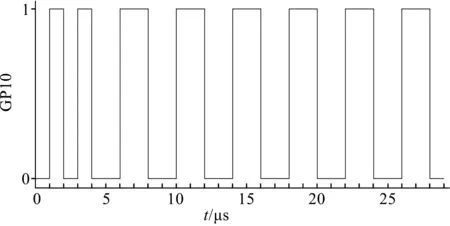

当N=1 001时,使用双脉冲周期精插补算法后,脉冲在插补周期内的分布情况如图6所示。

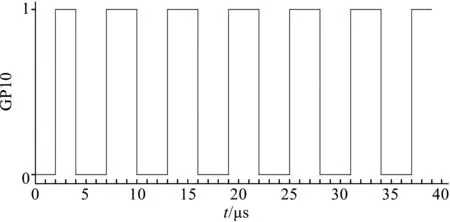

当N=667时,使用双脉冲周期精插补算法后,脉冲在插补周期内的分布情况如图7所示。

图6 当N=1 001时使用双脉冲周期精插补算法后脉冲在插补周期内的分布情况

图7 当N=667时使用双脉冲周期精插补算法后脉冲在插补周期内的分布情况

从图(6,7)可以看出:在N=1 001与667的情况下,输出脉冲占据了插补周期的全部时间,没有空行程,达到了输出脉冲均匀化的效果。

当N=1 001,使用双脉冲周期精插补算法时,脉冲在插补周期起始时间段的输出波形如图8所示。

图8 N=1 001时使用双脉冲周期精插补算法时脉冲在插补周期起始时间段的输出波形

由图8可知:当N=1 001时,输出脉冲由起始2个周期为2 us的脉冲与后续周期为4 us的脉冲组成。

当N=667,使用双脉冲周期精插补算法时,脉冲在插补周期起始时间段的输出波形如图9所示。

图9 N=667时使用双脉冲周期精插补算法时脉冲在插补周期起始时间段的输出波形

由图9可知:当N=667,输出脉冲由起始1个周期为4 us的脉冲与后续周期为6 us的脉冲组成。

将以上结果与表1中的数据相比较可知,脉冲均分算法的实际输出结果与理论的一致,说明该算法在实际硬件中能够正确运行,且达到了预期的效果。同时,实验结果说明了能够基于同步异构DSP的CLA模块的硬件结构,实现双脉冲周期精插补脉冲均分算法,使插补周期中没有闲置的空行程,达到了输出脉冲均匀化的目的。

5 结束语

本研究通过脉冲均分算法,借助同步异构DSP的CPU与CLA协同处理任务的能力,设计了数控系统中用于运动控制的精插补器,实现了插补过程中脉冲的均匀化输出。

该系统硬件与软件结构简单、稳定可靠,可以在不借助外部逻辑电路的情况下(如CPLD、FPGA等),达到与之相同的效率与实时性。

笔者在研究过程中发现该系统还有不足之处,即只在CLA上实现了精插补,粗插补还是由主CPU来完成。因此,在今后的研究中,可以将粗插补器也移植到CLA中,以进一步提高硬件的使用效率与系统的实时性,达到更好的效果。