基于OTP修调功能的芯片量产方法研究

2020-02-25朱少华梁鉴如

朱少华, 梁鉴如

(上海工程技术大学电子电气工程学院, 上海 201620)

1 引 言

近年来,随着集成电路市场的不断扩大,芯片的需求量也日趋增大。由于芯片的功能需求越来越多,集成度越来越高,尺寸不断减小,导致芯片的制造工艺越来越复杂,芯片的某些重要参数在制造过程中会受到一些因素的影响,从而导致芯片良率的下降,增加芯片的生产成本。因此,如何提高芯片的良率使芯片平均成本降低成为一个重要问题。为了保证芯片出货的良率,测试成为集成电路的重要一环。芯片制造受到工艺的影响,一些重要参数会有一定偏差,因此在自动化测试设备(ATE)测试时,需要通过trim code 进行微调。

需要复测的情况有以下两种: 1)可能存在测试机异常导致测试的电压或电流不合格,需要进行复测,如果没有改进算法,此时OTP 也会被重复烧写,让原本可能PASS 的芯片真正失效。2)混料时也会存在重复测的情况。

文献[1]介绍了全搜索的算法,编程时从000 依次搜索到111,找出最接近target 的trim code,这种算法程序比较简短,但是对每个trim code 都要测量电压值,测试时间较长,不利于降低成本。文献[1,2]介绍了一种新颖的算法,认为相邻两个trim code 之间的trim step 差值近似相同,测量值与trim step 有相当好的线性关系,算出初次测量值与target 值之间的trim step 个数,然后进行烧写。文献[1,2]中提出的算法只能用于可重复烧写的修调电路,而且由于trim step 并不是完全线性的,有可能受工艺影响,造成线性度很差。OTP 烧写的特性导致芯片在复测时,再次烧写OTP 会由于误烧写导致芯片失效,因此需要改进烧写策略,进而提高芯片的良率。

对已经烧写的修调位重复烧写会造成芯片失效,需要改进修调算法避免这种情况,从而在复测时不会因OTP 重复烧写造成芯片失效。本文基于ATE 自动化测试平台提出了一种改进的OTP 烧写trim code 的算法,针对OTP 存储单元不能重复烧写的特性,通过修调算法的改进,使得测试时避开已经进行OTP 烧写的芯片,避免重复烧写。

2 修调技术

2.1 修调原理

在芯片生产制造过程中,受到工艺偏差等各种因素的影响,芯片的某些重要参数实际值与设计期望值有偏差。因此在设计芯片时加入了修调电路对参数进行修调,使其符合spec 上的要求。如果没有trim修调,不符合参数的芯片只能被剔除,降低芯片的良率,造成芯片资源的浪费与生产成本的增加[3]。

对于芯片基准电压的修调,主要通过增加电阻来微调电压值。集成电路芯片的主要修调技术就是通过对串联电阻网络进行修调,增大或减小电阻网络的阻值从而改变相应的参数[4]。

如Fig.1 所示是一个电阻网络。实际生产导致实际电阻值偏大或者偏小,为了使生产好的芯片内部电阻符合设计要求的精确阻值,可以通过修调改变开关状态,使电阻串联或者短路,从而改变总电阻的大小[5]。

2.2 OTP 修调

Fig.1 为OTP 修调原理示意图,包含了内嵌存储单元修调电路,每一个电阻都有一个MOS 管与它并联,MOS 管的导通与关断是通过嵌入在芯片中的存储单元的一位存入1 或0 来控制的,常用的存储单元有OTP、EEPROM 等[6]。OTP 为One Time Programmable 存储单元,只可以进行一次编程,编程后就不能再修改,否则会造成芯片功能失效。

普通寄存器在掉电的时候数据就会丢失,而OTP 存储单元写数据时,即使掉电数据也会保留。芯片测试完成后肯定是要掉电的,因此需要用到OTP 存储单元。相比于EEPROM,OTP 需要引入TPAD 修调点,制造工艺相对简单,而且开关的尺寸也对修调精度影响较小。

Fig.1 Schematic diagram of the modulation principle

3 芯片分析

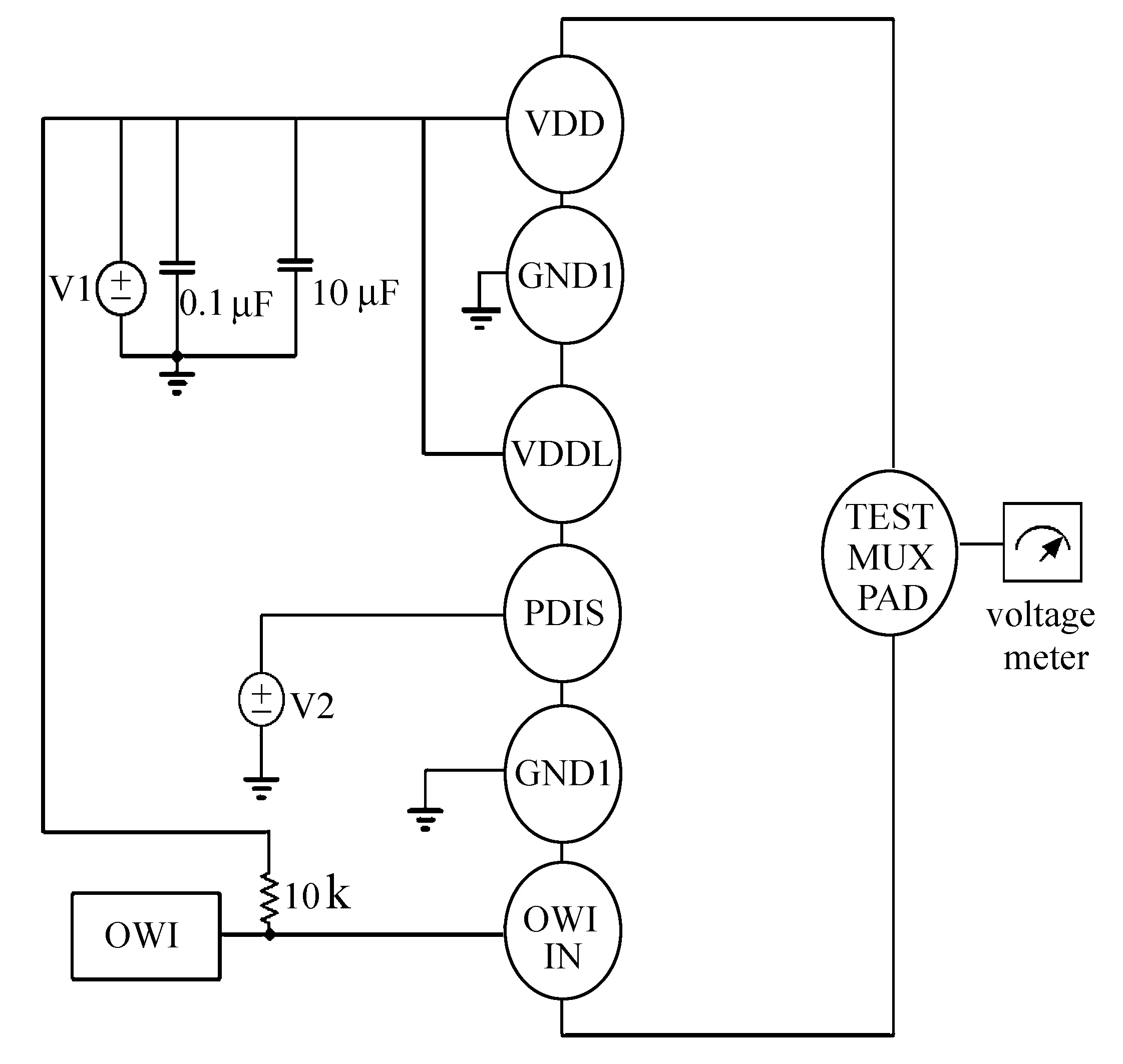

Fig.2 为芯片测试电路图,采用OWI 协议通信。VDD 为芯片供电电源,PDIS 为芯片失能端,通过TEST−MUX−PAD 测试VREF 电压,VREF 电压目标值Target 为807 mV。Table 2、Table 3 为芯片的寄存器表。芯片烧写OTP 步骤如下:

1)进入one-wire 通信模式;

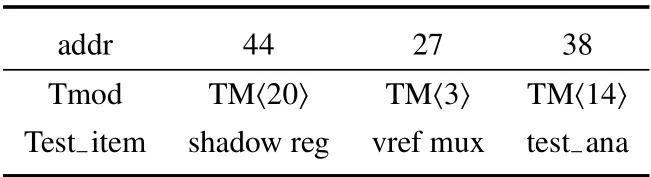

2)使能影子寄存器(TM〈20〉=1),开启基准电压修调(TM〈3〉=1),测试寄存器使能(TM〈14〉=1);

3)设置V1=5 V,测试TEST−MUX−PAD,根据Trim table 计算出最优的code。

Table 1 Register table

Table 2 Adjustment register table

Fig.2 Circuit diagram of chip test

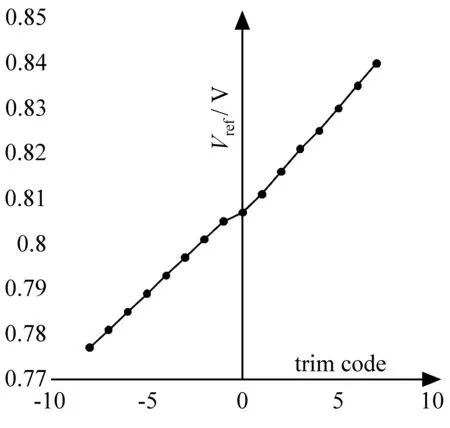

Fig.3 Relationship of chip tuning

4 修调算法

4.1 全局搜索算法

传统算法只适用于可以重复烧写的修调电路,例如EEPROM。得到芯片的预期设计值后,通过trim修调单元,从芯片的修调初始值0000-1111 依次搜索,测量出16 个状态所对应的值来找出修调步长。

全局搜索的算法是对每个trim 状态进行测量,将会大大增加测试时间。因此,文献[2]改进了此算法,可以降低测试时间。文献[2]认为由于trim 电路中电阻的特殊性可以保证相邻的步长s 之间的差值近似相同,通过测量100 颗芯片发现每个trim 状态所对应的值与s 之间呈近似线性关系。文献[2]基于这种关系测量code 值为0000 和0111 所对应的值T0与T7,得出步长值

从而可以求出从T0到目标值Ttarget所需要的步进值

4.2 改进算法

传统方法基于可重复烧写的存储单元,在芯片的原始状态测试参数偏差,计算得出修正值,然后写入存储单元。

改进算法借鉴基于可重复烧写的存储单元的基础上改进算法,使其适应OTP 存储单元。改进算法:1)判断芯片是否烧写过OTP;2)计算出修正值后,先写入寄存器中,测试是否合格,如不合格就微调修正值,再次写入寄存器中并测试之;3)直到合格后再写入OTP。改进算法可以解决以下问题:1)由于电路非线性影响,计算的修正值可能仍有偏差,而OTP 已经写过无法更改;2)由于测试环境、混料等原因需要再次对芯片进行测试时,无法避免重复烧写OTP,造成芯片失效。

如Fig.3 所示为芯片的修调关系,芯片参考电压设计值Ttarget=807 mV。根据文献[2]的算法测试得到修调步进s=4 mV。

修调过程如下:

1)运行pattern,使用capture 功能抓取寄存器的值中可修调位的值,并记录。将抓取的寄存器值转换为十进制,记为Rreg。

2)设置芯片需要的条件,使芯片处于相应的工作状态,测试相关管脚的电气参数,得到实测值,记为Ttest。根据是否在可修调范围判断芯片是否失效。

3)若Ttest大于等于目标值Ttarget,计算需要的十进制code,即

若Ttest小于目标值Ttarget,计算需要的十进制code,即

式中floor 为向下取整函数,得到不大于自变量的最大整数。

4)若Rreg=0,将step 步数dcode转换成二进制trim code,执行5);若Rreg≠0,step 步数为

将dcode转换成二进制trim code,执行6)。

5)将trim code 写到reg−pattern 中的可修调位(寄存器可修调位),运行reg−pattern,并测量管脚的电气参数,判断当前值是否在设计的target 范围内。因为运行reg−pattern 只是将trim code 写入到寄存器中,下电不会保存。因此若没有在target 范围内,微调trim code 值,将新的trim code 写到reg−pattern 中。

6)将trim code 的值写入到OTP−pattern 中,设置只读模式。

7)运行OTP−pattern,先写OTP KEY 进入OTP 烧写模式,再烧写trim code。下电之后再次上电,测量管脚的电气参数,不在target 范围内判断为芯片失效。Fig.4 所示为详细的流程图。

Fig.4 Flow chart of improved algorithm

5 实验数据分析

为了验证该算法的准确性,根据上文所表述的修调算法,在测试机Chroma3380 上编写出相应的程序,测试8000 颗die。将所有的die 分成两批,首先使用常规的方法直接进行OTP 烧写,然后再使用所提出的算法测试,其结果分别如Fig.5、Fig.6 所示。

Fig.5 Test results of wafer NO.1

Fig.6 Test results of wafer NO.2

Table 3 Test results

如Fig.5、Fig.6 所示,PRE−VREF 为修调前的VREF 电压,POST−VREF 为OTP 烧写后的VREF 电压。由图可见,使用这两种方法进行OTP 修调都可以成功。但常规的烧写算法良率低于改进的烧写算法。如Table 3 所示,Wafer NO.1 使用常规算法测试了4000 颗die,有161 颗die 在测试结束之后VREF电压偏大或者偏小,芯片失效,良率95.98%;Wafer NO.2 使用改进算法测试了4000 颗,良率为100%。这是由于OTP 只能进行一次烧写,且常规算法算出的trim code 不一定是最佳值,导致复测时超标,重复烧写造成芯片失效,良率下降。

如Table 4 所示,列出了两种算法测试的5 颗die 的VREF 电压测试时间。由表可见常规方法的测试时间约为170 ms,而采用改进算法测试时间约为200 ms,可以看出改进算法的测试时间比常规方法多了30 ms,但是相比于提高的良率,增加30 ms 的测试时间是完全可以接受的。

Table 4 Comparison of test time

6 结 论

与传统的修调相比,基于OTP 芯片的trim 修调算法可以进行复测,提高测试良率。改进了测试算法,减少了测试的失效率,且测试时间仅多了30 ms。在保证测试时间的情况下,大大提高了测试良率。通过对8000 颗die 测试验证了所提出算法的准确性。