基于WLP-FDTD的带隙电源地平面噪声时域分析

2019-06-05李晓春毛军发

孙 伟,李晓春,毛军发

(上海交通大学 高速电子系统设计与电磁兼容研究教育部重点实验室,上海 200240)

随着电路工作频率的不断提高和供电电压的不断下降,由同步开关噪声和电压降引起的电源完整性问题成为电源配送网络设计中的重要环节.电源配送网络通常以一对电源地平面的形式出现,它为芯片供电,并为信号线提供电流返回路径.在工作频率很高和电源电压很小的电路中,电源完整性分析与设计尤为重要.常用的减小电源地平面噪声的方法有2种:一种是在板间添加去耦电容,通过降低电源地平面间的输入阻抗提高供电电压的稳定性;另一种是通过将电源地平面切分来隔离噪声,这就导致了电源地平面上会出现一些狭小的细缝.因此,准确分析具有带隙和去耦电容结构的电源地平面成为电源完整性设计的重要环节.

高速电路系统中的电源分配网络分析方法可以分为2大类:一类是电磁场分析方法;另一类是等效电路分析方法.电磁场分析方法精度高,但效率低.文献[1]中使用时域有限差分算法(FDTD),分析电源地平面特性,该方法是一种全波方法但是算法的时间步长受限制于稳定性约束条件.文献[2]中使用非连续伽辽金时域法提取电源地平面对的散射参数,该方法同样是一种显式时间步的方法,并且在求解每个单元阵所需要的消耗比较大.文献[3]中使用镜像方法提取电源地平面的阻抗参数,该方法是一种解析方法.它将地平面的四周等效成理想磁壁边界(PMC),将待求解端口镜像到区域外,但是这种方法只适用于规则电源地平面.

等效电路方法通过提取电源地平面的等效电路参数,包括电阻(R)、电感(L)、电导(G)和电容(C)参数,来分析电源地平面电路的噪声特性,具有效率高的优点.针对电源地平面的等效电路模型,文献[4-5]中引入基于加权拉盖尔多项式-时域有限差分(WLP-FDTD)方法分析电源地平面的电源完整性.WLP-FDTD算法不受FDTD稳定性条件约束,是一种无条件稳定的时域方法[6-7].因此,相比FDTD方法,WLP-FDTD具有效率高的优点.近年来,WLP-FDTD方法也被应用于均匀传输线[8]、非均匀传输线[9].文献[4]中分析了一个理想的完整电源地平面.文献[5]中考虑了去耦电容的影响,但未考虑电源地平面的带隙结构.文献[10]中提出一种基于谐振腔和传输线理论的SPICE模型来分析电源地平面的阻抗特性.在此基础上,文献[11]中提出了一种场路结合的方法分析带隙电源地平面的散射参数特性.这2种方法在求解电源地平面中均采用了电磁场数值方法,但场的求解过程中均没有考虑金属平面寄生电阻的影响.

本文使用无条件稳定的WLP-FDTD方法分析带隙电源地平面的噪声传播问题.WLP-FDTD方法以加权拉盖尔多项式为基函数,通过伽辽金法消除时间变量,从而使算法不再受到稳定性条件约束.与传统FDTD算法相比,该方法可以选择任意的时间步长,解决了由于计算单元尺寸变小带来的计算效率低问题.相比于文献[6-7]中采用WLP-FDTD方法分析规则的电源地平面结构,本文考虑了电源地平面的带隙结构和去耦电容,在电源地平面的电路模型中引入带隙的等效耦合电路模型,并且将去耦电容应用到等效电路中,拓展了WLP-FDTD在电源地平面的应用,实现了基于WLP-FDTD方法的带隙和去耦电容电源地平面的噪声传播分析.计算结果表明,本文提出的基于WLP-FDTD的带隙电源地平面噪声分析方法与FDTD方法具有相同精度,但计算效率有显著提高.

1 带隙和去耦电容电源地平面的建模

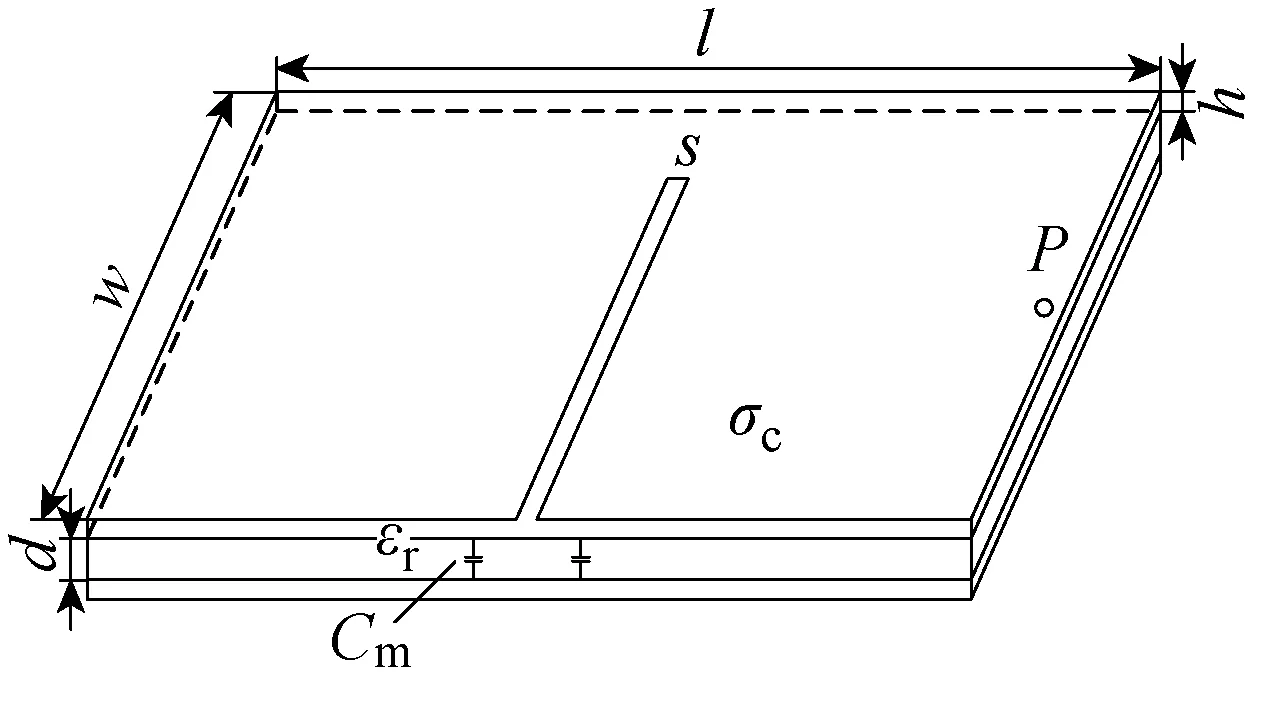

图1所示为一典型具有带隙和去耦电容的电源地平面结构,上下表面由大片金属分别组成电源平面和地平面,中间为填充介质,去耦电容Cm连接在两块金属板之间,带隙位于电源平面上.图中:w和l分别为电源地平面的宽度和长度;h为金属层的厚度;d为介质层的厚度;s为缝隙的宽度;εr为填充介质的相对介电常数;σc为金属的电导率,P为输出点.带隙电源地平面结构可以看作由两部分组成,即平面部分和带隙部分,分别对这两部分进行建模.

图1 具有带隙和去耦电容电源地平面三维结构Fig.1 The 3-D geometry of power/ground planes with slots and decoupling capacitors

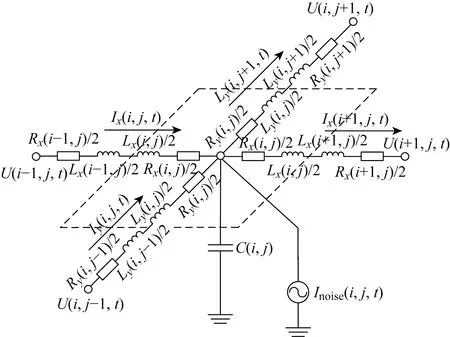

将无隙电源地平面等效为二维RLGC传输线模型,即分成M×N个单元,板内介质损耗可以忽略,即G=0,因此每个单元由RLC电路组成.图2所示为电源地平面单元模型.图中:Inoise(i,j,t)为外部噪声源(i=1,2,…,M;j=1,2,…,N).单元中x和y方向的电容、电感、电阻分别为[7]

C(i,j)=ε0εrmn/d

(1)

Lx(i,j)=μ0dm/n

(2)

Ly(i,j)=μ0dn/m

(3)

(4)

(5)

式中:m和n分别为单元(i,j)在x和y方向的长度;ε0和μ0分别为自由空间的介电常数和磁导率.

图2 电源地平面单元模型Fig.2 The circuit model of power/ground planes

根据基尔霍夫电压电流定律,点(i,j)处沿x和y方向的电流和该点的电压之间的关系[5]为

U(i,j,t)-U(i+1,j,t)=

(6)

U(i,j,t)-U(i,j+1,t)=

(7)

Ix(i,j,t)-Ix(i+1,j,t)+Iy(i,j,t)-

Iy(i,j+1,t)+Inoise(i,j,t)=

(8)

Inoise(i,j,t)表示该位置的电流噪声.

由于d通常很小,远小于电路中工作的波长,平面边缘可被视为开路,边界被等效为理想磁壁边界.因此,电源地平面的边界条件可以表示为[5]

Ix(1,j)=0

(9)

Ix(M+1,j)=0

(10)

Ix(i,1)=0

(11)

Iy(i,N+1)=0

(12)

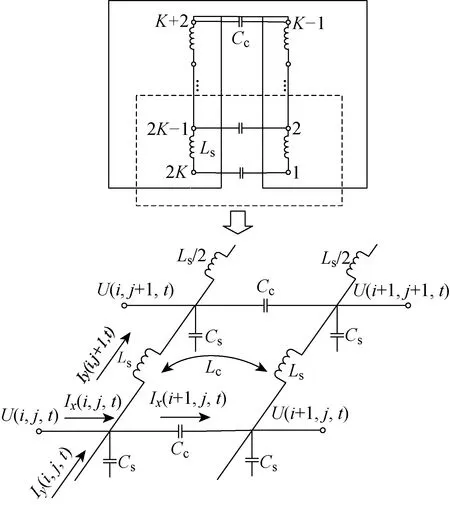

电源地平面工作在高频段,带隙之间的耦合效应不能忽略,因此带隙部分也需要精确建模.带隙周围会激发电场和磁场,电场和磁场的耦合效应分别可以用电容和电感表示[10-11].因此,可将带隙部分等效成耦合电路,如图3所示.耦合电路包含2K个节点,K的大小与带隙长度有关,每个单元的自电容Cs、耦合电容Cc、自电感Ls、耦合电感Lc[10-11]为

(13)

(14)

(15)

(16)

式中:Ce和Co分别为偶模等效电容和奇模等效电容;上标a和d分别表示空气和介质下的电容,文献[11]中给出了2种模式下电容的计算公式.

图3 带隙部分的等效电路Fig.3 The equivalent circuit of slots

通过带隙结构的耦合等效电路,可以将带隙和平面级联.假设节点(i,j)位于带隙等效电路的某个节点处,令相应的镜像节点位于(i+1,j)处,这样就建立起两个相邻平板间的联系,带隙部分的电压和电流关系为

(17)

U(i,j+1,t)=

(18)

Ix(i,j,t)-Ix(i+1,j,t)+Iy(i,j,t)-

(19)

基于等效电路方法可以很方便地处理电源地平面中具有去耦电容的情况.网格剖分的时候,选择将节点应用到去耦电容处.对于存在耦合电容的节点处,式(8)可以替换为

Ix(i,j,t)-Ix(i+1,j,t)+Iy(i,j,t)-

Iy(i,j+1,t)+Inoise(i,j,t)=

(20)

2 应用WLP-FDTD求解

不同于传统的FDTD算法,本文采用WLP-FDTD方法分析带隙电源地平面噪声的瞬态响应.WLP-FDTD方法引入拉盖尔多项式,并利用多项式加权正交性构造一组正交多项式组成基函数[6]

φp(st)=e-st/2Lp(st)

(21)

式中:s为时间尺度因子.基函数具有正交性:

(22)

利用这组基函数,电压电流可以展开为

(23)

(24)

(25)

以式(23)为例,对时间的一阶微分可以表示为

(26)

式中:W(t)为平面任意位置的电压或电流.

将式(26)代入式(6)、(7)和(17)~(20),可得

(27)

(28)

(29)

(30)

(31)

(32)

在式(27)~(32)的两边乘以φq(st)并在st=[0,∞)积分,可得

(33)

(34)

0.5s(C(i,j)+Cc)Uq(i,j)+

(35)

(36)

Uq(i,j+1)=Uq(i,j)+(Ls-Lc)×

(37)

(38)

(39)

无穷积分上界可以用噪声持续时间Td代替.边界条件式(9)~(12)可以表示为

(40)

(41)

(42)

(43)

电源地平面中的电压电流关系为式(33)~(35),带隙部分的电压电流关系为式(36)~(38),边界条件为式(40)~(43).根据式(33)~(38),将q-1阶项和噪声项移到等式右边,整理可以得到电源地平面的电压电流矩阵形式:

AWq=Inoise+bq-1

(44)

(45)

可以看出,式(44)右边的阶数低于左边,因此从q=0 开始求解,采用递归方法求解式(44),可以计算出电源地平面上的电压电流值.此外,A与阶数q无关,因此整个迭代过程中只需要在计算开始时对矩阵A求逆一次.

式(33)~(38)的求和上界q通常用有限值Q来代替.Q值的大小对计算精度和计算时间都有影响,虽然Q值越大,计算精度越高,但消耗的计算时间也越多,因此需要选择合适的Q值.假设电路中工作的信号带宽有限,截止频率为fB,则有[5]

Qmin=2fBTf+1

(46)

式中:Tf为信号的时间周期.

3 数值结果

采用2个带隙电源地平面结构作为算例,验证所提出的基于WLP-FDTD算法的计算精度与效率.

算例1不带去耦电容,平面尺寸为50 mm×50 mm,带隙位于电源平面的中心,带隙尺寸为 0.5 mm×20 mm,中间介质厚度为 0.05 mm,相对介电常数为 4.2,金属层厚度 0.018 mm.平面左侧存在噪声电流,其形式为正弦调制的高斯脉冲

Inoise(t)=

(47)

式中:Td=fc/2;Tc=3Td;fc=1 GHz.高斯脉冲的周期Tf=11.71 ns,截止频率fB=5 GHz,代入式(46)得Qmin,本文中Qmin值选取为120,K值选取为20.通过考察如图1所示右侧边缘中心P点的电压来分析噪声对平面性能的影响.当采用FDTD方法分析该问题时,由于FDTD受稳定性条件约束[6],时间空间步长必须满足

(48)

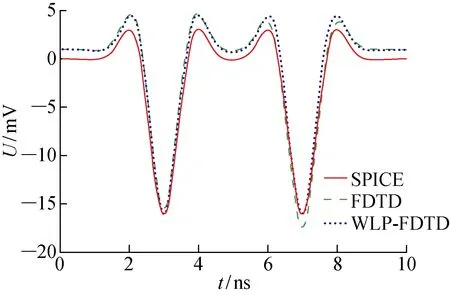

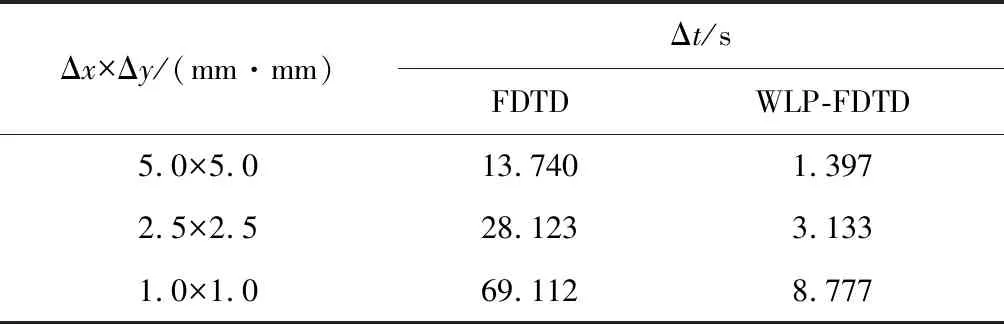

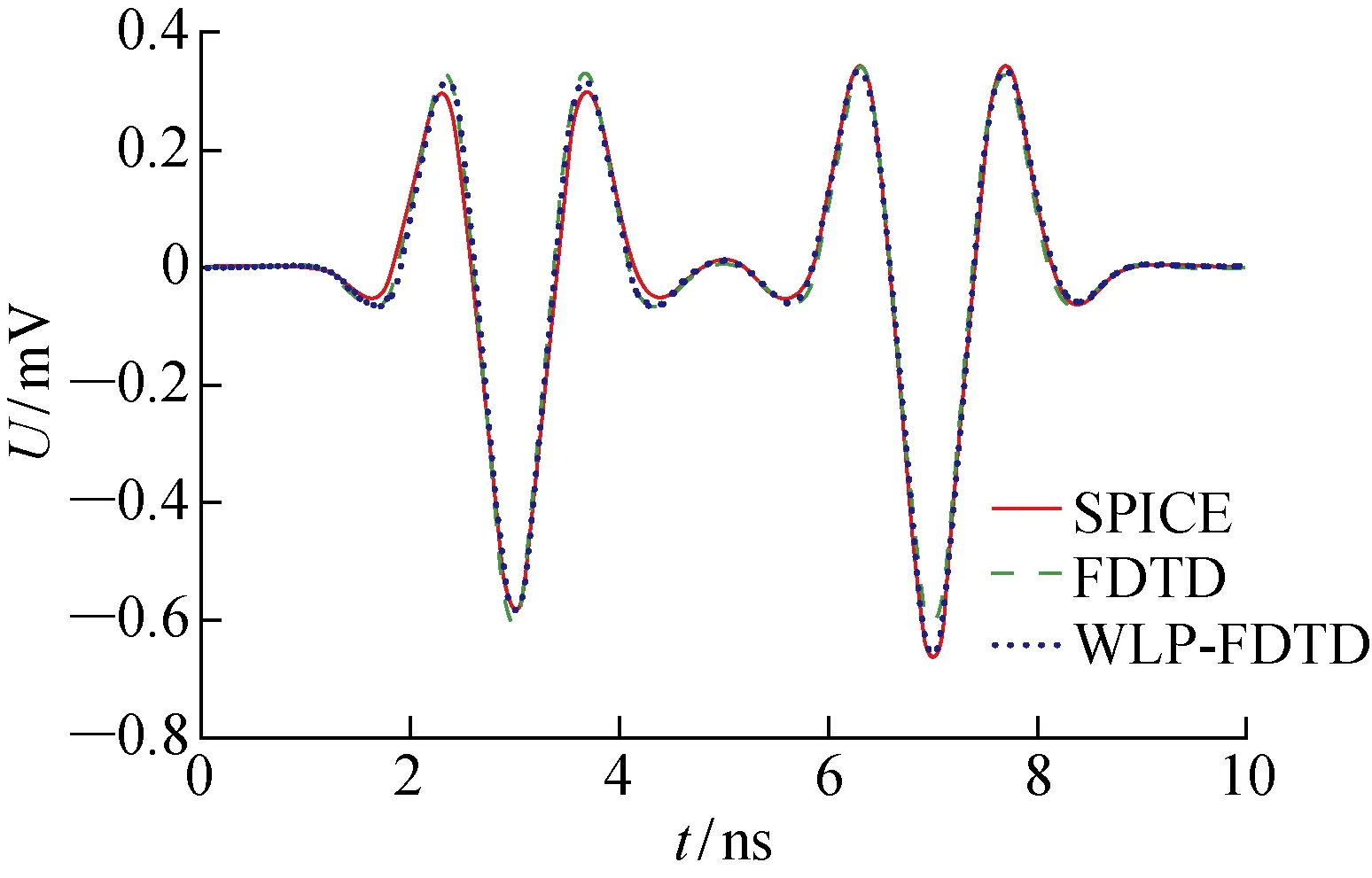

式中:vmax为介质中最大相速;Δx和Δy分别为x和y方向的网格尺寸.当网格尺寸选择1 mm,FDTD的时间步长必须小于 2.357 ps.图4给出了SPICE仿真软件结果、FDTD和WLP-FDTD算法的计算结果.可以看出,三者几乎完全吻合,验证了WLP-FDTD方法的准确性.针对算例1,表1给出了FDTD和WLP-FDTD的计算时间对比,仿真高斯脉冲的周期数为20个.由于WLP-FDTD没有时间步长影响,因此计算效率远高于FDTD.

图4 未加去耦电容的电源地平面中P点电压Fig.4 The output voltage of the power ground planes without coupling capacitor at the point P

表1 算例1计算时间对比Tab.1 Comparison of computation time of the 1st example

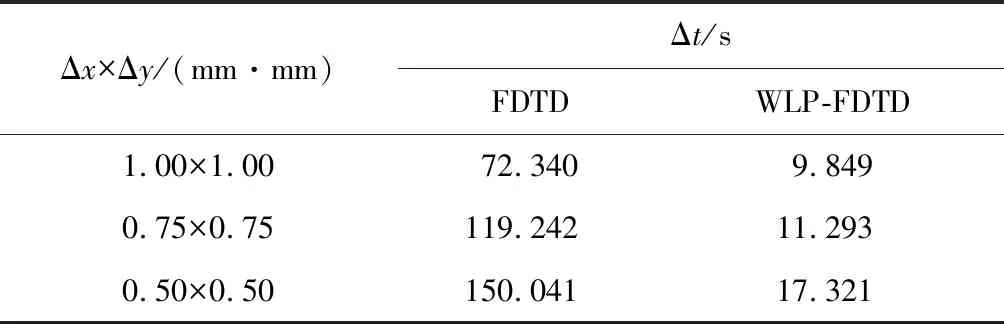

算例2平面尺寸与算例1相同,增加了2对去耦电容.去耦电容之间的间距为2 mm,分别位于带隙两侧和输出点P的两侧.去耦电容为10 pF.由于每对去耦电容的间距较小,网格划分比较密,网格尺寸最大为1 mm×1 mm,此时FDTD的时间步长必须小于 2.357 ps.图5给出了SPICE软件、FDTD和WLP-FDTD对算例2的仿真计算结果.可见,三者具有极高的吻合度.表2给出了相同空间步长情况下FDTD和WLP-FDTD对算例2的计算时间,仿真高斯脉冲的周期数为20个.可见,WLP-FDTD算法的计算效率远高于FDTD算法,且其优势随网格划分密度的增加而更加显著.

图5 添加去耦电容的电源地平面中P点电压Fig.5 The output voltage of the power ground planes with coupling capacitors at the point P

表2 算例2计算时间对比Tab.2 Comparison of computation time of the 2nd example

4 结语

本文基于一种无条件稳定的WLP-FDTD时域有限差分算法,分析带隙电源地平面中噪声的传播问题.首先,基于电源地平面的等效电路模型和带隙的等效电路模型建立电路方程;然后采用WLP-FDTD方法求解方程,从而得到复杂电源地平面结构噪声传播的瞬态响应.理论与实验结果证明,与传统FDTD方法相比,WLP-FDTD方法能够实现无条件稳定,因此在分析复杂结构电源地平面噪声时可以显著提高计算效率.