基于FPGA的非压缩高清视频光纤传输关键问题研究

2019-04-11成海龙刘艳明

严 枫 成海龙 刘 涛 刘艳明 乔 鑫

(驻218厂军事代表室 北京 100000)

0 引言

随着工业用及商用对视频清晰度及分辨率要求的不断提高,视频格式从低的600×480的分辨率发展至目前的超高清的4K级乃至8K级。这些剧增的视频数据给传输应用带来了巨大的挑战[1-2]。例如,当视频格式为4K级时,如以RGB4:4:4传输,帧率为60帧/秒,每个像素为8bit灰度等级,则一路视频的有效最大数据速率为14.4Gbps。直接以网络或者应用电缆的HDMI(High Definition Multimedia Interface)或者DP(DisplayPort)方式传输距离有限,现有应对长距离传输的方法可以采用基于H.265或者H.264的压缩/解压,通过以太网传输,或者基于FPGA(Field Programmable Gate Array)和光纤的方式进行无损非压缩传输后直接恢复[3-5]。两者相比较,后者由于采用非压缩实时传输方式,对原有视频无任何损失,且具有较小的时延及数据抖动,因此在视频质量要求高的场所应用较广泛。

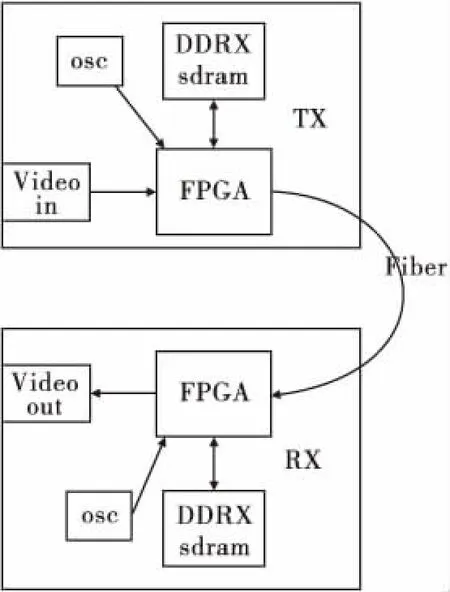

现有基于FPGA及光纤的高清长距离非压缩视频传输的方案模型可如图1所示。

图1 非压缩光纤视频传输方案架构图

方案架构中TX为发送端,RX为接收端。其工作流程为:在发送端,超高清视频流(Video in)输入至FPGA中,FPGA在时钟晶振OSC(oscillator)的驱动下,对视频流的数据进行缓存处理,存储至DDRxSdram(Double Data RateSynchronous Dynamic Random Access Memory,x为0-4) 并同步读出,通过其自带的高速串行数据口连接至高速光模块进行发送;在接收端,高速光模块接收带视频流数据的光信号,转换为高速电信号输入至FPGA高速串行数据口,FPGA对信号进行解码,得到视频流数据存储至DDRxSdram。并同步读出视频数据,后在OSC的驱动作用下,恢复原有的视频格式,输出视频流(video out),便于后续处理。

本文在研究这个方案传输机制的基础上,针对其中的几个关键技术问题,给出了解决方法,实现高效传输。其一是超大视频流数据存储访问带宽计算及带宽分配调度策略;其二是视频帧间动态同步及失步应对方式;其三是时钟重建及视频格式恢复方法。

1 超大视频流数据存储访问带宽计算及带宽分配调度策略

视频流数据进入FPGA后,在对输入/输出数据速率、系统内部带宽及外部存储器带宽进行计算后,可采用更高速度的存储器,并采取有效的调度策略,以此达到数据延迟时间短、资源利用率最高,系统性能最优的目的。

首先对所需的各个环节带宽进行计算,得到理论值。系统带宽计算结构可如图2所示。

图2 系统带宽计算示意图

图2中fifo为先进先出(first-in-first-out),fifoin1至fifoin n为多路输入视频缓存区,fifo out为视频数据输出缓存区。BWin1至BWin n为读取输入视频所需带宽,BW out为视频输出带宽,即为光纤传输的固定带宽,BW wr为写入外部存储器的所需带宽,BW rd为读取外部存储器的所需带宽。在给定的存储器条件下,其整体带宽BW sdram为

BWsdram=BWwr+BWrd

(1)

给定视频输入总带宽为

BWin=BWin1+BWin2+…+BWinn

(2)

为满足视频输入数据不丢失要求,BW wr 必须大于或者等于BWin;且为达到光纤通道带宽最有效利用的要求,BW rd必须大于或者等于BW out。BW rd与BWin无必然联系,一般在视频流无停顿及实时性的要求下,接收端输出视频显示正常时,BW out的基本指标必满足输出视频格式的24帧/秒以上,即BW rd≥BW out≥输出帧频24帧/秒。

按照上述视频流数据计算所需带宽后,实现带宽最大利用率上需要考虑两个方面。其一是FPGA内部数据高速获取。在上述要求下,多路视频输入时,需要满足在一个固定周期T内,每路输入视频数据均需至少读取一次。为此,在给定外部存储器的物理条件下,执行实现机构设计上最直接也是最有效的方法就是采用多层次存储结构(Cache)进行视频数据缓冲。其原理是依据分时复用或者分空间复用性,不断刷新读写数据,使得内部功能单元能快速得到连续数据,可大为提升系统内部数据读写性能。具体实施上,需要考虑极限条件(读写数据最大速率)以及视频格式,从而在资源利用最有效的情况下,决定Cache缓冲多少行视频数据。Cache实现一般可采用FIFO或者片内RAM(Random Access Memory)。

其二是FPGA与外部SDRAM之间的数据读写最优方法。在操作现有的外部各类型大容量高速存储器SDRAM的过程中,由于总线资源天然的共享限制,其读写操作必然存在冲突。为有效解决此类冲突,在设计中,采用令牌环调度方式(Round-Robin Scheme)或者固定优先级调度方式(Fixed PriorityScheme)。两者各自存在自身的优缺点,前者带宽均衡分配,存在延迟等待,浪费带宽等问题。后者无延迟问题,会出现高优先级抢占低优先级的情况,导致低优先级通道数据可能丢失。为解决这些问题,综合两者优点,采用基于单时钟条件下的动态总线竞争和Cache缓存相结合的方式。在每个时钟的边沿,读写调度逻辑控制器侦测当前总线归属状态,以及每路视频数据Cache空满缓存情况,依次分配下一个时钟的总线控制权。例如其中某路视频输入数据写入SDRAM调度用逻辑语言可表示为:

IF(第1路输入视频缓存空 == 真 )且(第2路路输入视频缓存空 == 真)且(第3路输入视频缓存空 == 假 ) 且(第3路输入视频写允许==真 )且(当前写SRAM状态 == 真 ),此时选择满足条件的第3路输入视频数据写入SDRAM。读写调度逻辑控制器从第3路的Cache中读取数据写入SDRAM,且考虑SDRAM本身的读写效率,一般可选用行触发方式。当第3路输入视频数据写入SDRAM的数据数量计数比SDRAM一行数据数量少1时,第3路输入视频写允许为假,第3路输入视频数据放弃总线控制权,控制权移交给其它数据通道。如其它通道满足类似条件,其就获得总线权;如有多个通道满足条件,由于存在Cache缓存,后响应的通道数据不会丢失,只是响应滞后,此时Cache缓存容量需要满足最长时间访问要求;如都不满足条件,总线浪费的带宽所用时间为通道数乘以时钟数,依据此方式,SDRAM总线控制调度可获取最高带宽利用率。

2 视频帧间动态同步及失步应对方式

输入视频在传输中总是会存在输入视频源断开、光纤断开以及输入端电路断电等各种断路情况,导致从发射端传输至接收端的视频为不完整的一帧图像。而断路情况恢复正常后,接收端需要得到完整的帧图像,且在接收端接收到的视频数据为无限长的数据流,需要从数据流中分割出独立的每帧图像进行缓存、处理及显示。解决这些问题需要采取视频帧间动态同步方法。现有帧同步实现方法有两种:一种是插入标志帧同步法;另一种是利用间隔固定时隙插入固定位同步的方法实现。如图3所示,本文采用第一种方法并对输入视频的格式进行编码,形成固定长度的标志同步码。

图3 帧同步示意图

建立同步码需要考虑如下几个问题:

1)同步码长度与误码率的关系。由于视频数据样本量大,若选取同步码长度短,出现视频数据与同步码一样的概率大。在极限条件下,参考KRONE误码率标准10E-12,即零误码率标准,其倒数换算成十六进制为0X0E8D4A51000,长度为40位二进制。选取同步码长度可为40位以上,当选取40位以上长度的同步码后,出现视频数据本身与同步码一致的概率接近于0。

2)码字选取。确定同步码长度后,选取码字参照8421编码方式以及满足信号线路均衡需要,选择同步码为“0XAA55F0F08421”。

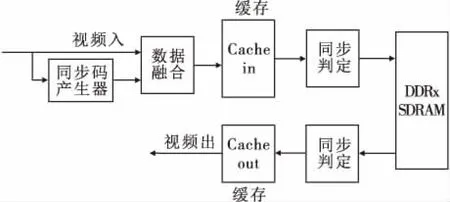

3)在FPGA内部的同步实现上,建立如图4所示的缓存输入输出均同步的同步机制。

图4 同步机制

在发送端视频输入的同步判定中,当且仅当检测到同步码时,从缓存cache in中得到的第一个输入视频数据(可以是RGB4:4:4或者YCrCb4:2:2格式)写入至SDRAM中本路输入视频定义的初始地址,后续依次从缓存cache in读取数据写入SDRAM。依此方式至下次检测到同步码,重复开始写入新的一帧输入视频数据。从SDRAM中读出视频数据传输给缓存cache out时,依旧是当且仅当检测到同步码,下一行(SDRAM获取数据按行突发方式)读取的地址必为本路输出视频定义的初始地址。

在接收端视频数据的同步判定中与发送端处理一致,只是当同步码丢失后,必须能够重新同步。本文中采取的方式为,设定一个固定时间(该时间应长于2帧图像间隔时间),在此时间内无同步码出现,清除输入cache in缓存的数据,写入SDRAM的地址清零至初始地址,从而确保完整的一帧图像输入至接收端的缓存cache in中。由此机制及按带宽计算的要求,可在满足实时视频数据的输入与输出速率需要的同时,极大降低了视频数据帧误码率,解决上述文中所提及的各种输入视频数据断路问题,提高了视频输出显示的稳定性。

3 时钟重建及视频格式恢复方法

按行业内视频各种格式标准,视频输入端的分辨率格式可从640×480@50Hz至4096×2016@60Hz,时钟频率从25MHz至297MHz,涵盖几十种格式及频率,而视频输出端不能通过其他有效方式获知发送端视频格式,但同时需自动输出相同视频格式。为满足此要求,本文给出一种编码及自适应的方法。步骤为:

首先在发送视频输入端进行格式编码。参照图4,在视频发送端,同步码发生器通过计数检测视频输入行的有效像素个数、一帧中行的行数目及一帧的场同步间隔时间,从而可确定输入视频格式。获知格式后,采用8bit对视频格式进行编码,例如,0×01表示为640×480@50Hz,0×02表示为640×480@60Hz,…,0×0FF表示为4096×2160@60Hz。其可表示的格式类别为256种,能够满足现有绝大部分视频格式。格式编码完成后,此编码数据与视频输入数据融合一起写入缓存cache in。

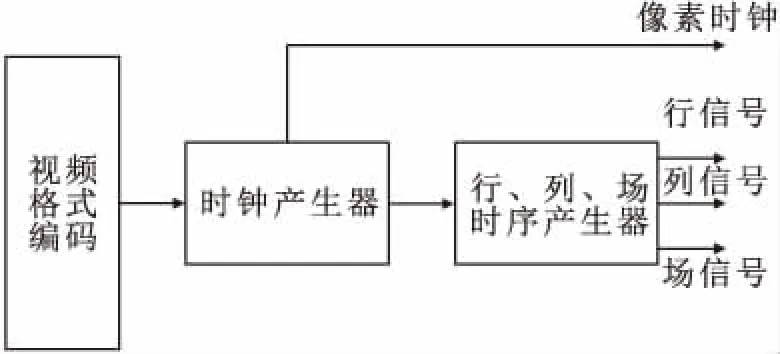

其次在接收视频输出端进行解码及恢复视频格式。上述编码一直随视频数据进行缓存、写入SDRAM及传输至接收端输出。当接收端从SDRAM读出视频数据输出至缓存cache out时,视频数据同步判定完成后,可获取当前的视频格式编码。得到格式编码,需恢复视频格式。恢复视频格式的过程包括产生输出视频像素时钟及行、列、场同步信号,如图5所示。其中重点为产生合适的输出视频像素时钟,现有的产生方式有FPGA片内产生及片外专用芯片(ASIC)产生。图5中产生的行信号作为读取缓存cache out的有效使能信号,在像素时钟及行、列及场信号的作用下,读取视频数据输出直接显示。

图5 视频格式恢复示意图

4 实验验证

为验证本文中所提出方法的可行性,设计如图6所示的实物进行验证。实物设计采用了Xilinx公司的Spartan6中的XC6SLX45器件及二片外置SDRAM。采用了ChipScope工具在线进行数据及时序观测,观测的结果如图6所示。

图中的数据获取结果表明,带宽的调度及同步码的方式能够满足要求。

最后,进行光纤视频的传输,传输的视频格式为1920×1080P,视频输出显示结果如图7所示。并经过长时间连续测试,视频输出无抖动,无像素缺失;在接收端进行断电,光纤拔插,视频均能自动恢复。

5 结束语

非压缩的高清或者超高清视频光纤传输方式与采用直接电缆方式、压缩传输方式或者网络传输的方式比较而言,在延长视频传输距离及保障视频质量方面具有一定的优势。本文在基于FPGA电路的基础上,对大容量视频数据的光纤传输的方法进行了较为深入的讨论。对其涉及的几个主要问题,如带宽的计算及调度、帧同步机制的建立与实现以及视频格式的自适应恢复等提出了解决方法。后进行了电路实物设计验证,验证的结果实现了视频长时间稳定透明传输,表明文中所提方法具有可行性,并可为未来需要高质量视频如超高清8K级或者其它方式的光纤传输提供了一条路径。