SOI工艺抗辐照SRAM型FPGA设计与实现

2018-10-13罗家俊刘海南李彬鸿吴利华刘忠利高见头孟祥鹤韩郑生

郝 宁,罗家俊,刘海南,李彬鸿,吴利华,于 芳,刘忠利,高见头,孟祥鹤,邢 龙,韩郑生

(1. 中国科学院大学,北京 100029;2. 中国科学院微电子研究所,北京 100029;3. 中国科学院硅器件技术重点实验室,北京 100029)

0 引 言

随着半导体制造技术的发展,现场可编程门阵列(Field Programmable Gate Array, FPGA)电路的集成度、逻辑规模大幅提高,电路架构和可配置资源不断优化,应用领域也随之拓展。SRAM型FPGA电路因其具有灵活的可重复编程特性和快速产品化特性使其不仅在集成电路初始设计中被大量使用,在消费电子、通信、军事和航天等领域也得到广泛应用。目前,针对SRAM型FPGA电路在恶劣工作环境,特别是在航天[1]、核辐射等复杂电离环境下的应用引起广泛关注[2-7]。商用SRAM型FPGA多采用体硅工艺的非加固设计,工艺自身的特点使其工作在恶劣电离环境下可靠性大幅降低,面向FPGA设计和工艺的辐照加固技术在应用需求的牵引下被不断提出。

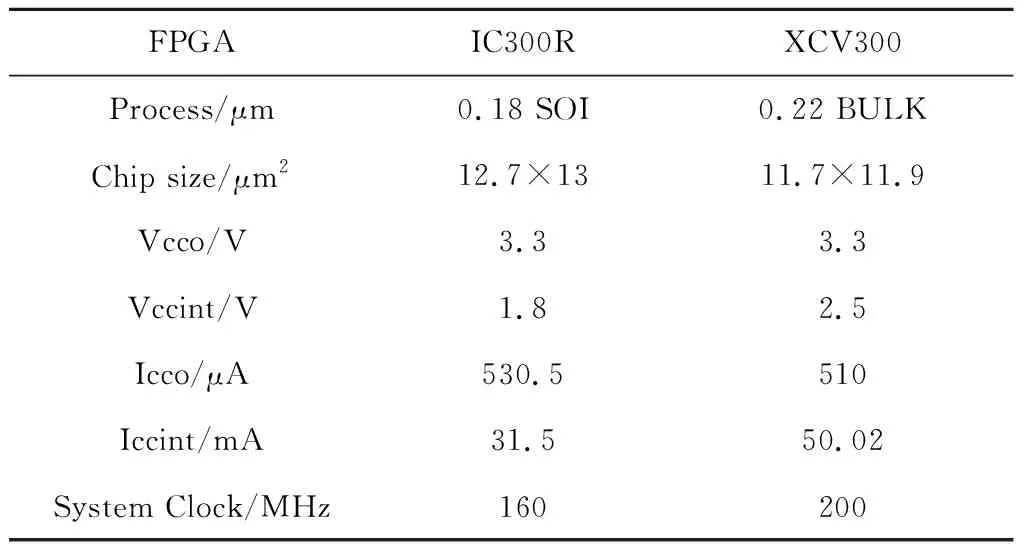

国内外多家机构已开展抗辐照FPGA电路的研发工作并形成系列产品,其中具有代表性的如Xilinx公司宇航级FPGA电路XQR4VSX55,配置存储器单粒子翻转饱和截面为4.37×10-8cm2/bit,块存储器单粒子翻转饱和截面为4.19×10-8cm2/bit。国内某设计公司开发的规模为55K逻辑资源的高可靠FPGA电路,配置存储器单粒子翻转饱和截面为1.05×10-8cm2/bit,块存储器单粒子翻转饱和截面为4.20×10-7cm2/bit。某航天研究所研制的百万门级高可靠FPGA系列产品,其典型产品300万门级FPGA配置存储器单粒子翻转阈值大于15 MeV·cm2·mg-1,抗总剂量水平为100 krad(Si)。显然FPGA电路的抗单粒子翻转能力除了受限于逻辑规模和特征尺寸外,体硅工艺在抗单粒子翻转能力方面的局限性也是无法回避的因素。

SOI MOS器件制作在隔离层上的硅岛中,因其全介质隔离有效消除背面寄生晶闸管,同时减小PN结面积和器件寄生电容等优点,在抗单粒子锁定和单粒子翻转方面有其先天优势[8]。因此,基于SOI工艺的抗辐照FPGA电路研究也是当前集成电路领域的一个重要研究方向。

本文基于0.18 μm SOI CMOS工艺实现一款30万门级抗辐照FPGA—IC300R电路,该款FPGA的逻辑规模和可配置资源与Xilinx公司的XCV300型FPGA[9]近似。

本文的组织结构如下:第1节IC300R电路架构介绍;第2节重点阐述IC300R电路的单粒子翻转加固设计方法;第3节列举了IC300R FPGA的电路特征;第4节为电路的电参数和抗辐照性能指标;第5节为总结和结论。

1 IC300R FPGA架构设计

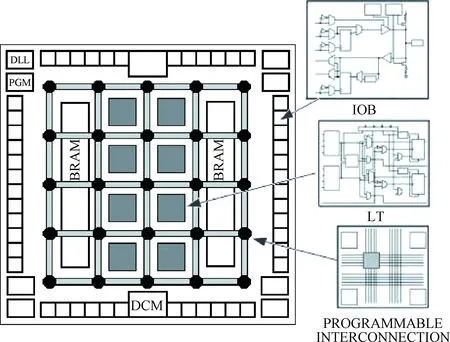

IC300R FPGA电路的可配置资源以逻辑块(Logic Tile, LT)为主,整体电路架构由图1所示。电路主要由以下模块组成:LT、数字时钟管理模块(Digital Clock Manager, DCM)、64k位存储容量的块存储器(Block RAM,BRAM)、4个可编程管理模块(Programmable Manager, PGM)以及可编程输入输出模块(Input Output Block, IOB)。

图1 IC300R FPGA架构示意图Fig.1 IC300R FPGA architecture

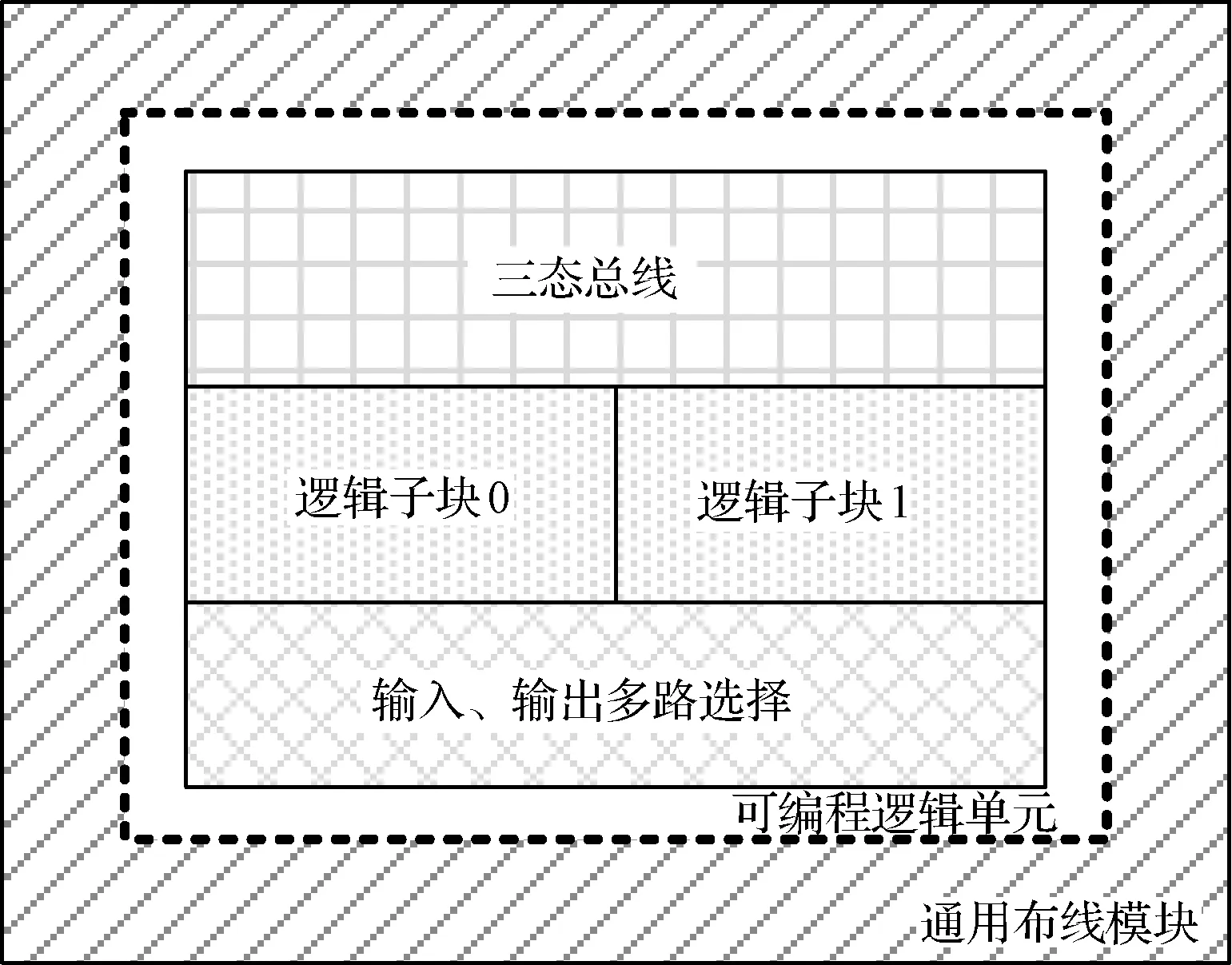

IC300R FPGA芯片面积的65%由逻辑块组成,共1536个逻辑块呈32行、48列矩阵排布,其结构示意图由图2所示,每个逻辑块由1个可编程逻辑单元(Configurable Logic Block, CLB)和1个通用布线模块(General Routing Module, GRM)组成。

图2 逻辑块(LT)结构示意图Fig.2 LT architecture

可编程逻辑单元包含3种电路模块,分别为逻辑子块、三态总线和输入、输出多路选择电路,通过配置实现查找表、乘法器和进位等逻辑功能。通用布线模块是可编程逻辑单元的布线资源,由单倍线、长线和16倍长度线三种类型连线资源,通过对通用布线模块编程实现预期的互联方式和逻辑功能。

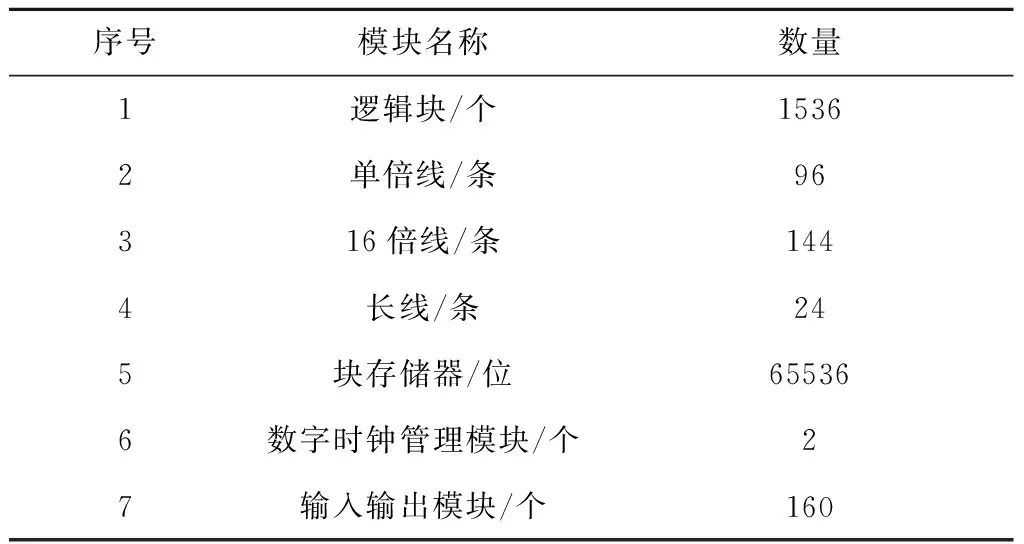

表1 IC300R FPGA架构参数Table1 Architecture parameters of IC300R FPGA

2 辐照加固设计

SRAM单元作为位流文件和运算数据的临时存储节点广泛分布于SRAM型FPGA电路中,该单元在单粒子事件敏感性方面有其结构上的弱势,其中比较关键的影响是配置存储器的单粒子翻转事件[10]。业内同行已对FPGA单粒子翻转加固技术进行了大量的研究,提出许多不同的加固方法,主要有以下三种:1)采用三模冗余技术(Triple Modular Redundancy, TMR),利用硬件备份关键数据实现加固效果[11-12];2)采用时序冗余技术,利用两路相互之间存在延迟的时钟,对单粒子入射产生的瞬时脉冲进行屏蔽[13];3)采用位流文件刷新技术(Scrubbing),通过不断写入配置信息抵御翻转风险[7,14-15]。并在此基础上衍生出许多类似的加固方法[16-19]。

上述方法在实现过程中,首先要面对的问题是芯片面积和功耗的增加,如三模冗余技术需三组相同的存储电路配合表决电路实现,面积为非加固方案的三倍以上,电路待机功耗也随之呈线性增加。其次是与加固方法相配合的硬件模块自身的加固问题,硬件模块不具备足够的加固能力,在辐照条件下并不能正常实现加固性能。为提升IC300R FPGA的抗单粒子翻转性能,电路设计采用辐照加固设计技术(Radiation Hardened by Design, RHBD)和辐照加固工艺(Radiation Hardened by Technology, RHBT)相结合的加固方法。

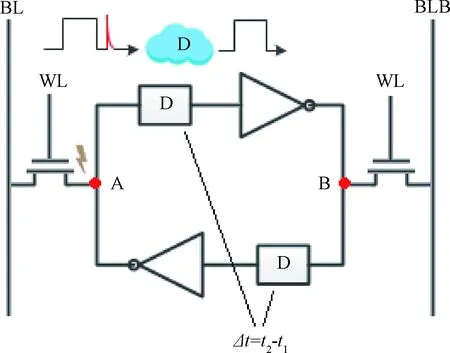

SRAM型FPGA电路中块存储器和配置存储器均采用SRAM单元结构是辐照加固的关键模块。SRAM单元通过反相器交叉反馈的方式存储数据,当高能粒子射入存储节点产生的电荷超过存储单元翻转的临界电荷时,会将原有的数据改写,造成FPGA电路功能中断或存储数据改变。大量研究表明,通过在SRAM单元交叉反馈回路中通过加入电阻、电容等延迟器件,增大两个存储节点之间数据变化的响应时间差,是提高SRAM单元单粒子翻转性能的有效技术[20-22]。

在IC300R FPGA电路中我们采用了一种脉冲屏蔽加固的SRAM单元结构,并应用于块存储器和配置存储器设计。如图3所示,当粒子入射A点,在入射路径上产生电子-空穴对,根据高能粒子入射电流双指数函数模型,

(1)

式中:I(t)为收集电荷过程中产生电流;Q为粒子入射路径上的沉积电荷数量;τα为电荷收集时间;τβ为粒子入射的持续时间。电荷收集过程产生的脉冲电压造成A点数据翻转,在电荷收集完成后消失,当脉冲电压持续时间满足存储单元锁存条件时,单元存储的数据被改写。六管单元反馈通路传输延迟较小,较低能量粒子入射产生的脉冲电压即可满足锁存条件要求,因此抗单粒子翻转能力较弱。

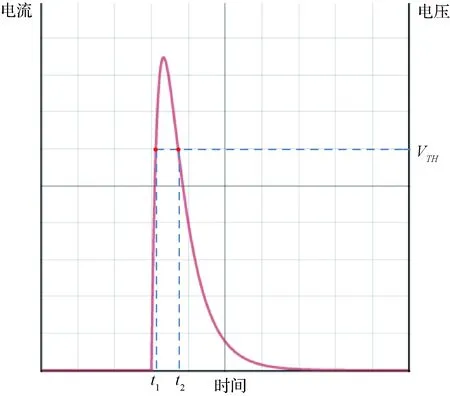

在脉冲屏蔽单元中,反馈回路中加入延迟结构D,通过调节D的参数改变反馈延迟时间。如图4所示,假设在给定节点A处寄生电阻值固定,则粒子入射的脉冲电压V(t)与电流I(t)值呈线性关系。存储单元中反相器翻转阈值为VTH,脉冲电压高于VTH的持续时间Δt,

Δt=t2-t1

(2)

图3 脉冲屏蔽加固SRAM单元Fig.3 Pulse shielded SRAM cell

在入射粒子能量确定的情况下,D的延迟时间tD满足如下条件:

tD>Δt

(3)

高能粒子入射产生的脉冲电压在传递到节点B时候已消失,实现单粒子翻转加固的效果。

图4 粒子入射电流双指数函数曲线Fig.4 Double exponential function curve

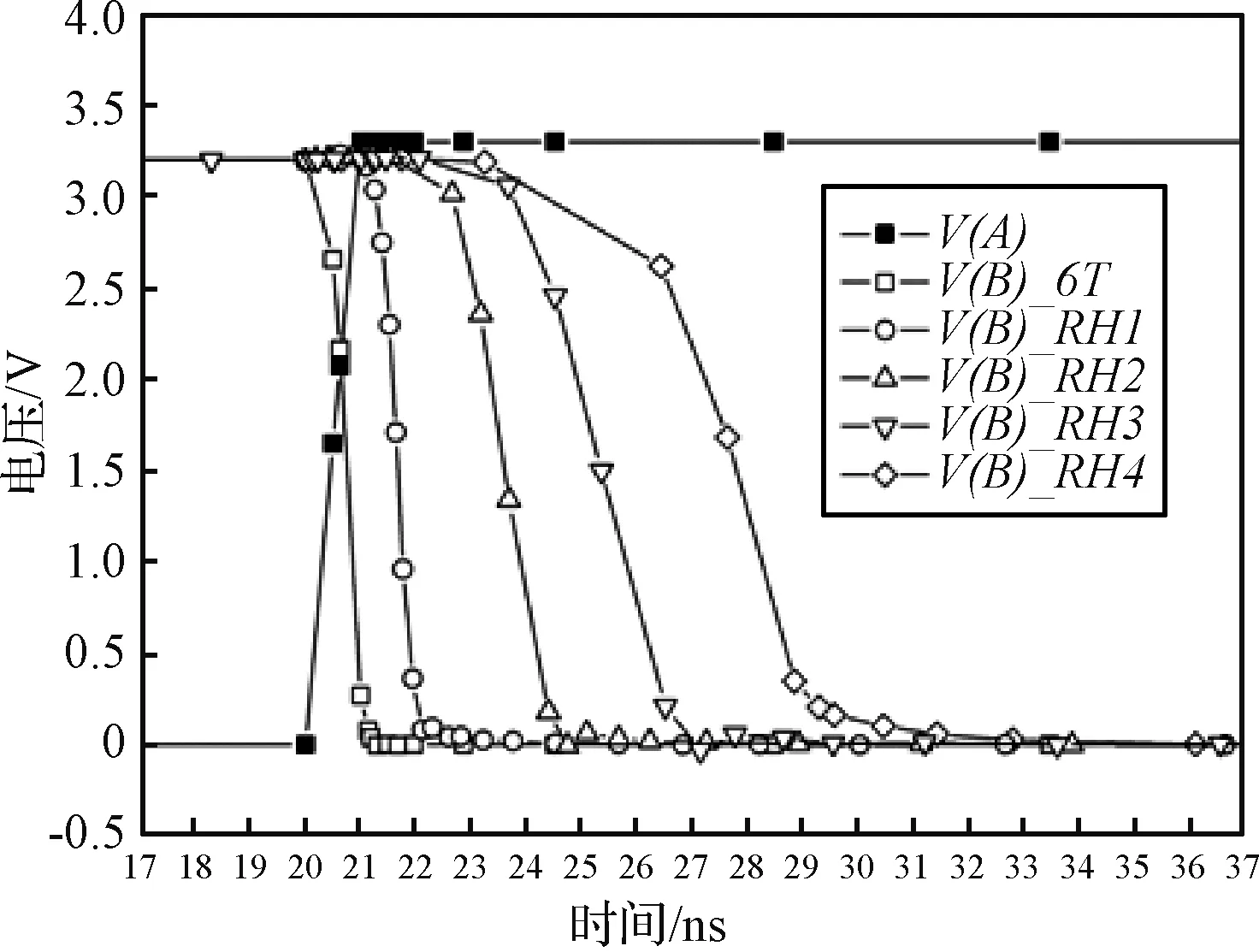

由图5仿真波形所示,其中V(A)为输入对应图3中的A点,V(B)为输出对应图3中的B点。从仿真结果可知,6管单元在B点的响应时间最小,加入延迟结构后,延迟时间tD随参数的设置逐渐增大。

图5 不同延迟条件存储单元翻转波形Fig.5 SRAM cell in/out waveforms with different tD

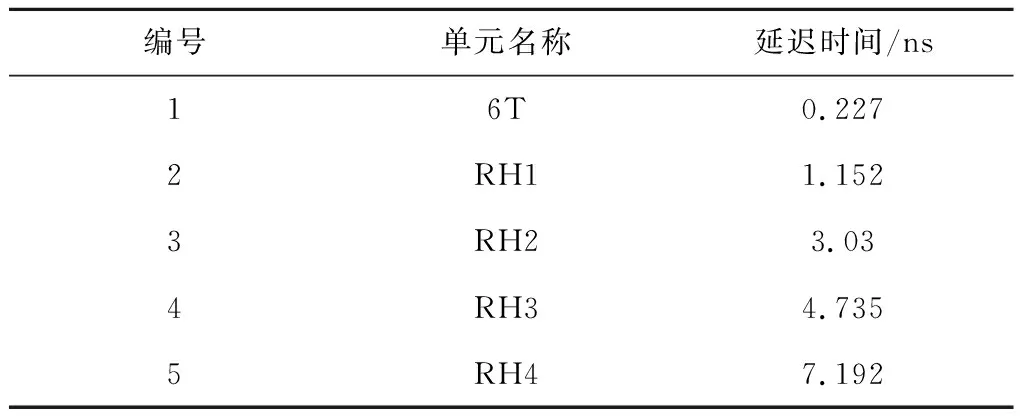

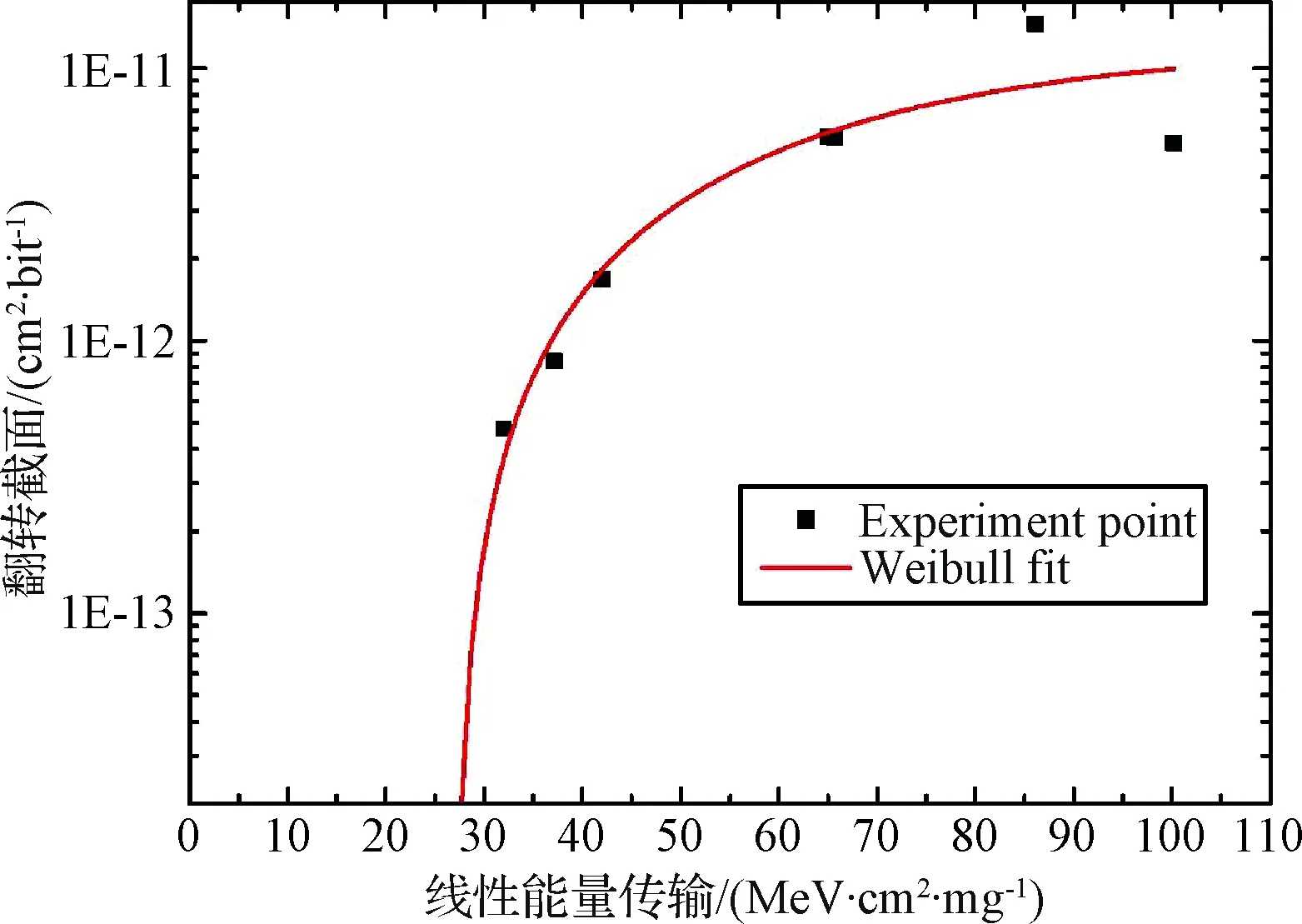

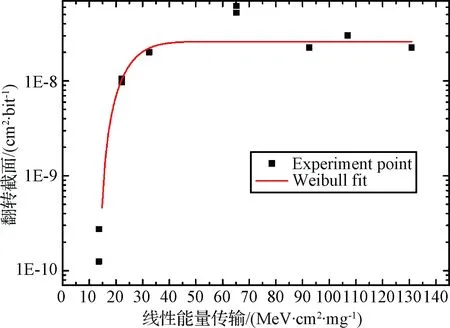

通过两款基于0.18 μm SOI工艺设计的64k SRAM对6管单元和图3所示脉冲屏蔽加固单元的抗单粒子翻转性能进行评估,加固单元选用表2中CELL_RH2条件对应延迟参数。为了排除其他设计因素影响,两款SRAM仅存储单元存在差异。由图6、图7中Weibull拟合曲线所示,选取电路翻转饱和截面值的10%对应的LET值为电路的单粒子翻转阈值[23],采用脉冲屏蔽加固单元的电路单粒子翻转阈值为SEULETTH>45 MeV·cm2·mg-1,采用6管单元电路翻转阈值为SEULETTH>25 MeV·cm2·mg-1。在加固单元面积方面,延迟结构中不包含MOS器件,因此面积对比6管单元并未显著增加,为3.32 μm×4.16 μm,6T单元为3.32 μm×3.43 μm,加固单元比6管单元增加约21.3%。

表2 加固单元与6管单元延迟时间仿真对比Table 2 Delay time comparison between different conditions of pulse shield cell and 6T cell

图6 加固单元单粒子翻转Weibull曲线Fig.6 Pulse shield cell SEU LET Weibull curve

图7 六管单元单粒子翻转Weibull曲线Fig.7 Standard 6T cell Weibull curve

3 FPGA电路实现

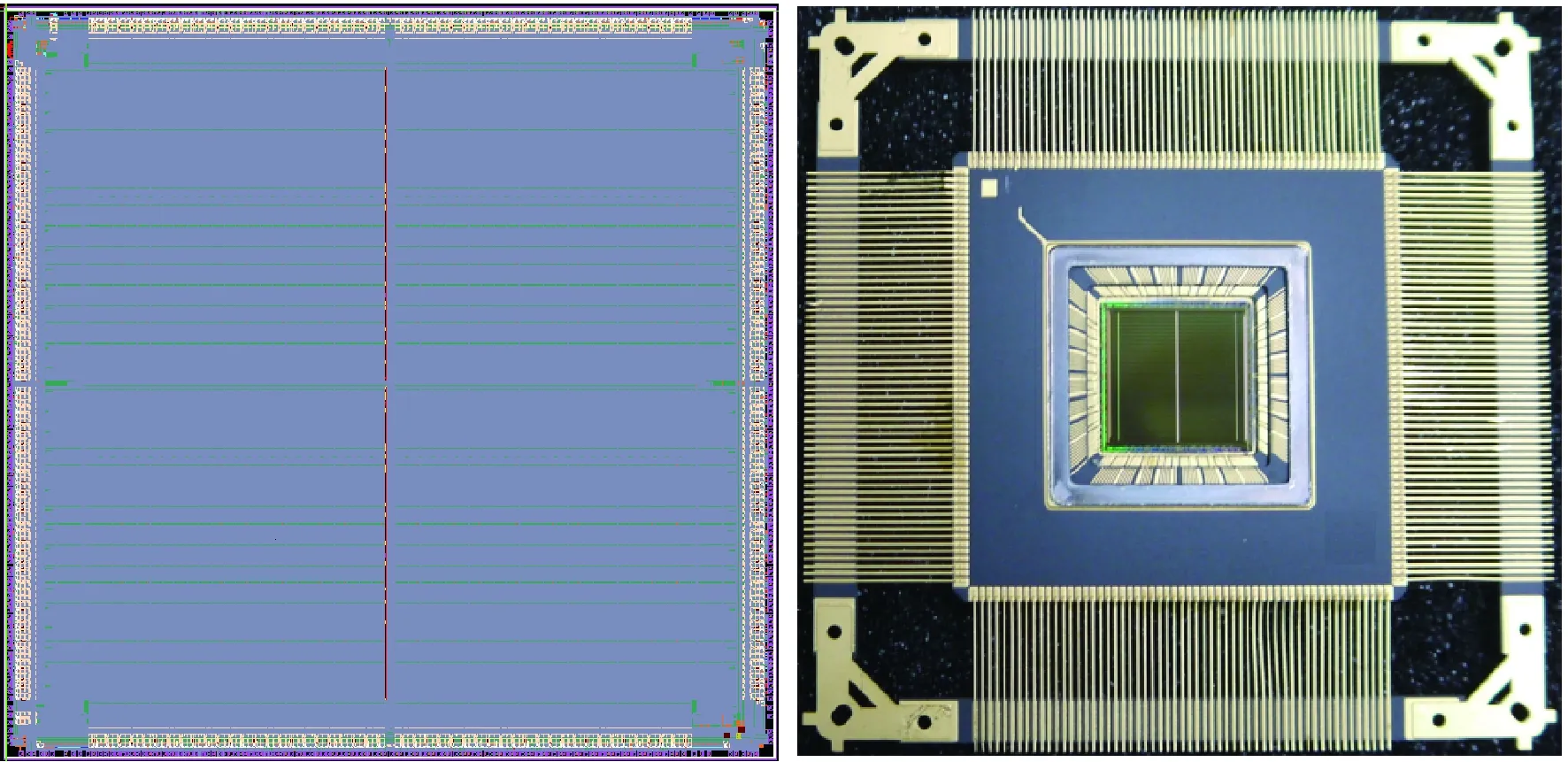

IC300R FPGA是基于0.18 μm部分耗尽SOI CMOS工艺设计,I/O电源电压为3.3 V,内核工作电压为1.8 V,采用6层金属互联。电路设计采用定制设计和自动布局布线相结合的设计方法。IC300R版图根据LT模块分布情况进行优化布局,水平方向1个块存储器与4个逻辑块宽度基本一致,2个PAD与1个逻辑块宽度基本一致;在竖直方向3个PAD与1个逻辑块高度基本一致,通过全局规划实现电路版图在X方向和Y方向长度近似,为管壳选型和封装提供便利条件。IC300R电路整体版图面积为12.7 mm×13 mm,采用CQFP228形式封装。

图8 IC300R FPGA版图和电路开帽图Fig.8 IC300R FPGA layout and package outlook

4 功能测试和辐照测试

4.1 功能测试

FPGA测试和其他超大规模数字集成电路测试情况类似,面对不同的IP(Intellectual Property)和复杂的逻辑,不可避免的需要大量测试算法和资源[24]。当前FPGA电路以异质结构为主,其内部包含可编程互联单元、逻辑块和内嵌SRAM等模块以及大量的IP,资源的丰富性和逻辑的复杂性对测试的完整性也提出了很高要求。大量的研究报告和文献分析并提出整体或功能模块级的测试方法[25-27]。

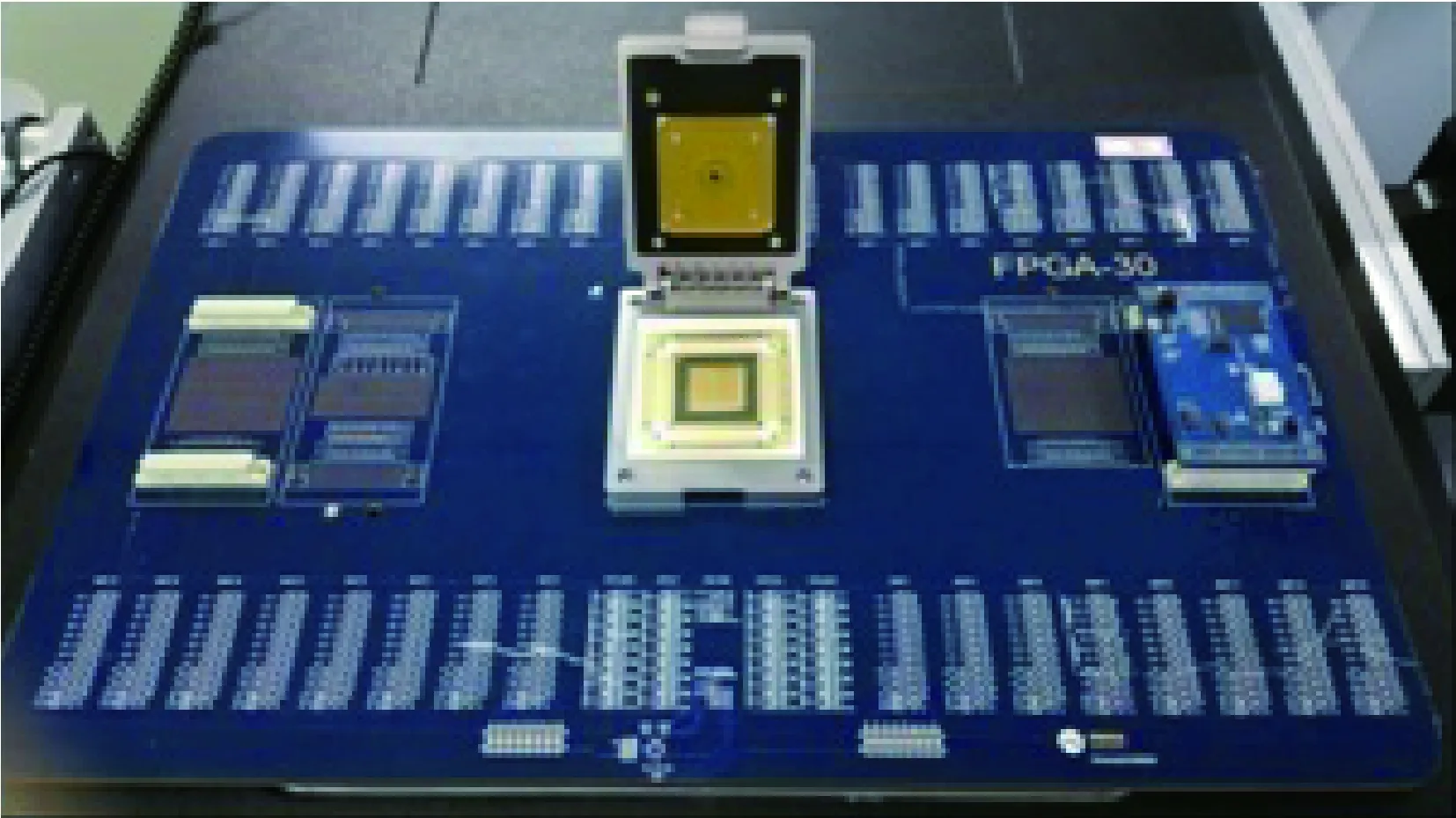

本文结合已有的研究成果开发针对IC300R FPGA的测试向量集,包括可编程逻辑块矩阵、寄存器链、RAM测试、互连测试、查找表测试等共150条功能测试向量,覆盖93%的逻辑资源和80%的互联资源,并基于Teradyne J750EX测试平台(如图9所示),通过JTAG模式实现电路的配置和测试。

图9 IC300R FPGA测试板Fig.9 IC300R FPGA test board

表3 IC300R与XCV300电路对比Table 3 Comparison between IC300R and XCV300

4.2 辐照测试

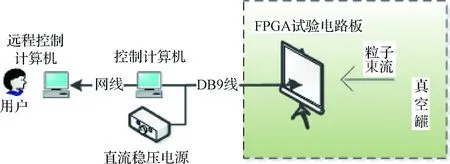

IC300R FPGA的辐照测试包括单粒子翻转(Single Event Upset, SEU)、单粒子锁定(Single Event Latch, SEL)和总剂量(Total Ionizing Dose, TID)测试。单粒子测试系统如图10所示,控制计算机通过JTAG接口完成对待测FPGA的配置和回读,并对回读数据是否翻转进行对比。直流稳压电源完成对监控待测电路供电和对功耗实时监控,远程控制计算机主要完成在线测试及试验过程中特殊情况下的复位和离线操作。

图10 IC300R单粒子翻转试验系统示意图Fig.10 IC300 SEU test system sketch

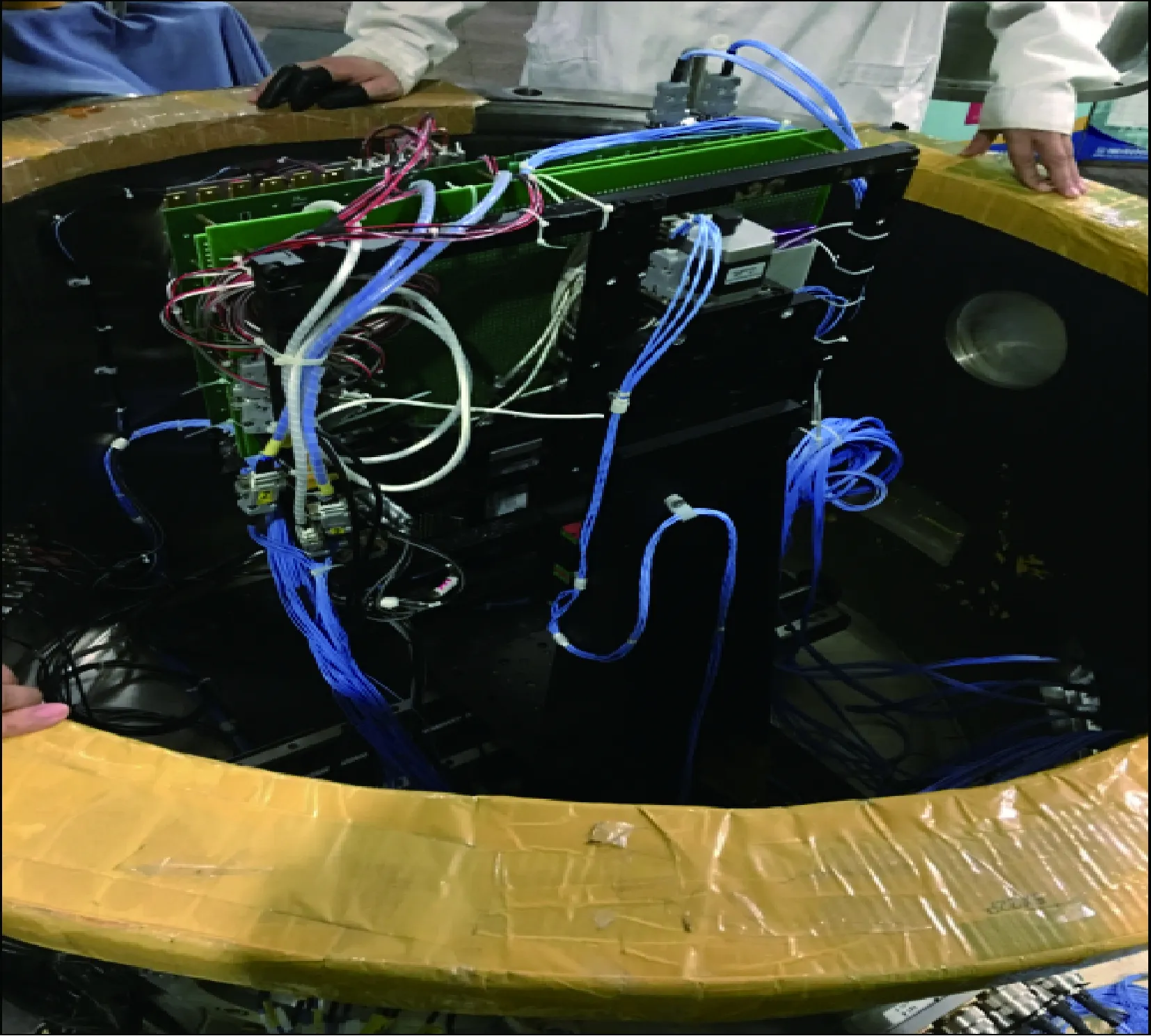

图11 IC300R FPGA单粒子翻转测试Fig.11 IC300R FPGA SEU test

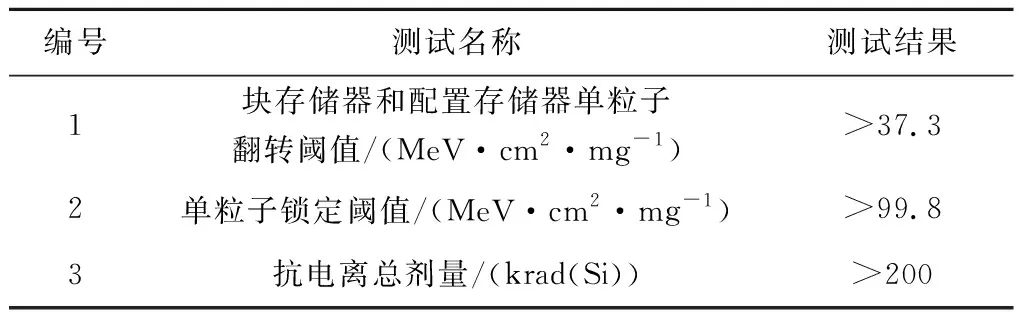

单粒子翻转通过对块存储器和配置存储器进行静态测试[23]完成评估。照射源选用中国原子能研究院串列加速器(HI-13)进行Ge离子照射,能量为208 MeV,硅中射程为30.3 μm,LET值为37.3 MeV·cm2·mg-1,注量率为1×104ions/(cm2·s)。离子总注量达到1×107ions/cm2时,IC300R电路块存储器和配置存储器无数据发生翻转。

单粒子锁定测试[23]选用兰州重离子加速器Bi离子照射,该离子在硅中LET值为99.8 MeV·cm2·mg-1,注量率为1×104ions/(cm2·s)。IC300R电路在离子累积总注量达到1×107ions/cm2时为测试终止条件,无单粒子锁定现象发生。

总剂量测试[28]选用Co-60放射源,在剂量率为50 rad(Si)/s条件下进行,累积总剂量达到200 krad(Si)时,进行电测试并加照50%剂量,经100 ℃、168小时高温加电退火。终点电测试结果显示IC300R电路功能正常,试验前电路静态电流为34.4 mA,退火后静态电流为37.2 mA。表4列举了全部辐照试验结果。

表4 IC300R FPGA辐照测试结果Table 4 IC300 FPGA radiation test results

5 结 论

本文介绍的IC300R电路是一款抗辐照FPGA,采用0.18 μm SOI CMOS工艺并结合设计加固共同实现其抗辐照性能。辐照测试结果显示,IC300R FPGA抗电离总剂量水平大于200 krad(Si),抗单粒子翻转阈值大于37.3 MeV·cm2·mg-1,抗单粒子锁定阈值大于99.8 MeV·cm2·mg-1。

在抗辐照设计加固方面,脉冲屏蔽加固SRAM单元被用于块存储器和配置存储器中,仅比相同工艺条件的6管单元面积增加21.3%,实现了抗单粒子翻转阈值大于37.3 MeV·cm2·mg-1设计预期。该加固单元应用在64k SRAM验证电路中,使电路抗单粒子翻转性能有明显提升,单粒子翻转阈值由采用6管单元SEULETTH>25 MeV·cm2·mg-1提升至SEULETTH>45 MeV·cm2·mg-1。

最后,电路级单粒子翻转加固是一项系统工程,我们通过对64k SRAM电路和IC300R FPGA电路抗单粒子翻转性能分析并确认,脉冲屏蔽加固单元是一种有效提升电路抗单粒子翻转水平的SRAM单元结构。