A novel BIST scheme for circuit aging measurement of aerospace chips

2018-07-24HuguoLIANGXingshengFANGMoxingYIZhengfengHUANGYingchunLU

Huguo LIANG,Xingsheng FANG,b,*,Moxing YI,Zhengfeng HUANG,Yingchun LU

aStudio of Computer Architecture,Hefei University of Technology,Hefei 230009,China

bAnhui Institute of Economic Management,Hefei 230051,China

KEYWORDS Aging measurement;Avionics;BIST;Critical path;Self-oscillation loops

Abstract The avionics working environment is bad,easy to accelerate aging of circuits.Circuit aging is one of the important factors that influence the reliability of avionics,so circuit aging testing is of great significance to improve the reliability of avionics.As continuing aging would degrade circuit performance,aging can be monitored through precise measurement of performance degradation.However,previous methods for predicting circuit performance have limited prediction accuracy.In this paper,we propose a novel Built-In Self-Test(BIST)scheme for circuit aging measurement,which constructs self-oscillation loops employing parts of critical paths and activates oscillations by specific test patterns.An aging signature counter is then used to capture the oscillation frequency and in turn measure the aging state of the circuit.We propose to implement this measurement process by BIST.Experimental results show that the proposed in- field aging measurement is robust with respect to process variations and can achieve a precision of about 90%.The application of this scheme has a certain value to improve the reliability of avionics systems.

1.Introduction

With the development of aerospace technology,the reliability of digital systems is becoming more and more important.Because aviation equipment works in harsh environments,such as strong electromagnetic radiation and high temperature,those elements can accelerate the aging of circuits,which can seriously reduce the reliability of digital systems.1,2Therefore,the design of a highly reliable digital system has become an extremely challenging process with the aggressive scaling of semiconductor technology.Circuit aging is one of the issues that influence the system reliability.Aging could increase the threshold voltage,increase the circuit delay,and degrade the circuit speed.Eventually,it could cause timing errors and circuit failures.There are many mechanisms causing circuit aging,which include Negative Bias Temperature Instability(NBTI),Hot Carrier Injection(HCI),and Time Dependent Dielectric Breakdown(TDDB).In nanometer circuits,NBTI is very serious and becomes the dominant factor over a variety of aging mechanisms,which could cause more than 20%degradation of circuit performance in the worst cases.3,4

Precise measurement of circuit aging is a critical problem for designing and maintaining aging-resilient circuits.In previous studies of aging measurement,online aging prediction and using a reference ring oscillator are two alternative techniques.

Online aging prediction employs aging sensors monitoring signals on a data path online.5–7It evaluates the state of circuit aging utilizing a detection guardband,which is a time interval proceeding the sampling edge of clock.If the transition of a logic signal occurs within the guardband,it triggers an aging signal.

A representative approach of online aging prediction using sensors is the Aging Resistant Stability Checker(ARSC),described in Ref.5,which employs a delay element to generate a guardband on a critical path.An aging sensor monitors the logic signal and determines circuit aging by checking whether a data transition appears within the guardband.The advantage of this method is that the aging sensor is aging resilient.Its sensitivity to aging is much lower than those of the other parts of the circuit.However,it could only determine whether an aging-induced error would occur,but couldn’t evaluate the degree of actual aging of the circuit.In addition,this method requires one additional aging sensor for eachflip-flop in the circuit.Therefore,the limited resolution of the result and its high area overhead are the major problems of this method.Moreover,process variations could significantly influence the precision of prediction,and this sensor may hardly work in circuits running at a high frequency.

Employing a reference ring oscillator is another method for aging measurement.8–10This technique constructs two extra rings on a chip.One is a stressed ring,and the other a reference ring,which is not stressed during operation.These two rings could oscillate to generate different pluses.It estimates the aging state of a circuit based on the comparison result between the stressed and reference rings.

The method proposed in Ref.8is a representative reference ring method to estimate the degradation of an aging circuit.In addition to two oscillating rings,it employs a phase comparator and a frequency detector to measure the phase difference between the two oscillating rings,from which the amount of aging degradation is computed.Two other methods based on a reference ring are proposed in Refs.9,10.In order to determine the precise location in the last cycle,they connect each logic gate of the reference ring to aflip-flop and employ a counter to measure the frequencies of the rings.Therefore,the overheads of area and power consumption are very significant.

A reference ring could quantify the process of circuit aging.However,the feasibility of this technique is based on a hypothesis that the aging process of a circuit under measurement and a stressed circuit for quantification are somewhat synchronized.In fact,the aging process is closely related to the workloads of a circuit.The operational conditions of different circuit instances are always different.Therefore,in practice,their aging states differ,so the assumption is hardly valid,and thus the method based on a reference ring oscillator would not reflect the aging state of a circuit accurately.

In this paper,we propose an in- field circuit aging measurement method based on a built-in self-test.The major contributions of this method are:

(1)It employs parts of critical paths to construct selfoscillation loops,which could more accurately reflect the aging process of critical paths.

(2)It triggers the self-oscillation loops by specific testing patterns and captures measuring results by an aging signature counter.

(3)It reuses the structure of the built-in self-test to control the measuring process,which helps reduce the overall area cost.

A set of experiments has been conducted to evaluate the validity and accuracy of this measurement method.The results show that this method could reflect the aging process of a circuit with a highfidelity.Its average precision is about 90%,and process variations have little impact on measuring results.

The remainder of this paper is organized as follows.Section 2 reviews related work of aging measurement.Section 3 describes our proposed method based on in- field circuit aging measurement,including criticalpath identification,selfoscillation loop construction,self-oscillation loop sensitization,and evaluation of circuit aging.Experimental results of this method are shown in Section 4.Finally,conclusions are offered in Section 5.

2.Related work

Built-In Self-Test(BIST)and oscillating rings are two efficient Design for Testability(DfT)methodologies for modern chips.BIST is effective for both stuck-at and transient faults,and an oscillating ring is a closed-loop circuit which could be used to test the delay of a circuit.

BIST employs DfT structures on a chip to trigger fault detection by the circuit itself.11–25Generally,there are two categories of BIST techniques:of fline BIST and online BIST.The of fline BIST generally uses a test pattern generator and an output response analyzer to test faults during a circuit suspense operation.The online BIST usually employs a duplicated circuitry to detect run-time errors during a circuit normal operation.5–10Due to the testing structures on a chip,faults in the Circuit Under Test(CUT)could be detected easily.In this paper,we reuse the BIST structure for sensitization of critical paths and further construct self-oscillation loops to measure circuit aging of the CUT.

Oscillating rings have been used to measure the process of circuits aging.8–10An oscillating ring is a closed-loop circuit.Therefore,the output response of the loop will become the input signal.If the overall logic function of the loop is logic‘not”,its input signal would oscillate between ‘0” and ‘1”,and then the oscillation count of the closed loop could be used to characterize the performance of the loop throughout the circuit’s lifetime.When the circuit ages,its performance degrades,and in turn the oscillating frequency decreases.Therefore,testing the oscillating frequency of the paths in the circuit could reflect the degree of circuit aging.

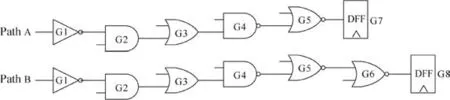

The method proposed in Refs.8–10is illustrated in Fig.1.It uses two extra oscillating rings to emulate each critical path in the CUT.Because an emulated ring does not follow the actual operational conditions of the circuit,the result based on the emulated ring cannot accurately reflect the degradation of circuit aging.Moreover,its area overhead is extremely high because the amount of the critical paths in the CUT is generally very large.In this paper,we construct self-oscillation loops using parts of critical paths in the CUT directly and activate the oscillation with specific test patterns by reusing the BIST structure.

Fig.1 Classical oscillating rings.

3.In- field circuit aging measurement

As circuit aging is highly related to the temperature,workload,and other on-chip conditions,only testing on an interior circuit itself could precisely reflect the actual aging state of each circuit.In this paper,an in- field method for aging measurement using self-oscillation loops based on the BIST architecture is proposed.Its structure is shown in Fig.2.

The BIST architecture generally includes an on-chip Test Pattern Generator(TPG)and a response analyzer which typically is a Multiple-Input Signature Register(MISR)as illustrated in Fig.2.The TPG could generate a test pattern applied into the CUT by using a scan chain,and the response would be scanned out and compressed by the MISR.A controller unit is also a critical partial component for the BIST architecture which could operate both functional and test circuitry during the test mode.In the proposed in- field aging measurement,the BIST architecture is extremely crucial.

The in- field method employs parts of critical paths of a circuit to construct self-oscillation loops,the oscillation count of which could actually characterize the aging state of the CUT.Then,it reuses the mechanisms of BIST to realize measuring each critical path sensitized by a specific testing pattern,which is applied to the circuit by a scan chain.The aging signature counter collects the testing information of self-oscillation loops.The final measuring result is generated by comparing the aging signature counter with the standard value.The flow of this measuring method is illustrated in Fig.3.

As the control unit is quite important in BIST,it could generate multiple control signals,such as scanning-enable signal,clock signal,etc.Under the synergy of these signals,the CUT could work on different modes.For example,when a scanning-enable signal is triggered,the test pattern generated by the Auto Test Pattern Generator(ATPG)26would be applied into the CUT,and an oscillating loop sensitization would befinished.After agitating the oscillating loop,the infield aging measurement starts to work.Otherwise,the CUT works in the normal mode.

3.1.Critical path identification

Though the amount of sub-paths generated by STA in a circuit is generally very large,only a few of them would be erroneous under circuit aging,and then they should be tested to evaluate their aging states.Meanwhile,if one path is contained by another one,the aging state of the former one could be reflected by that of the latter one,and only the latter one should be measured.The identification of a critical path aims to reduce the scale of the testing set as much as possible without impacting on the measured result.

As an example illustrated in Fig.4,there are two critical paths,named Path A and Path B,in a circuit under testing.The logic gates on Path A are{G1,G2,G3,G4,G5},noted as set A,and the gates on Path B are{G1,G2,G3,G4,G5,G6},noted as set B.Since set A is a subset of set B,Path A would be removed from the testing set.

The method of determining the critical path is from Ref.27,in which an NBTI-based timing analysis framework was proposed.The framework determines an aging-sensitive potential critical path set in a circuit and then further determines agingsensitive critical gates considering path correlations.This method is effective and easy to use,drawing attention from different communities.

Using the method above,amounts of paths such as path A would be removed from the testing set,so the rest paths in the testing set are more representative.Moreover,the scale of the testing set could be further decreased with considering circuit aging.Research has shown that more than 20%degradation of circuit performance could be caused by aging in the worst cases.The delay of a logic path increases as a circuit ages.Suppose that one path is named Path M in the testing set,and its delay isdat the beginning.After working for years,its delay turns intoD,and the maximum inherent delay of the paths in the circuit is definedT.IfDis less than(1+20%)T,Path M would be removed from the testing set.After these works,the scale of the testing set is highly cut down,and then the remained is called critical path.

Fig.2 Structure of in- field aging measurement.

Fig.3 In- field circuit aging measurement.

3.2.Self-oscillation loop construction

A self-oscillation loop is a ring that contains an odd number of inverters which could oscillate by itself after applying a specific vector without any other driving.In this paper,we classify logic gates into three categories which include reversed gates,masked gates,and undetermined gates.Reversed gates include INV,NOR,and NAND.They could be transformed into inverters by a specific input setting.Masked gates include AND and OR,which should be masked in the loop.Undetermined gates are XOR and XNOR.They could be transformed to either inverters or transmission gates.For example,if an input of NAND is 1,then it is transformed into an inverter.If an input of AND is 1,then it is just like a transmission gate.Additionally,when an input of XOR is 1 or 0,it is an inverter or a transmission gate.Fig.5 gives a demonstration of gate transformation.

Before constructing a self-oscillation loop,we firstly count the number of reversed gates in the critical path.If it is not odd,we would select an undetermined gate to keep an odd number of inverters in the loop.Then we set the necessary input value of each gate according to the gate type.Finally,it connects the input of the first gate to the output of the last gate on the test path to construct a loop,which could oscillate by itself after applying a specific test vector.

The worst case of loop construction is that the number of reversed gates is not odd,and there is no undetermined gate in the test path.In this case,we could add an extra inverter in the loop without influencing the normal function of the circuit.

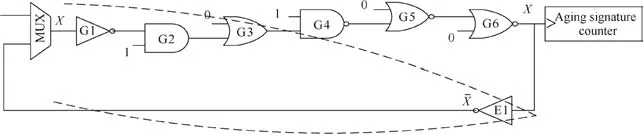

In Fig.6,the constructed self-oscillation loop of Path B(Fig.4)is illustrated.There are only four reversed gates in Path B,so that an extra inverter,E1,is added to the loop.

3.3.Generation of aging test vectors and excitation of selfoscillating circuits

The constructed loop could oscillate when applying a specific testing vector,which is generated by an existing ATPG algorithm.It is just like sensitizing a stuck-at fault and only needs to transferXtoon the data path.Generally,we consider X to be the input andto be the output of the data path.In Fig.6,the testing generation is to pass the input of G1 to the output of G6,which would be reversed after logic computing by E1.

Fig.4 Two paths under testing.

Fig.5 Rule of gate transformation.

Fig.6 Self-oscillation loop of Path B.

Controlling the interior nodes is the same as the circuit test,which could be performed by applying a specific testing pattern to the inputs of a circuit.In the BIST,it connects memory elements into a shift register as a scan chain to apply testing vectors.The excitation of a self-oscillation loop could be realized in the same way.In this paper,we reuse the scan chain in BIST to apply the testing pattern for each critical path and keep the inputs of the circuit unchanged until the end of aging measurement.

The scanflipflops would be helpful in applying the testing pattern.Fig.7 shows a Scan Flip-Flop(SFF)cell,which was modified from the traditional Dflip-flop with adding a multiplexer.Compared with the Dflip-flop,the scanflipflop has more functions.When pin TC receives a high level,it works as a Dflip-flop.On the contrary,it works in the pattern of the scanning mode,and the data on pin SD would be scanned.CK is the clock input.Qandare two opposite outputs,respectively.In order to control and observe the state of each SFF,the scan chain is practical,as shown in Fig.8.The SCANIN and SCANOUT define the input and output of a scan chain,respectively,and the output of each SFF is connected to the scanning input(SD)of the next.

Once pin TC receives a low-level signal,the scan chain starts to work as a long shift register.Desired values could be shifted into the scan chain,and the state of everyflip-flop would be controlled and observed.In the same way,a specific test pattern could be applied into the circuit by using the scan chain.Suppose that a specific testing pattern is applied to the inputs,the critical path(in Fig.6)would be sensitized.When the testing signalstarts to propagate on Path B,the control unit changes the working mode of MUX.After that,a selfoscillation loop has been created and begins to agitate.

Fig.7 Scanflip-flop cell.

3.4.Aging measurement of circuits

In circuit aging measurement,an aging signature counter is employed to quantify the aging state.The realization of the aging signature counter could be a kind of shifting counter with functions of setting and resetting.It is triggered by the output of the self-oscillation loop,i.e.,the calculation of the aging signature counter is increased by one after every two cycles of the self-oscillator loop.It collects the cycles of the self-oscillation loop in a predefined testing period.Fig.9 is one kind of the aging signature counter we used in circuit aging measurement.

The output of the aging signature counterNagingwould be compared with the reference oneNreferencestored on a chip by reusing the structure of BIST.The reference amounts are the cycles of these loops without aging.The testing time for countingNreferenceis the same as that forNaging.

The typical principle of aging evaluation is in Eq.(1),where symbolDreferenceis the delay of the fresh circuit whileDagingis the delay of the aged circuit.Due to the constant testing time for circuit aging,Eq.(2)is right,so it does not have to compute the real propagating delay of the circuit,and the amount of oscillating cycles could be employed to measure the degree of circuit aging.

Eq.(3)is the quantifying method for circuit aging used in this paper,which is deducted from Eqs.(1)and(2).In Eq.(3),the aging measurement accuracyCdegradationis determined by the reference eigenvaluesCreferenceand aging eigenvaluesCaging.

Fig.8 Scan chain design framework.

Fig.9 One structure of the aging signature counter.

The quantifying precision of aging measurement in this paper is related to the maximum number(MAXcounter)of the aging signature counter.Because all the outputs of the signature counter are integers,the precision of testing is equal to the reciprocal of MAXcounter.For example,if there are tenflipfl ops in the counter,the maximum precision is 1/1024,i.e.,it could measure a degradation of circuits less than 0.1%.Moreover,we could predefine the initial number of the signature counter to change the precision in the process of measurement.

4.Experiments

In this section,we would show the implementation and experimental results of the proposed in- field aging measurement in specific circuits.

4.1.An implementation of circuit aging measurement

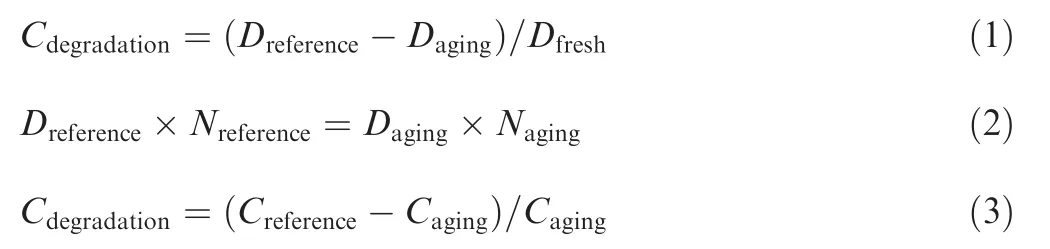

An experiment of this method is performed on circuit S27.Seven critical paths are identified by the proposed identification principle,which are as follows:{(P1:G1,G12,G13),(P2:G1,G12,G15,G9,G11,G17),(P3:G1,G12,G15,G9,G11,G10),(P4:G0,G14,G8,G16,G9,G11,G17),(P5:G0,G14,G8,G16,G9,G11,G10),(P6:G0,G14,G8,G15,G9,G11,G17),and(P7:G0,G14,G8,G15,G9,G11,G10)}.For these seven paths,the responding self-oscillation loops are implemented as shown in Fig.10,where inverter Eiis to keep an odd number of reversed gates.

When a stuck-at fault exists at the output of MUX,and this fault is sensitized to the output of the self-oscillation loop,then testing patterns can be generated by an ATPG algorithm20for sensitization of the self-oscillation loops.There are seven patterns to agitate the seven paths:{(P1:XX0XXX0),(P2:1XX10X0),(P3:1XX10X0),(P4:0XX001X),(P5:10X0010),(P6:X1X101X),and(P7:11X101X)}.Each testing pattern would agitate at least one loop.By reusing the structure of BIST,the testing patterns could be stored on a chip and applied to the circuits with the scan cells to agitate the loops.The detailed experimental steps are shown in Fig.3.

4.2.Results and analysis

In order to evaluate the precision of the proposed method,we implemented measurement on circuit S27 and compared its results with those of the golden-model which was simulated by Hspice under the same workload.Experiments were conducted under a 1.1 V supply voltage,a 65 nm technology size,and 273 K temperature,while the simulation time for each path is 105ps.

Fig.11 shows the measurement results on circuit S27 after aging of 5 years and 10 years,respectively.Since the paths under measurement are the actual parts of the circuit itself,they intrinsically reflect the aging degree of the circuit.The accuracy of Fig.11 is the ratio between the measurement results of this proposed method and those of Hspice simulation.According to the information in Fig.11,the measuring precisions under the aging processes of both 5 and 10 years are around 90%,compared with those of the golden model.

Fig.10 Seven self-oscillation loops of S27.

Fig.11 Precision of measurement.

The experimental results of nine ISCAS’89 benchmark circuits27are shown in Fig.12.It shows the measurement accu-racy of experimental results on the part of ISCAS’89 circuits,which is the average of all aging sensitive characteristic path metrics.The precision achieved with the proposed scheme is higher than 90%after aging of 5 and 10 years.

Fig.13 shows the result of comparison between the in- field method proposed in this paper and the method proposed in Ref.8.After aging of 5 years,the average measuring precision of Ref.8is just above 50%,and the precision is only 65%after aging for 10 years,which are significant lower than those of our method.The main reason is that the workloads of reference rings are different from the interior parts of circuits,so they would not age synchronously.

In order to quantify the effect of process variations,we employ Monte Carlo simulation,where the process variations are considered as Gaussian distributions,and the related parameters are calculated with the 3δ principle.Each simulation for the method is performed with 10,000 runs.The results of the simulations are described in Table 1.The measuring precision is evaluated under process variations of 10%,15%,and 20%.It could be seen that the effect of process variations on the method proposed in this paper is less than 1%,which achieves a much less effect by process variations and a lower rate of slope,compared to Ref.8.

Fig.12 Average accuracy of aging metrics.

Fig.13 Comparison between two different measuring methods.

Table 1 Sensitivity to the process variations.

5.Conclusions

In this paper,an in- field method for circuit aging measurement using BIST is proposed.It utilizes part of a circuit under measurement to construct self-oscillation loops and activates these loops by specific testing patterns.The results of self-oscillation loops are collected by an aging signature counter,which are compared with the reference data to estimate the aging state of the circuit.Experimental results and comparisons show that this method holds a high measuring precision and is not sensitive to the effect of process variations.This paper presents a scheme to accurately measure the aging of circuits,which will improve the reliability of avionics systems to some extent.Therefore,the research of this scheme has certain theoretical significance and application value to the reliability of avionics systems.

Acknowledgments

This paper was supported by the National Natural Science Foundation of China(Nos.61674048,61574052,61474036,61371025)and Project Team of Anhui Institute of Economics and Management of China(No.YJKT1417T01).

杂志排行

CHINESE JOURNAL OF AERONAUTICS的其它文章

- Particle image velocimetry for combustion measurements:Applications and developments

- Abnormal changes of dynamic derivatives at low reduced frequencies

- A new hybrid aerodynamic optimization framework based on differential evolution and invasive weed optimization

- Experimental study of an anti-icing method over an airfoil based on pulsed dielectric barrier discharge plasma

- Envelope protection for aircraft encountering upset condition based on dynamic envelope enlargement

- Effects of the radial blade loading distribution and B parameter on the type of flow instability in a low-speed axial compressor