基于SiGe BiCMOS工艺的高速光接收机模拟前端电路

2018-01-19谷由之毛陆虹吴思聪

谢 生,谷由之,毛陆虹,吴思聪,高 谦

基于SiGe BiCMOS工艺的高速光接收机模拟前端电路

谢 生1,谷由之1,毛陆虹2,吴思聪1,高 谦1

(1. 天津大学微电子学院天津市成像与感知微电子技术重点实验室,天津 300072;2. 天津大学电气自动化与信息工程学院,天津 300072)

光接收机;跨阻放大器;改进型Cherry-Hooper;直流偏移消除电路;锗硅双极-互补金属-氧化物-半导体

随着社会信息化程度的不断提升,人类社会对网络带宽和数据流量的需求指数增长.为满足海量信息的传输,用于干线网络传输的超高速、超大容量光纤通信技术已取得突破性进展.光接收机作为光通信系统的重要组成部分,其功能是把光纤线路输出的微弱光信号转换为电信号,经数字处理后,恢复发射前的原始信号[1-3].

作为接收链路的核心部件,光接收机前端电路的参数指标决定着通信系统的整体性能[4].尽管CMOS工艺具有成本低、集成度高的优势,但MOS器件的跨导低、寄生效应大、噪声性能差.因此,基于CMOS工艺的光接收机很难实现宽带应用[5].而SiGe BiCMOS工艺将高速、电流驱动能力强和模拟精度高的双极技术与CMOS技术融合,为实现高速光接收机创造了良好条件[6].2013年,Brandl等[7]基于BiCMOS工艺设计的一款跨阻放大器,尽管可以实现86.6,dBΩ的增益,但仅能满足3,Gb/s的数据传输.最近,Eissa等[8]设计的跨阻放大器虽然实现了40,Gb/s的数据传输,但增益只有49,dBΩ.由此可见,尽管基于SiGe BiCMOS工艺设计的电路在某个参数方面表现优秀,但仍需平衡各方面的制约,才能达到更好的整体性能.

本文基于IBM 0.18,µm SiGe BiCMOS 7,WL标准工艺,设计了一款光接收机模拟前端放大电路.该放大电路采用了射随器反馈的共射共基(Cascode)跨阻放大器,并对传统Cherry-Hooper限幅放大器进行了改进,同时对三级级联的限幅放大器分别给予不同的反馈,从而实现更高的带宽和更好的稳定性.另外,直流偏移消除电路中使用差分有源密勒电容来替代传统的片外大电容,在一定程度上也提高了电路的性能.

1 电路结构

标准光接收机的系统包括光电探测器、模拟前端电路[9]和数字后端电路.本文设计的模拟前端电路的整体结构如图1所示,包含跨阻放大器(TIA)、限幅放大器(LA)、输出缓冲级(Buffer)和直流偏移消除电路(DOC).其中,光电探测器接收来自光纤的微弱光信号,经光电转化后输出数微安的光电流至跨阻放大器[10].跨阻放大器将光电流转化并放大为具有一定幅度的电压信号.限幅放大器由三级改进型Cherry-Hooper(CH)增益级级联而成,它将继续放大电压信号,直至可用于数据恢复电路.输出缓冲级是为了测试方便而做的阻抗匹配,同时提供足够大的输出摆幅.直流偏移消除电路由一个低通滤波器(LPF)组成,用来消除过程变化引起的直流电压偏移.

图1 光接收机模拟前端电路结构

2 模拟前端电路分析

2.1 跨阻放大器

鉴于共射共基电路拥有较高的反向隔离度,且输出电阻远大于共射极电路,本设计中的跨阻放大器采用射随器反馈的共射共基结构,如图2(a)所示.反馈通路采用射随器获取输出电压,再由电阻F将其转化为电流信号反馈到输入端.

由仿真分析可知,HBT的基极-发射极等效电阻π和集电极-发射极输出电阻o的阻值都很大,因此在小信号分析中可忽略.与基极-发射极电容π相比,基极-集电极电容μ很小,所以小信号分析时忽略μ的作用.另外,射随器3管的偏置和发射极面积都很小,所以忽略基极-发射极电容π3的影响.因此,可画出如图2(b)所示的半边电路的小信号等效电路.

理论分析表明,电路的跨阻增益

(1)

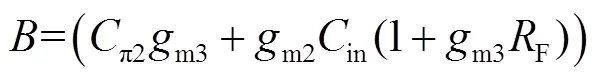

其中

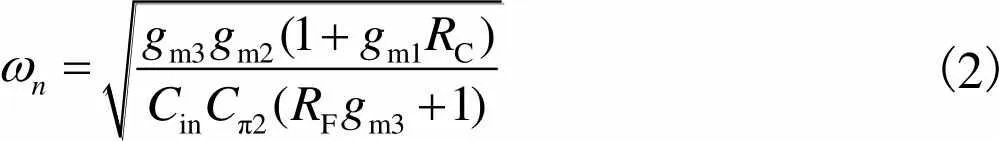

式中:in=π1+PD;π1和π2分别为1和2管的基极-发射极电容;PD为PD结电容;m1、m2和m3分别为1、2和3管的跨导.由式(1)可知,电路的固有频率ω和阻尼系数分别为

(2)

(3)

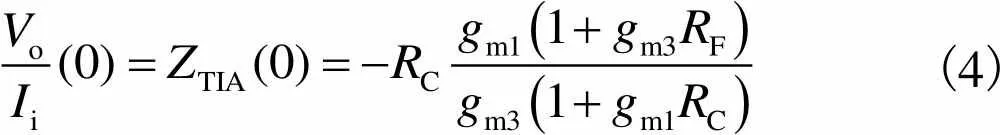

而电路的低频增益为

(4)

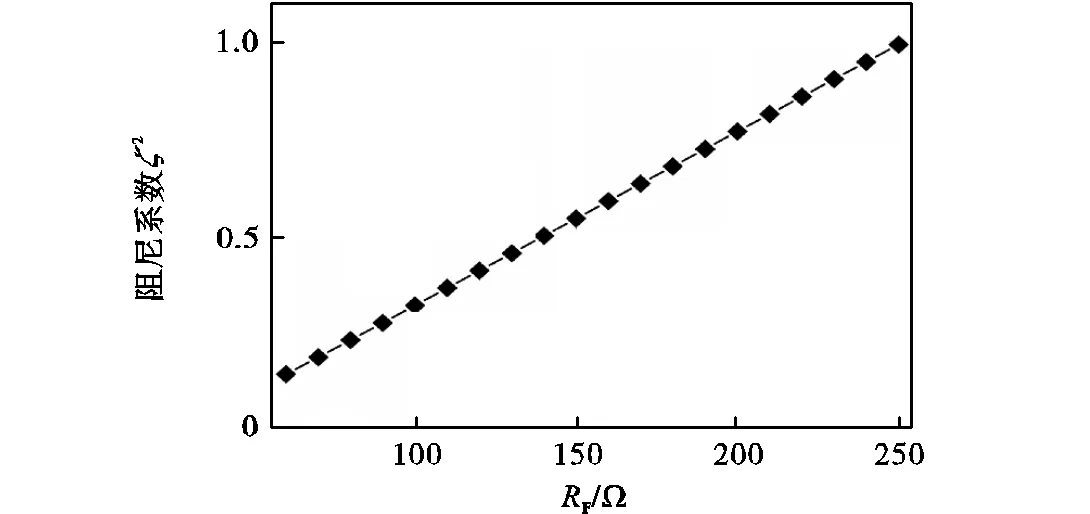

图3所示为由式(3)计算的阻尼系数ζ2与电阻F的关系曲线.显然,函数ζ2(F)近似于一次函数,电阻越大,反馈信号越小,值越大.由图可见,当F=140,Ω时,电路阻尼系数的平方等于0.5,这时可以获得最优的平坦度.

图3 z,2与RF的关系曲线

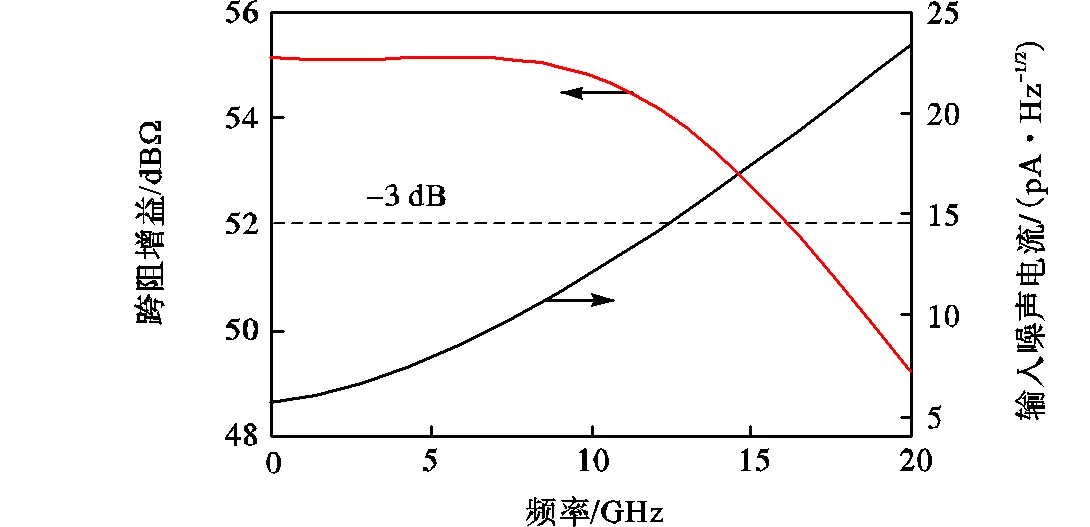

图4 TIA的跨阻增益和等效输入噪声

2.2 限幅放大器及直流偏移消除电路

限幅放大器作为接收机中的电压放大器,需要为后级的数据判决电路提供较大的输出电压摆幅.图5(a)是传统Cherry-Hooper限幅放大器的电路图,其利用射随器作为反馈通路,驱动2管的基极-发射极电容π2,通过反馈信号,将、处原本孤立的两个低频极点形成一对共轭极点,因而提高了单级电路的带宽.

在忽略1、2和3管的基极-集电极电容μ、体电阻、输出电阻o以及基极-发射极等效电阻π的情况下,其小信号等效电路如图5(b)所示.

图5 传统CH限幅放大器

理论分析可得,其小信号增益

(5)

其中

式中:π2和π3分别为2和3管的基极-发射极电容;m2和m3分别为2和3管的跨导;L(等于π1)为输出端的负载电容.而电路的低频增益可表 示为

(6)

由式(5)可知,电路的高频零点z1≈-m3/π3不会对带宽内的增益造成影响.调节反馈信号的大小(即m3和F),可使电路工作在巴特沃斯响应下,获得最大带宽.然而,调节F的阻值会改变1的偏置,对CH电路的增益造成影响.另外,随着电压信号的不断放大,点较高的直流电平也会制约输出信号的摆幅.

为了降低输出直流电平,同时也为了拓展带宽,本文对传统CH电路进行了改进,即在输出端与射随器2的基极之间加了一个电阻2,如图6(a)所示.

同理,在忽略1、2和3管的基极-集电极电容μ、体电阻、输出电阻o以及基极-发射极等效电阻π的情况下,改进型CH限幅放大器的小信号等效电路如图6(b)所示.

图6 改进型CH限幅放大器

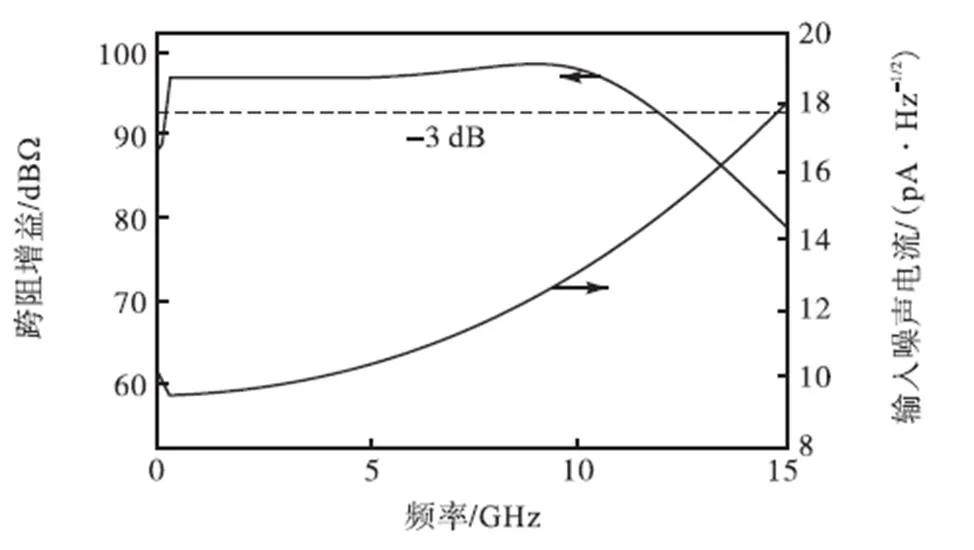

改进后电路的传输函数可表示为

(7)

其中

而电路的低频增益

(8)

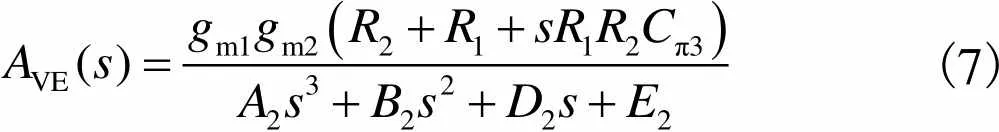

图8是改进前后CH限幅放大器的电压增益对比图.由图8可见,在低频增益相同的情况下,改进型CH电路的带宽明显提高.单级LA电路的-3,dB带宽可达18.5,GHz,而电压增益为16.9,dB.这是因为改进前后CH电路的极点基本一致,而改进后电路产生的低频零点抵消了实数极点,故相邻的共轭对主极点决定带宽.

此外,改进型CH电路具有更高的稳定性.环路稳定性的仿真结果表明,改进型CH电路的相位裕度更接近72°,稳定性更好.

在将改进型CH电路进行三级级联时,分别给予各级不同幅度的反馈,使得每级电路产生的固有频率和阻尼系数都不完全相同,故产生的共轭极点对不会重叠.这样的设计不仅能避免因完全相同的改进型CH结构级联而导致电路带宽的剧烈衰减,还能降低LA电路的频率响应尖峰,因而拓展了工作带宽[12].

图8 传统CH电路和改进后CH电路的电压增益曲线

因为光接收机前端一般由多级放大电路组成(如图1所示),例如本文中的LA采用了三级级联,所以一旦其中某级电路的直流偏置发生变化,则后级电路会将此差异不断放大,整体电路极有可能进入饱和区,导致信号传输失效[13].针对多级电路的直流偏移,通常会在电路中增加直流偏移消除电路,如图9(a)所示.

DOC电路通常需要一个大电容D来实现低截止频率的滤波器.传统设计多采用片外电容,这不仅会引入大的寄生效应,而且不利于电路的单片集成.为克服上述问题,本文利用密勒效应,使用差分有源密勒电容电路来实现大的等效电容,如图9(b)所示.图中所示电容CMA通过密勒效应放大,放大倍数为差分放大器的增益因子(1+m2,D),故等效电容值

(9)

由电阻MA和等效电容eq形成的低截止频率滤波器,将高频信号滤除,再通过1管将直流电平反馈到前级电路,进而消除直流偏移.

理论计算和仿真结果表明,本设计中仅需一个2,pF左右的MA电容即可实现1.1,MHz带宽的低通滤波器.由此可见,利用DAMC电路可避免使用大的片外电容,同时降低片外电容引入的寄生效应.与片上大电容相比,差分有源密勒电容可节省芯片面积,降低成本,增加可靠性.

2.3 输出缓冲级

在高频信号传输过程中,一般都采用特征阻抗为50,Ω的传输线,所以所设计的电路和器件的输入/输出端也都必须满足阻抗匹配,以避免信号反射,降低实际入射或传输功率.由于光接收机电路是宽带信号传输线路,故要求系统在整体带宽内都要满足良好的阻抗匹配.

目前,设计使用较多的输出缓冲级有电流逻辑型电路(CML)、T倍频器和有源电感型结构等.其中,CML电路简单有效,且输出阻抗能得到很好的保证,故本文采用CML电路作为输出缓冲级.缓冲级的负载电阻一般设置在70,Ω左右,保证22低于-15,dB.因光接收机中的跨阻放大器和限幅放大器已提供足够的增益,所以输出缓冲级的增益在0,dB左右即可.

3 仿真结果

为了实现上述模块的单片集成,本文基于IBM 0.18,µm SiGe BiCMOS 7,WL工艺(最大的传输频率为60,GHz)对整体电路进行了优化,并完成版图绘制,如图10所示.芯片核心面积720,µm×700,µm.

图10 光接收机模拟前端电路版图

图11 模拟前端电路的跨阻增益和等效输入噪声

由于高频电路的实际测试多采用网络分析仪对电路的参数进行测量,所以图12给出了模拟前端电路的参数版图后仿结果.由图可见,参数21在-3,dB带宽内极为平坦,其值约为48,dB;而参数11和22在-3,dB带宽内分别小于-10,dB和-15,dB,表明电路在输入和输出端口实现良好匹配.

图12 模拟前端电路的S参数

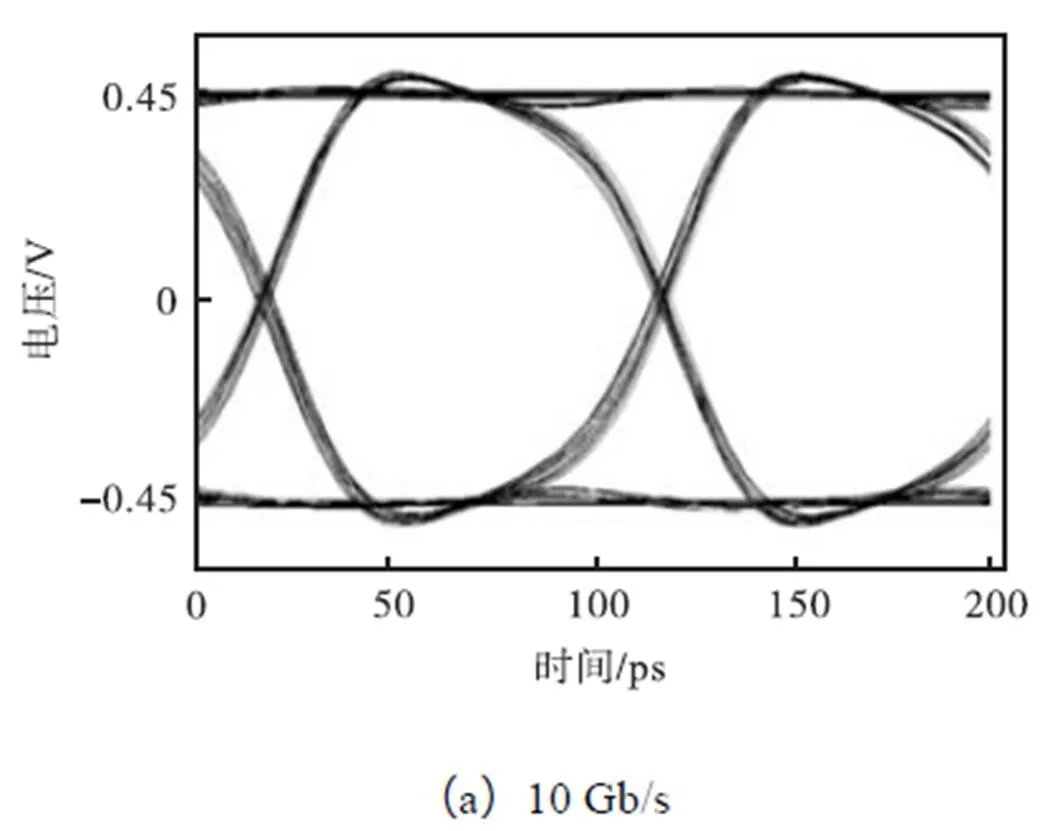

为了表征所设计模拟前端电路对信号的实际传输效果,图13给出了传输速率为10,Gb/s、12.5,Gb/s和15,Gb/s时的眼图,其输入电流为5,µA.

由图13可见,眼图的时间抖动很小,增益尖峰也不明显,眼皮较薄,整个眼图对称完整,张开程度良好,可以实现高质量的信号传输.

表1总结了本文所设计模拟前端电路的性能参数,并与其他文献报道做了对比.由表可见,本文所设计的前端电路在整体性能参数方面更具优势.

表1 光接收机模拟前端电路的性能对比

Tab.1 Performance comparison of reported optical re-ceiver analog front-end circuit

4 结 语

[1] Youn J S,Lee M J,Park K Y,et al. A 12. 5-Gb/s SiGe BiCMOS optical receiver with a monolithically integrated 850-nm avalanche photodetector[C]//. Los Angeles,California,USA,2012:1-3.

[2] Toru Y,Toshiaki T,Norio C,et al. A 20,Gbps inductorless CMOS optical receiver for short distance VCSEL based 850,nm optical links[J].,2014,78(1):43-51.

[3] Oh W S,Park K. A 12-Channel 60-Gb/s transimpedance amplifier and limiting amplifier array for OPCB applications[C]//. Marrakech,Morocco,2008:22-25.

[4] Xie Sheng,Guo Jing,Guan Kun,et al. Design and realization of InP/AlGaInAs multiple quantum well ring laser[J].2014,20(6):402-406.

[5] Huang J C,Lai K S,Hsu K Y J. A 10. 5,Gb/s transimpedance amplifier using capacitive emitter degeneration technique[J].,2009,53(8):916-919.

[6] Moeneclaey B,Verbrugghe J,Blache F,et al. A 40,Gb/s transimpedance amplifier for optical links[J].,2015,27(13):1375-1378.

[7] Brandl P,Zimmermann H. 3,Gbit/s optical receiver IC with high sensitivity and large integrated pin photodiode [J].,2013,49(8):552-554.

[8] Eissa M H,Awny A,Winzer G,et al. A wideband monolithically integrated photonic receiver in 0.25 µm SiGe:C BiCMOS technology[C]//. Lausanne,Switzerland,2016:487-490.

[9] Xie Sheng,Tao Xizi,Mao Luhong,et al. A high-Gm differential regulated cascode transimpedance amplifier [J].,2016,22(4):345-351.

[10] Kang Y Z,Mao L H,Zhang S L,et al. A 13,GHz 38,mW differential front-end amplifier based on 0.18,mm SiGe BiCMOS for 15,Gb/s optical receiver [C] //. Xi'an,China,2012:1-3.

[11] Chen L,Li Z,Wang Z. A 10-Gb/s Inductorless CMOS limiting amplifier for optic-fiber transmission system [C]//. Chengdu,China,2010:1-4.

[12] Holdenried C D,Haslett J W,Lynch M W. Analysis and design of HBT Cherry-Hooper amplifiers with emitter-follower feedback for optical communications[J].,2004,39(11):1959-1967.

[13] Huang H Y,Chien J C,Lu L H. A 10-Gb/s inductor-less CMOS limiting amplifier with third-order interleaving active feedback[J].,2007,42(5):1111-1120.

(责任编辑:王晓燕)

Analog Front-End Circuit for High-Speed Optical Receiver Based on SiGe BiCMOS Technology

Xie Sheng1,Gu Youzhi1,Mao Luhong2,Wu Sicong1,Gao Qian1

(1. Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology,School of Microelectronics,Tianjin University,Tianjin 300072,China;2. School of Electrical and Information Engineering,Tianjin University,Tianjin 300072,China)

optical receiver;transimpedance amplifier;modified Cherry-Hooper;DC offset cancellation circuit;SiGe BiCMOS

10.11784/tdxbz201612053

TN433

A

0493-2137(2018)01-0057-07

2016-12-20;

2017-05-25.

谢 生(1978— ),男,博士,副教授.

谢 生,xie_sheng06@tju.edu.cn.

国家自然科学基金资助项目(61474081).

the National Nature Science Foundation of China(No.,61474081).