高性能LDPC/Turbo码双模译码器的发展综述

2017-07-05王秀敏

王秀敏,宿 晨,单 良,王 怡,王 玉

(1. 中国计量大学 信息工程学院,浙江 杭州310018; 2. 纽约城市科技大学 计算机工程技术学院,纽约 11201)

高性能LDPC/Turbo码双模译码器的发展综述

王秀敏1,宿 晨1,单 良1,王 怡1,王 玉2

(1. 中国计量大学 信息工程学院,浙江 杭州310018; 2. 纽约城市科技大学 计算机工程技术学院,纽约 11201)

目前LDPC码和Turbo码广泛应用于3G和4G商用移动通信系统中,并且在无线局域网、光纤通信、水下通信、视频和图象的加密以及网络安全等方面也发挥着重要的作用. 由于全球在不同地区的移动通信设备只支持一种码,这使得移动通信有一定的地域局限性并影响通信质量. 因此,通过对LDPC码和Turbo码译码过程的研究与结合,实现一种高性能的LDPC/Turbo码双模译码器具有重要意义. 文章回顾了目前LDPC/Turbo码双模译码器的发展情况,并针对存在的不足进行分析和总结,最后介绍LDPC码和极化码未来发展的趋势.

LDPC/Turbo码;双模译码器;SISO计算单元;极化码

进入21世纪以来,无线通信已经基本覆盖到了全球的每一个角落,影响着我们的生活,拉近了人与人之间的距离. 数字通信系统具有抗干扰能力强、传输差错可控、可加密并保密性好等特点,并且对于不同信源的信号在传输和接收处理方面有非常好的灵活性,因而能与现代通信完美结合[1-2]. 在通信系统中最重要的就是保证信息传输的稳定、可靠[3],Gallager先生于1962年发明了一种低密度奇偶校验码(LDPC)[4], 由于当时LDPC码只有在码长较长时性能好但通信硬件条件难以满足这个需求而被忽视,直到1996年MacKay和Neal再次提出了它[5]. 在此之前,Berrou等人于1992年发明了Turbo码,同时提出了迭代译码的思想[6]. LDPC码和Turbo码都接近Shannon极限,良好的译码性能满足现代通信的需要. 实验证明当码长大于104时,LDPC码的译码性能要优于Turbo码[7].

最早详细提出LDPC码和Turbo码双模译码器设计思路是在2008年,当时Sun Yang 等人提出了一种能同时支持LDPC码和Turbo码的译码算法,以及一种支持两种码共享的软输入软输出SISO计算单元[8-9],最大化的减少逻辑资源消耗,这些成果也为之后双模的研究打下坚实基础. 2014年Carlo 提出的LDPC/Turbo码双模译码器支持深空通讯,将双模译码器的应用推向了新的高度,并且在计算单元SISO中实现了约90%的资源共享[10-11].

随着4G通信的日渐成熟人们把更多的目光投向5G的研究中,其中极化码已经与5G悄然的联系在了一起. 极化码是由Erdal 教授于2008年提出的[12],极化码在理论上可达到Shannon极限,并且在编译码设计上会有线性的复杂度变化,因而成为了研究的焦点[13].

1 LDPC/Turbo码双模译码器

1.1 双模译码器总体结构

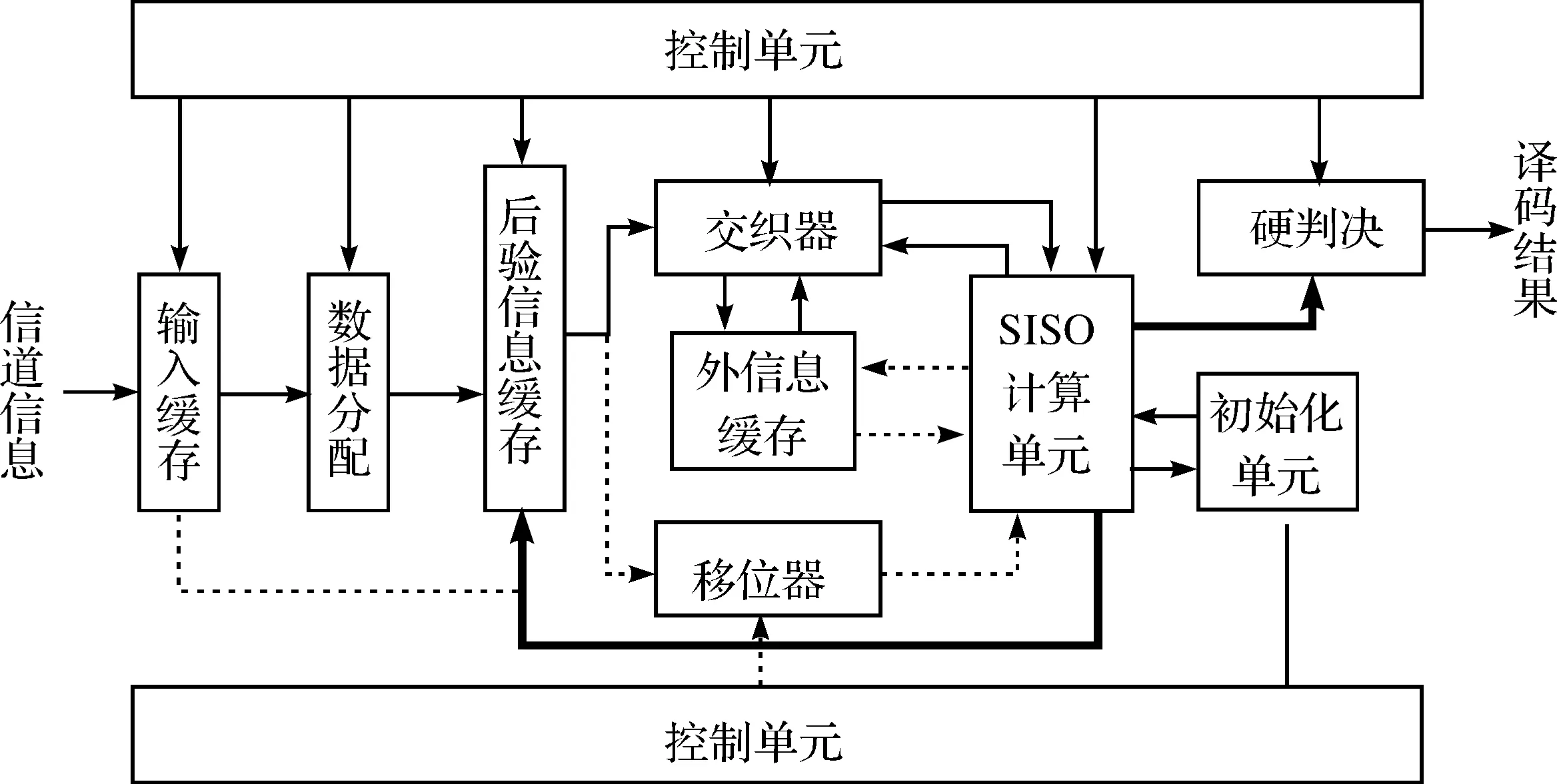

译码器总体结构设计主要基于译码过程,目前LDPC/Turbo码双模译码器中应用最广泛的算法是Turbo码的LUT-LogMAP算法和LDPC码的LUT-TDMP算法,由于两种算法在译码过程上基本一致,因此在设计中可以共享大量的计算单元. 文献[8]提出的双模译码器总体结构如图1. 该结构支持WiMAX标准下的LDPC码和TD-LTE标准下的Turbo码,图中虚线指向代表LDPC码的译码过程,实线是Turbo码的译码过程,而加粗实线为两种码共有的译码过程. 其中,交织器负责Turbo码信息的交织或解交织[14],移位器负责LDPC码信息的循环移位[15],两者的目的都是为了打乱信息序列从而去掉消息在传递过程中的关联度. 由于工作原理不同,交织器与移位器也是目前无法实现共享的模块.

图1 LDPC/Turbo码双模译码器的总体译码结构图Figure 1 Overall structure of LDPC/Turbo dual-mode decoder

1.2 存在的不足

译码器的性能主要看吞吐率、误码率和逻辑资源消耗,其中决定吞吐率的主要因素就是译码延时. 随着科技不断进步,硬件手段更加丰富,逻辑资源消耗已不是致命的问题,人们为了更好更快的通信会选择消耗较多的逻辑资源. 结合这一趋势,我们总结出目前LDPC/Turbo码双模译码器的不足如下:

1)吞吐率较低. LDPC码或Turbo码单模译码器已经可以达到3G以上的吞吐率[16-17],相比之下LDPC/Turbo码双模译码器还有很大的差距,主要原因是Turbo码最大码长要比LDPC码长,并且各自的译码并行度也有很大不同[18],因此在分块译码处理时很难减少译码延时,受影响最大的就是Turbo码.

2)译码性能一般.由于LDPC码和Turbo码目前仅能以MAP算法相结合,因此译码算法的选择受到很大的限制,无论是LUT-LogMAP算法还是LUT-TDMP算法均不是各自码中性能最好的译码算法,因而直接影响到误码率.

3)标准限制. 本文研究的双模译码器仅支持WiMAX标准的LDPC码和TD-LTE标准下的Turbo码,由于不同标准在码的构造、信道选取和译码算法等方面也会不同,因此双模译码器支持多标准的路还很长.

2 未来发展方向

2.1 LDPC/Turbo码双模译码器改进与发展

在译码器吞吐率改进上,2011年Sun Yang 等人提出了基于QPP交织器的动态交织结构,实现了实时输出交织地址从而在减少了大量存储单元的同时降低了译码延时,并使得Turbo码吞吐率达到了1 Gb/s以上[19]. Robert于2015年提出了一种高并行的Turbo码译码算法,通过滑窗结构对消息节点进行最大化的并行处理,从而实现1 Gb/s以上的吞吐率[20]. 虽然双模译码器并行度受限制,但采用以上两种方法均可使数据处理更加连续,从而减少译码延时,但应用到双模中时还要考虑资源共享. Lin于2015年提出Radix-4 SISO计算单元结构[21],该结构支持Turbo码的MAP算法和LDPC码的MS算法,通过改变消息传递网络,增加消息传递路径来提升消息传递的效率. 由于MS算法在LDPC码译码算法中性能较差,因此将该算法升级为NMS算法会使译码性能有大幅度提升,而仅提升LDPC译码算法性能会使计算单元共享率降低,因此我们尝试将Turbo码的算法也做相应的调整. NMS算法是Wu Xiaofu于2010年提出的基于归一化的MS算法,该算法在MS算法的基础上通过引入归一化因子修正状态转移函数达到比BP算法更优的译码性能[22].

由于NMS算法的译码性能也优于LUT-TDMP算法[23],因此可以尝试将归一化近似的优势结合到LUT-TDMP算法和LUT-LogMAP算法计算状态转移函数的近似中. Vanukurn于2013年提出混合算法的思想,通过对LUT-Log-MAP算法和Linear-Log-MAP算法的混合达到了比Log-MAP算法更优的译码性能[24],结合的部分为状态转移函数近似部分. 基于以上两个思想可以将文献[8]中的状态转移函数f(x,y)和max*进行查表近似和归一化近似法相结合,选取合适的归一化因子不但能够提升译码性能,还可以将乘法运算转化为移位加法的形式,这样相比查表近似还减少了逻辑资源消耗[25].

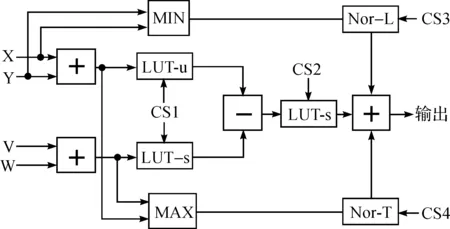

图2 支持双模译码器的NFU单元结构图Figure 2 NFU structure of dual-mode decoder

因此,可将文献[8]中的灵活的功能单元(FFU)升级为采用混合近似法处理状态转移函数的归一化功能单元(NFU),其结构如图2. 其中4个CS信号控制不同近似法,在文献[8]的查表模块LUT-u和LUT-s的基础上加入LDPC码和Turbo码各自的归一化近似单元Nor-L和Nor-T,以满足最佳的译码需求. SISO调用NFU的结构如图3所示[9],其中前后向递归单元(FBR)利用分支度量γ进行前向度量α和后向度量β的递归计算[10]. 通过加法、比较和选取单元(ACS)计算出外信息. 结合图3可以看出,采用混合近似法可以在LDPC码或Turbo码每次进行状态转移函数计算时最多可以分别减少16个和22个LUT计算,并将其替换为复杂度更低的移位加法运算[26],这样的改进不但在理论上可以提升译码性能,而且还会节省逻辑资源.

图3 基于NFU单元的SISO结构图Figure 3 Structure of SISO based on NFU

2.2 双模译码器与极化码

随着5G时代的悄然临近,极化码逐渐成为研究的重点.极化码的核心就是“信道极化”,当极化码的码长持续增加时,一部分信道的容量将趋向于1即没有误码的信道,而另一部分信道的容量则趋向于0的纯噪声信道.因此不难看出,我们将会选择在容量接近于1的信道上直接传输信息从而逼近信道容量[27]. 在极化码译码时,主要采用简单的逐次干扰抵消译码的方法,从而以较低的实现复杂度获得与最大自然译码相近的性能[28].

目前有很多学者已经对LDPC码、Turbo码和极化码的性能进行比较,发现LDPC码在中短码长的译码性能要远远优于极化码并且在码长大于104时优于Turbo码,而极化码虽然有理论上接近信道极限的性能但是也同样要求码长大于220时才行,不过考虑到极化码在编码和译码方面均有比LDPC码和Turbo码更低的复杂度因而受到了广泛认可[29].

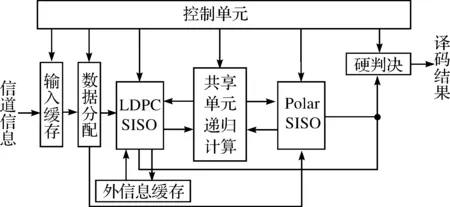

图4 LDPC/Polar码双模译码器结构Figure 4 Structure of LDPC/Polar dual-mode decoder

由于极化码同其他码的译码原理不同,因此共享计算单元会非常复杂. 但是随着研究的不断深入,更多的共性将会被挖掘出来.例如,极化码和LDPC码均可用于AWGN信道,并且极化码SC译码算法及其改进算法也涉及到消息传递的递归计算,这点同LDPC码的前后向度量递归计算的过程类似. 因此,可以构想一种LDPC/Polar码双模译码器如图4所示,根据控制单元和数据分配来对不同码长的码字选取最佳的译码方式,目的是对于中短码长的码字进行LDPC码译码,而较长码长则采用极化码译码[30],这样的译码器相比LDPC码与极化码的级联会有很大的优势. 由于大多极化码译码算法不需要迭代,因此极化码SISO单元仅需要内部存储并没有与外信息缓存相连[31].

3 概括与总结

本文针对当前LDPC/Turbo码双模译码器的研究现状,结合它的不足提出改进想法,目的是为了提升双模译码器的吞吐率和译码性能并减少逻辑资源消耗. 同时,结合5G时代的到来以及极化码的不断深入研究,提出一种LDPC/Polar码双模译码器模型,该译码器可以完成对不同码长的码字以最佳的译码方案译码. 目前由于LDPC码和极化码联合后其共享模块较少,因此找到更多LDPC码与极化码在计算单元的共享方案也是后续研究的主要内容之一.

[1] SHENG G, ZHAO X Y, ZHANG H D, et al. Mathematical models for simulating coded digital communication: a comprehensive tutorial by big data analytics in cyber-physical systems[J]. IEEE Journals & Magazines,2016,4(1):9018-9026.

[2] SUN S L, KADOCH M, GONG L, et al. Integrating network function virtualization with SDR and SDN for 4G/5G networks[J]. IEEE Journals & Magazines,2015,29(3):54-59.

[3] FENG L X, PENG J, CHEN G R, et al. Communication channel analysis and simulation of medical implanted electronic devices based on the volume conduction[C]//15th International Conference on Cognitive Informatics & Cognitive Computing. USA: IEEE Press,2016:423-431.

[4] GALLAGER R. Low-density parity-check codes[J]. IEEE Transactions on Information Theory,1962,8(1):21-28.

[5] DAVEY M, MACKAY D. Low-density parity check codes over GF(q)[J]. IEEE Communications Letters,2002,2(6):165-167.

[6] BERROU C, GLAVIEUX A, THITIMAJSHIMA P. Near Shannon limit error-correcting coding and decoding: Turbo-codes [C]// Communications, ICC ’93 Geneva, Technical Program. USA: IEEE Press,1993:1064-1070.

[7] BAEK C, JUNG J. A study on turbo equalization for MIMO system based on LDPC codes[C]// Eighth International Conference on Ubiquitous and Future Networks (ICUFN). USA: IEEE Press,2016:501-504.

[8] SUN Y, CAVALLARO J R. A flexible LDPC/Turbo decoder architecture[J]. Journals of Sign Process Systems,2011,64(1):1-16.

[9] SUN Y, CAVALLARO J R. Unified decoder architecture for LDPC/turbo codes[C]// IEEE Workshop on Signal Processing Systems. USA: IEEE Press,2008:13-18.

[10] CARLO C, GUIDO M. Unified Turbo/LDPC code decoder architecture for deep-space communications[J]. IEEE Transactions on Aerospace and Electronic Systems,2014,50(4):3115-3125.

[11] CARLO C, MAURIZIO M, GUIDO M. VLSI implementation of a Multi-Mode Turbo/LDPC decoder architecture[J]. IEEE Transactions on Circuits and Systems I: Regular Papers,2013,60(6):1441-1454.

[12] ERDAL A. A performance comparison of polar codes and Reed-Muller codes[J]. IEEE Communications Letters,2008,12(6):447-449.

[13] SYED M A, FAN Y Z, CHEN J, et al. High-Throughput and Energy-Efficient belief propagation polar code decoder[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2017,25(3):1098-1111.

[14] JYRKI L, JONGHOON R, EEVA S. On the degree of the inverse of quadratic permutation polynomial interlreavers[J]. IEEE Transactions on Information Theory,2012,58(6):3925-3932.

[15] DAESUN O, KESHAB K P. Low-Complexity switch network for reconfigurable LDPC decoders[J]. IEEE transactions on very large scale integration(VLSI systems),2010,18(1):85-94.

[16] SACHIN K, RAHUL S, NIKUNJ D, et al. High-Throughput LDPC-Decoder architecture using efficient comparison techniques & dynamic Multi-Frame processing schedule[J]. IEEE Transactions on Circuits and Systems I: Regular Papers,2015,62(5):1421-1430.

[17] RAHUL S, ROY P P. High-Throughput turbo decoder with parallel architecture for LTE wireless communication standards[J]. IEEE Transactions on Circuits and Systems I: Regular Papers,2014,61(9):2699-2710.

[18] SHAHRIAR S, JANNE J, MUHAMMET F B, et al. Design of a unified transport triggered processor for LDPC/turbo decoder[C]// Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XIII). USA: IEEE Press,2013:288-295.

[19] SUN Y, CAVALLARO J R. Efficient hardware implementation of a highly parallel 3GPP LTE/LTE-advance Turbo decoder[J]. Intergation, the VLSI Joural,2011,44:305-315.

[20] ROBERT G M. A Fully-Parallel Turbo Decoding Algorithm[J]. IEEE Transactions on Communications,2015,63(8):2762-2775.

[21] LIN C H, YU C S. Multi-mode radix-4 SISO kernel design for Turbo/LDPC decoding[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2015,23(10):2256-2267.

[22] WU X F, SONG Y, JIANG M, et al. Adaptive-Normalized/Offset min-sum algorithm[J]. IEEE Communications Letters,2010,14(7):667-669.

[23] ZHAO M, ZHANG X L, ZHAO L, et al. Design of a high-throughput QC-LDPC decoder with TDMP scheduling[J]. IEEE Transactions on Circuits and Systems II: Express Briefs,2015,62(1):56-60.

[24] VANUKURU H R, AKSHAY S, NIGAR S. A composite sub-optimal approach for hardware implementation of turbo decoder[C]// 2013 IEEE International Conference on Communications (ICC). USA: IEEE Press,2013:4515-4519

[25] 张顺根,仰枫帆.基于FPGA的随机构造QC-LDPC分层译码器设计[J].无线电通信技术,2015,41(1):41-45.

ZHANG S G, YANG F F. Design on randomly constructed QC-LDPC layered decoder based on FPGA[J]. Radio Communications Technology,2015,41(1):41-45.

[26] 卢海芹,仰枫帆.基于FPGA有限域构造的QC-LDPC分层译码器设计[J].电子科技,2015,28(2):78-82. LU H Q, YANG F F. Design of QC-LDPC layered FPGA decoder based on the structure of finite fields[J]. Electronic Science & Technology,2015,28(2):78-82.

[27] YANG G Y, ZHUANG M J. Achieving the secrecy capacity on strong security using LT code with polar code pre-coding[C]// 2016 10th IEEE International Conference on Anti-counterfeiting, Security, and Identification (ASID). USA: IEEE Press,2016:53-57.

[28] SUN S H, CHO S G, ZHANG Z Y. Error patterns in belief propagation decoding of polar codes and their mitigation methods[C]// 2016 50th Asilomar Conference on Signals, Systems and Computers. USA: IEEE Press,2016:1199-1203.

[29] IDO T. On the construction of polar codes for channels with moderate input alphabet sizes[J]. IEEE Transactions on Information Theory,2017,63(3):1501-1509.

[30] SYED M A, FAN Y Z, CHEN J, et al. High-throughput and energy-efficient belief propagation polar code decoder[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2017,25(3):1098-1111.

[31] ZHANG Y X, YANG Z, LIU A J, et al. Secure transmission over the wiretap channel using polar codes and artificial noise[J]. IET Communications,2017,11(3):377-384.

A development overview of high-performance LDPC/Turbo dual-mode decoders

WANG Xiumin1, SU Chen1, SHAN Liang1, WANG Yi1, WANG Yu2

(1. College of Information Engineering, China Jiliang University, Hangzhou 310018, China; 2. College of Computer Engineering Technology, New York City College of Technology, New York 11201, USA)

LDPC codes and Turbo codes are widely used in the commerce of 3G and 4G mobile communication systems and play an important role in wireless LAN, optical fiber communication, underwater communication, video and image encryption and network security. Global mobile devices in different regions only support one code. Domain limitation in mobile communication affects the quality of communication. Therefore, it is very important to realize a high-performance LDPC/Turbo dual-mode decoder by combining the LDPC and Turbo codes in the decoding process. This paper reviews the development of LDPC/Turbo dual-mode decoders, analyzes and summarizes the shortcomings of the decoder, and introduces the trend of future development for LDPC and polar codes.

LDPC/Turbo code; dual-mode decoder; SISO calculation unit; polar code

2096-2835(2017)02-0203-05

10.3969/j.issn.2096-2835.2017.02.011

2017-03-13 《中国计量大学学报》网址:zgjl.cbpt.cnki.net

国家自然科学基金资助项目(No. 61379027),国家自然科学青年基金资助项目(No. 51404223),浙江省自然科学青年基金资助项目(No.LQ14E060003).

王秀敏(1963-),女,辽宁省锦州人,教授,主要研究方向为电子信息与通信.E-mail:wxm6341@163.com

TN91

A