MVB控制器校验序列FPGA设计

2016-12-13常玉琪胡黄水王宏志

常玉琪,胡黄水,2*,王宏志,王 莹

(1.长春工业大学 计算机科学与工程学院,吉林 长春 130012;2.吉林大学 通信工程学院,吉林 长春 130022)

MVB控制器校验序列FPGA设计

常玉琪1,胡黄水1,2*,王宏志1,王 莹1

(1.长春工业大学 计算机科学与工程学院,吉林 长春 130012;2.吉林大学 通信工程学院,吉林 长春 130022)

分析了多功能车辆总线控制器的校验序列,基于MVB控制器CRC循环冗余校验和偶校验基本原理,设计了一个串行CRC校验模块。以Quartus II软件作为开发平台,采用VHDL硬件语言进行编程,在FPGA中成功实现了CRC编码设计,并得出了校验序列的正确仿真波形。

多功能车辆总线;CRC;FPGA;可靠性

0 引 言

多功能车辆总线(Multifunction Vehicle Bus,MVB)是一种高可靠性的实时通信总线,主要用于车辆电气设备互联通信。为满足通信的准确性和可靠性,在总线中设计一个具有很强检错纠错能力的校验序列显得尤为重要[1-2]。

目前,国内外学者已对CRC校验进行了许多研究,文献[3]根据MVB标准选择串行计算方法设计了由一组移位寄存器和异或单元组成的CRC发生电路;文献[4]提出了一种简单通用的CRC并行计算实现方法,适用于各种不同的CRC生成多项式和各种不同的信息码宽度;文献[5]介绍了串行CRC检验原理和并行CRC检验原理,并对两种实现方式进行了性能对比。

目前MVB控制器校验序列的研究比较单一,通常是研究在列车通信网络(Train Communication Network,TCN)协议的基础上设计的串行或并行CRC校验方法。文中提出的串行CRC校验方法,既能够在较高的时钟频率下进行CRC校验码的计算,又可以提高生成CRC校验码的速度。用VHDL硬件语言在FPGA中实现了MVB控制器校验序列的生成,并通过仿真分析验证了该方法的可行性。

1 MVB校验序列

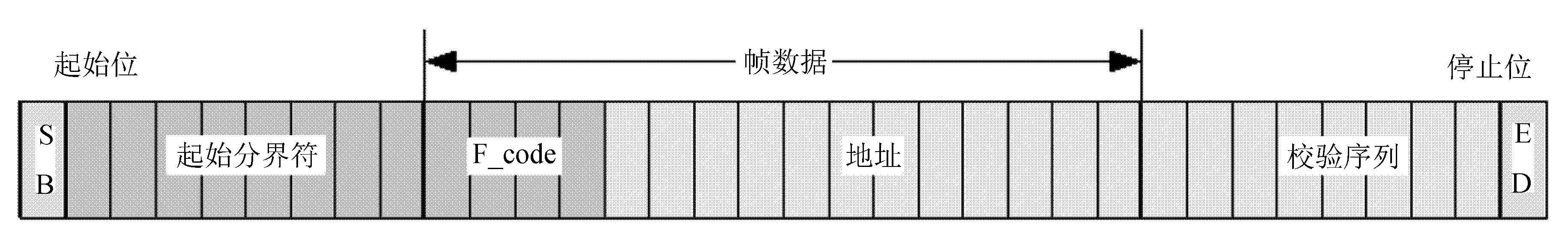

MVB总线能够传输两种类型的帧,一种是由总线主发送的主帧,另一种是从设备响应主帧而发送的从帧。主帧是以主起始分界符开始,其后是16位的帧数据,紧接着是8位校验序列,最后以终止分界标识符结束,如图1所示。

图1 主帧格式

从帧是以从起始分界符开始,接着为16、32、64、128或256位帧数据,在每64个数据位后包含一个8位的校验序列,或当帧数据只有16或32位时,将一个8位的校验序列附加其后,最后以终止分界符结束,如图2所示。

图2 从帧格式

帧数据应用一个或者更多的8位校验序列来保护,校验序列用于被其保护的16、32或64位数据的循环冗余校验(CRC)。校验序列应按如下的多项式公式计算[6]:

G(x)=x7+x6+x5+x2+1

7位余数结果应用一个偶校验位扩展,最后将所有的8位数据反向发送。

2 校验模块的设计

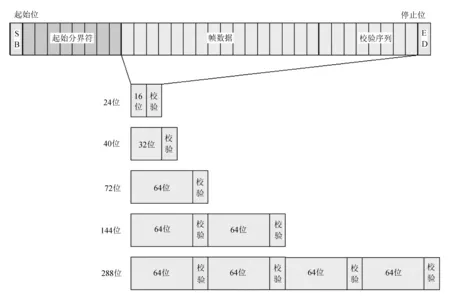

校验模块的设计采用VHDL硬件描述语言,选用Altera公司生产的FPGA芯片,例如Cyclone IV系列芯片,并且利用Quartus II和ModelSim开发软件进行开发和仿真CRC的串行处理算法。CRC串行校验模块主要由复位(RESET_IN)、时钟(CLOCK_IN)、串行数据输入(SDATA_IN)、帧长(FRAME_L)、发送CRC命令位(SEND_CRC)这5个输入以及CRC串行数据输出(CRC_OUT)组成。CRC串行算法流程如图3所示。

图3 CRC模块程序设计流程

FRAME_L的值有000、001、010、011、100,分别对应数据帧长为16、32、64、128、256位,相应的字计数器WORD_COUNTER的值分别对应为1、2、4、8、16。

3 仿真分析

以发送一个16位帧数据为例,SDATA_IN=“0111111011000011”,CRC生成多项式为11100101,所得余数0010001经过偶校验位扩展成00100010,由此可得8位反向校验序列CS=11011101。按照上述设计过程,采用VHDL语言编程。设计中程序的主过程代码如下:

IF RESET_IN='0' THEN

CN:=15;

CHECK_EVEN:='0';

CRC_END:='0';

SCRC_OUT<="00000000";

CRC_EN:='1';

CRC_POLY:="11100101";--生成多项式为x^7+x^6+x^5+x^2+1

SBUFF_OUT<="0000000000000000";

ELSIF RISING_EDGE(CLOCK_IN) THEN

IF CRC_EN='1' THEN

DATA_BUFFER(CN):=SDATA_IN;

--先存高位

IF CN=0 THEN

接收16位数据结束

CN:=15;

CRC_END:='1';

CRC_EN:='0';

END IF;

CN:=CN-1;

SBUFF_OUT<=DATA_BUFFER;

END IF;

END IF;

IF CRC_END='1' THEN

CRC_BUFFER:=DATA_BUFFER(15 DOWNTO 8);

FOR I IN 15 DOWNTO 0 LOOP

IF CRC_BUFFER(7)='1' THEN

--最高位为1才异或

CRC_BUFFER(7 DOWNTO 0):=CRC_BUFFER(7 DOWNTO 0) XOR CRC_POLY(7 DOWNTO 0);

--按位异或

END IF;

CRC_BUFFER(7 DOWNTO 0):=CRC_BUFFER(6 DOWNTO 0) & DATA_BUFFER(7);

--左移1位

DATA_BUFFER(15 DOWNTO 0):=DATA_BUFFER(14 DOWNTO 0) & '0';

--左移1位

END LOOP;

CRC_BUFFER(0):='0';

FOR I IN 7 DOWNTO 1 LOOP

CHECK_EVEN:=CHECK_EVEN XOR CRC_BUFFER(I);

--偶校验

END LOOP;

CRC_BUFFER(0):=CHECK_EVEN;

CRC_BUFFER(7 DOWNTO 0):=NOT CRC_BUFFER(7 DOWNTO 0);

--取反即为最终的校验值 (7位CRC,加上1位偶校验,再取反)

SCRC_OUT<=CRC_BUFFER;

CHECK_EVEN:='0';

CRC_END:='0';

END IF;

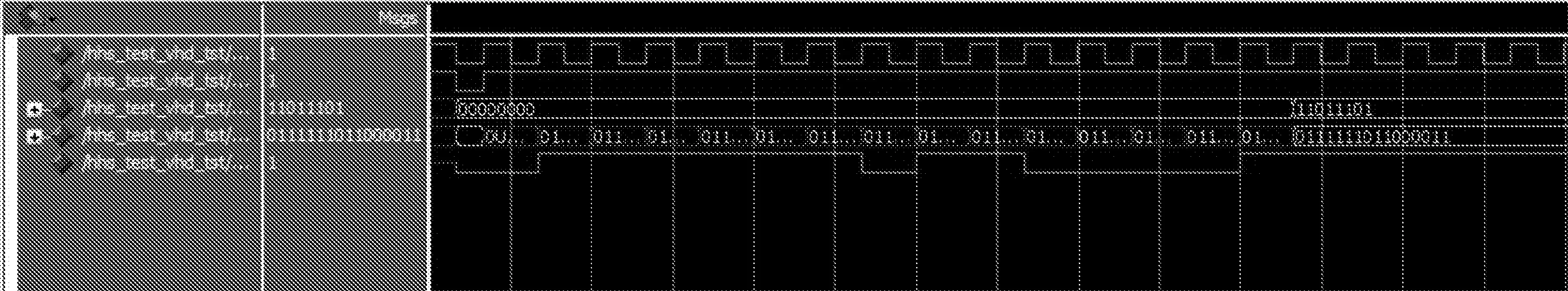

本设计使用Quartus II调用ModelSim进行时序仿真,系统仿真波形如图4所示[7]。

图4 CRC仿真结果

仿真中采用的待校验数据为16位数据(0111111011000011)[8],可以看到最后输出的CRC校验序列的值为11011101,与理论值相符。由此看出,该设计能正确实现MVB帧中CRC编码功能。

4 结 语

在遵从网络协议的基础上[9],分析了MVB帧的构成和CRC编码原理后,用VHDL硬件描述语言实现了对MVB帧格式中CRC校验码的设计,同时给出了串行CRC的设计流程,最后对MVB帧中CRC检验码的生成过程进行了仿真,仿真波形证明了设计的正确性。CRC编码模块的成功实现为MVB总线在国内机车上的应用提供了基础。

[1] 幸柒荣,林知明,温小旭.MVB总线中校验序列的编码设计[J].工业控制计算机,2009(9):59-60.

[2] 李中奇,杨丰萍,郭万岭,等.多功能车辆总线控制器编码器设计[J].华东交通大学学报,2009,26(6):52-56.

[3] 魏耀南,林品,唐允宝.MVB帧收发模块设计[J].机车电传动,2010(3):26-29.

[4] 王海光.并行CRC算法硬件实现研究与VHDL设计[J].漳州师范学院学报:自然科学版,2007,20(4):51-56.

[5] 谷小刚,陈长龄,杨战平.CAN协议中CRC编码的硬件实现[J].计算机与信息技术,2006(5):60-61.

[6] [Anon]. IEC.IEC61375-1-1999 Electric railway equipment-train bus-part 1:train communication network[S].Genva:IEC,1999.

[7] 陈玉泉.一种并行CRC算法的实现方法[J].现代电子技术,2005,28(22):21-23.

[8] 徐士强.MVB通信协议可配置冗余码校验电路的FPGA实现[J].电子技术与软件工程,2015(19):48-51.

[9] 胡远朋,王宏志,胡黄水.基于FPGA全功能MVB网络从设备链路层IP核设计[J].长春工业大学学报,2016,37(1):20-24.

FPGA based MVB controller check sequence design

CHANG Yuqi1,HU Huangshui1,2*,WANG Hongzhi1,WANG Ying1

(1.School of Electrical & Electronic Engineering,Changchun University of Technology,Changchun 130012,China;2.Department of Communication Engineerings,Jilin University,Changchun 130022,China)

By analyzing the check sequence of Multifunction Vehicle Bus (MVB) controller,a CRC check module is designed based on MVB cycle redundancy and odd-even test principle. With Quartus II as platform,we implement CRC code in FPGA with VHDL hardware language and verify the waveform of check sequence.

Multifunction Vehicle Bus (MVB); CRC; FPGA; reliability.

2016-03-14

吉林省发改委经济结构战略调整引导资金专项项目(2014Y125);吉林省教育厅“十二五”科学技术研究项目(吉教科合字(2015)第100号);吉林省科技厅科技攻关计划项目(20140204037GX)

常玉琪(1992-),女,汉族,河南洛阳人,长春工业大学硕士研究生,主要从事列车网络通信技术方向研究,E-mail:yuqi.chang@outlook.com. *通讯作者:胡黄水(1974-),男,汉族,湖南隆回人,长春工业大学副教授,博士,主要从事无线传感器网络和轨道车辆动力学方向研究,E-mail:huhs08@163.com.

10.15923/j.cnki.cn22-1382/t.2016.5.11

U 285.5

A

1674-1374(2016)05-0470-04