OOFDM-PON系统的FFT/IFFT字长联合优化设计与实现

2016-10-20王凯吴琦李家齐薛子威张俊杰

王凯,吴琦,李家齐,薛子威,张俊杰

(上海大学通信与信息工程学院,上海 200444)

OOFDM-PON系统的FFT/IFFT字长联合优化设计与实现

王凯,吴琦,李家齐,薛子威,张俊杰

(上海大学通信与信息工程学院,上海 200444)

在基于现场可编程门阵列(field programmable gate array,FPGA)平台实现的实时光正交频分复用无源光网(optical orthogonal frequency division multiplexing-passive optical network,OOFDM-PON)系统中,由于实时全并行快速傅里叶变换/快速傅里叶反变换(fast Fourier transform/inverse fast Fourier transform,FFT/IFFT)模块计算复杂度高,成为实时OOFDM-PON系统设计的主要瓶颈之一.构建OOFDM-PON发送与接收仿真平台,通过联合优化OOFDM-PON发送端的IFFT与接收端FFT蝶形运算的旋转因子和输出字长来降低模块的系统逻辑资源占用率.采用基于缩短字长界限范围的方法来减少最优化字长的搜索时间,同时构建了实时OOFDM-PON系统的基于DIF-2的64点IFFT/FFT的字长优化映射表.该映射表在离线OOFDM-PON平台上的验证结果与仿真结果之间的误差控制在0.5 dB,验证了该优化算法的正确性.与Spiral设计方案相比,该设计的基于上述映射表的FFT模块可以节约大约37.2%的逻辑资源.

光正交频分复用无源光网;快速傅里叶变换/快速傅里叶反变换;字长优化;反向误差向量幅度

自从提出光正交频分复用无源光网(optical orthogonal frequency division multiplexingpassive optical network,OOFDM-PON)的思路后[1],OOFDM-PON在光通信领域引起了广泛的关注.为了验证实时OOFDM-PON的通信性能以及评估实时OOFDM-PON的算法复杂度,国内外多家学术机构开发了实时OOFDM-PON的演示平台[2-5].然而随着OOFDMPON系统中模拟数字转换器/数字模拟转换器(analog-to-digital converter/digital-to-analog converter,ADC/DAC)采样频率(达到10GS/s)以及子载波数(1024)的提升,OOFDM-PON算法所占用的资源尤其是OOFDM-PON中的快速傅里叶反变换(inverse fast Fourier transform,IFFT)计算已经达到了现有顶级现场可编程门阵列(field programmable gate array,FPGA)资源的82%[3].因此,OOFDM-PON的快速傅里叶变换/快速傅里叶反变换(fast Fourier transform/IFFT,FFT/IFFT)算法占用的逻辑资源已经成为制约OOFDM-PON实时系统演示的主要瓶颈之一.

在如何减少FFT/IFFT运算占用逻辑资源方面,国内外已经开展了大量的相关研究.在低吞吐率的应用场景下,FFT/IFFT的优化主要聚焦在结构上的优化上,文献[6]使用的就是采取单路径延迟反馈方式来减少存储器资源的使用,但基于串行结构的FFT/IFFT会产生比较大的运算延迟,不能满足实时OOFDM系统对FFT/IFFT算法高吞吐率的需求.在现有的实时OOFDM-PON演示系统中,FFT/IFFT的设计与实现大多采用Spiral IP核[7],用户可以通过在线网站输入系统设计参数(如FFT点数、蝶形结构等),生成所需要的FFT/IFFT逻辑代码.基于Spiral的FFT/IFFT在线设计所采用的旋转因子为固定字长,而且没有优化FFT/IFFT每级蝶形的输出字长.

为满足高速实时的系统要求,IFFT/FFT需要采用全并行流水线结构.此时减少使用系统资源的主要策略是对IFFT/FFT的字长进行优化.在FFT字长优化方面,主要考虑如何合理地分配蝶形运算中每级输出字长.文献[8]使用了仿真实验的方法优化8 192点FFT处理器,结果表明在蝶形运算前面几级提升字长和对数据字长进行截断操作(scaling)可以很好地权衡运算准确性和硬件资源;文献[9]使用了一种统计错误分析和仿真实验混合的方式优化了IFFT和FFT处理器,并且提供了一种可以有效减少搜索时间的方法;文献[10]仅仅考虑了128点FFT以及IFFT最后一级对OFDM收发系统的影响;文献[11]对实时OOFDMPON系统的发送端IFFT运算进行了输出字长和旋转因子字长的优化,接收端的FFT处理采用浮点型操作;文献[12]对基于DIT-2结构的32点FFT/IFFT进行了联合优化设计,但没有提及字长优化策略,且缺乏实际平台的验证.

本研究所采用的实时OOFDM-PON硬件平台是在DIF-2的64点IFFT/FFT算法[5]的基础上,结合IFFT与FFT的每级输出以及旋转因子字长的联合优化,提出了一种减少仿真时间的字长搜索算法,并在实际平台上进行了验证.

1 仿真模型建立

图1是本研究采用的仿真模型框图.在发射端,数据源采用伪随机二进制码(pseudo random binary sequence,PRBS),通过正交振幅调制(quadrature amplitude modulation,QAM)映射,然后构成64点IFFT所需要的并行输入信号,并行输入采用施密特共轭对称信号以生成仅包含实部的OFDM符号,再通过添加循环前缀和长短训练序列来组成OFDM帧信号,最后通过DAC量化将数据转换成模拟信号在信道上传输.在接收端,ADC将模拟信号转换成数字信号,根据长短训练序列完成帧信号的同步以及信道估计,再通过64点FFT将OFDM符号数据转化为QAM信号.本研究利用接收QAM信号的反向误差向量幅度(inverse error vector magnitude,IEVM)(理想信号平均功率的均方根值与误差矢量信号平均功率的均方根值之比)作为系统性能的衡量标准.

图1 仿真模型框图Fig.1 System setup blocks

从图1可以看出,影响系统最终输出信号质量的因素主要有IFFT/FFT模块的运算准确度和ADC/DAC量化误差.为独立分析IFFT/FFT模块内部数据的字长和IEVM的关系,本研究先使用浮点型的IFFT/FFT进行仿真,分析ADC/DAC量化误差带来的影响,为后面的字长优化提供参考.考虑到实际的OOFDM-PON中DAC与ADC的位宽一般都保持一致[2,11],因此本研究分析的DAC采用与ADC同样的位宽.

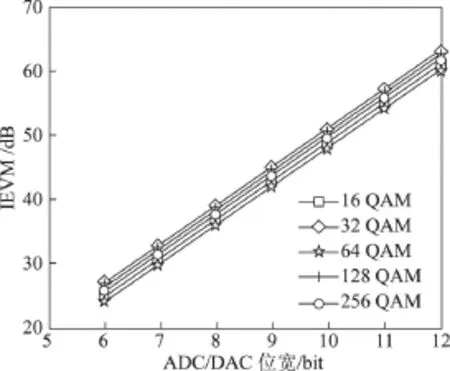

图2描述了在16~256 QAM映射方式下,不同的ADC/DAC位宽和系统接收端IEVM数值的关系.从图中数据得到如下结论:①在同一种QAM调制格式下,系统IEVM和ADC/DAC量化位宽基本呈线性的关系,ADC/DAC位宽每增加1bit,相应的IEVM数值就会增大约6dB;②在相同的ADC/DAC量化位宽情况下,不同的QAM映射的系统IEVM基本上没有什么影响.值得注意的是,上述结果是在采用浮点型的IFFT/FFT情况下得到的,故上述仿真结果可以作为后续字长优化搜索的理论IEVM的上限(IEVMideal).

图2 系统IEVM和ADC/DAC位宽的关系Fig.2 Transceiver IEVM vs.ADC/DAC resolution

2 字长优化

为了减少实时OOFDM-PON系统逻辑资源的消耗,通常在实际平台中采用定点计算实现FFT/IFFT运算[2-5].在本研究中,64点FFT/IFFT运算采用基于DIF-2的结构,该FFT/IFFT结构一共包括6级蝶形运算.对于每一级蝶形运算而言,旋转因子的字长以及每级蝶形运算的输出字长都会对FFT/IFFT的计算精度造成影响,使得系统的IEVM小于IEVMideal.考虑到OOFDM-PON接收系统的最优IEVM小于40dB[4-5],结合图2仿真所得到的IEVMideal,本研究将IEVMideal的90%(IEVMdown)作为字长优化的依据.

由于采用DIF-2的64点FFT/IFFT最后2级蝶形运算仅仅进行简单的加减运算,每级运算结果的输出字长增加一位即可,因而无需进行优化.为了使FFT/IFFT运算的逻辑设计规整,在64点FFT/IFFT的其余4级蝶形运算中,每级蝶形运算的旋转因子字长都保持一致,且输出字长也保持一致.基于图1的OFDM系统联合优化共计需要16个优化参数(FFT/IFFT分别有4级旋转因子以及4级输出字长),若本研究采用InterrCore(TM)i5-2320 CPU 3.00 GHz性能的处理器,则100次的仿真需要约4min,16个参数完成遍历搜索所消耗的时间是不切实际的(大约几个月的时间),因此采用遍历搜索字长在实际仿真中不现实.为了减少字长优化搜索的时间,本研究提出了一种基于字长集搜索的方法.

2.1 字长集上限搜索流程

本研究提出了一种基于字长集搜索的方法,该方法的实现流程如图3所示.首先把64点FFT/IFFT的每级旋转因子以及输出字长设置为6,并将其作为搜索的初始字长集{binitial},如表1中的第一次搜索集合.根据该初始化字长集计算系统的IEVM,然后判断该结果是否小于IEVMdown,如果上述条件满足,则把字长集进行加1操作(如表1的第二次搜索字长集),直到设定的字长集满足系统的IEVM需求(即IEVM>IEVMdown),该字长集称为{bceiling}.

图3 搜索字长上限流程Fig.3 Computing procedure adopted in numerically identifying the bit resolution upper boundary

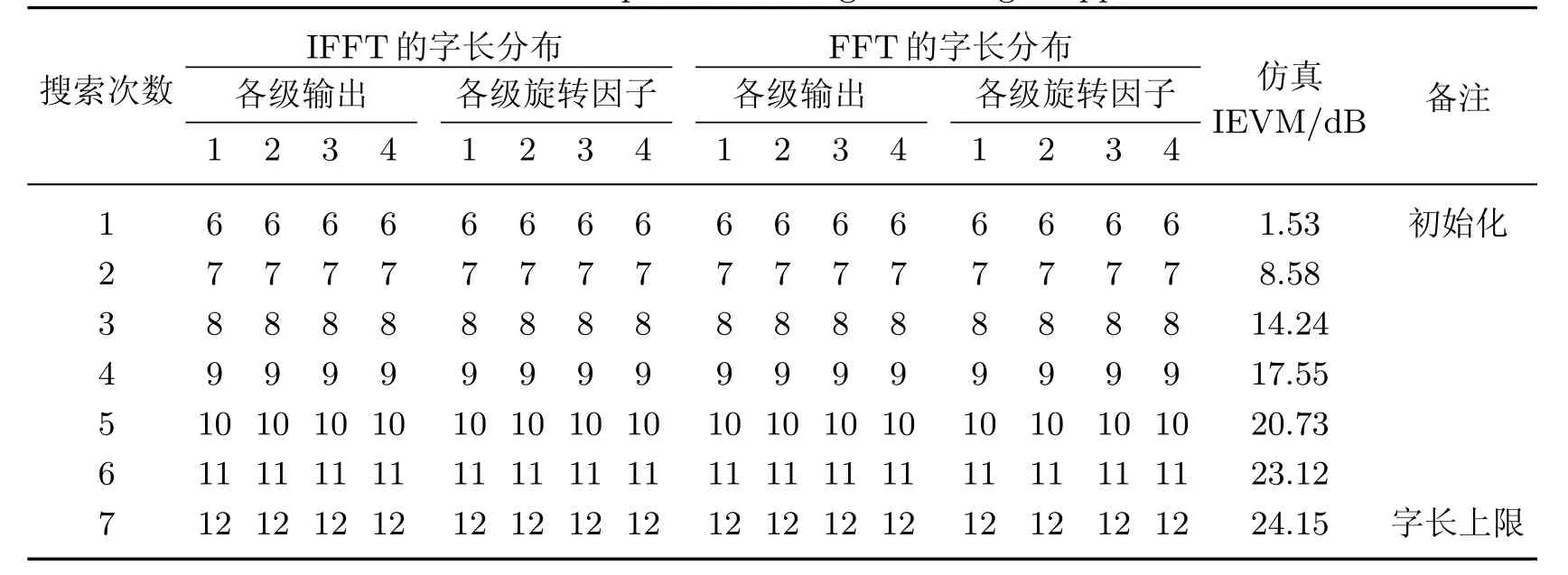

表1给出了一个寻找字长上限的实例.系统ADC/DAC量化位宽采用6bit,系统要求的IEVMdown=24.037 dB;系统初始统一字长为6,通过6次计算就找到了系统的字长上限.

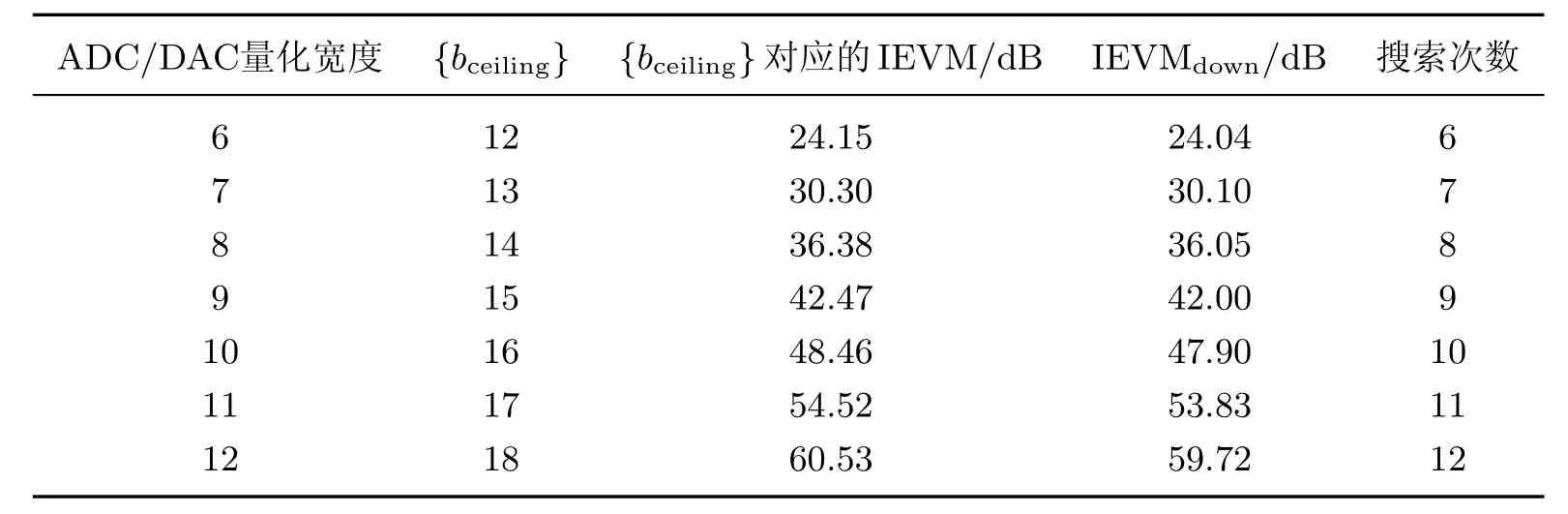

表2是针对不同ADC/DAC量化位宽所对应的字长上限映射表.从表2可以看出,针对不同位宽的ADC/DAC,其字长搜索次数仅与ADC/DAC量化位宽呈线性关系,根据该字长搜索上限所计算的系统IEVM满足本研究设计需求.

2.2 最优化字长搜索

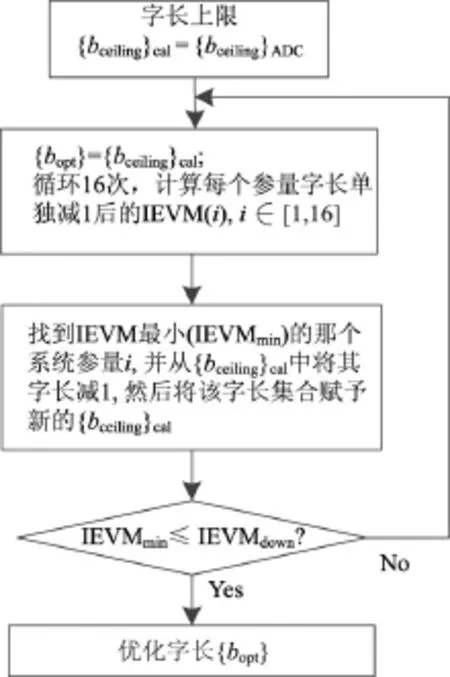

显然表2的结果仅给出了满足所设约束(IEVM>IEVMdown)的一个上限,并不是字长的最优结果,为了在此基础上进一步对字长进行优化,本研究给出了字长优化搜索的流程(见图4).该字长优化方法实现分为如下几个步骤.

表1 一个搜索字长上限的实例Table 1 An example of searching word-length upper-band

表2 字长上限搜索结果Table 2 Results of word-length upper-band

步骤1 当OOFDM-PON系统的ADC/DAC量化位宽确定了以后,根据表2获取64点FFT/IFFT的各级字长上限{bceiling}ADC,然后把该字长上限传递给待优化的字长集{bceiling}cal,以供后续流程进行字长优化.

步骤2 首先把上述字长传递给系统的优化字长{bopt},然后对64点FFT/IFFT的各级旋转因子以及输出共16个参变量对收发系统的单独影响进行分析,方法针对每一个参变量,从{bceiling}cal中减去其对应的字长,然后计算收发系统的IEVM,并循环16次获取16个参变量所对应的IEVM.

步骤3 对上述16个参变量获取的IEVM进行排序,并根据上述排序结果获取最小的IEVM所对应的参变量,然后把该参变量的字长减1,并把获取到的新的字长集赋予{bceiling}cal.

步骤4 判断IEVMmin是否满足本研究所设定的判断依据,如果不满足则从步骤2进行循环.

步骤5 如果上述条件满足,则在步骤2获取的{bopt}就是最优的字长集合.

针对不同的ADC/DAC量化位宽,本研究进行了大量的仿真,得到了如图5所示的字长映射表.图5(a)和(b)是发射端IFFT蝶形各级输出字长和旋转因子的优化结果,(c)和(d)是接收端FFT蝶形各级输出字长和旋转因子的优化结果.本研究采用的是DIF-2的64点IFFT/ FFT结构,理论上需要对6级蝶形的旋转因子和输出字长进行优化.但是由于DIF结构的最后两级蝶形仅进行简单的加减运算,每级运算结果的字长增加一位即可,故图5中没有列出后面两级字长的优化结果.

图4 优化字长搜索流程Fig.4 Computing procedure to optimize the word-length

图5 基于ADC/DAC量化位宽的字长优化结果Fig.5 Word-length optimization results based on ADC/DAC bits

分析图5(a)和(c)中的结果,可见优化的IFFT和FFT蝶形各级输出字长和ADC/DAC量化位宽近似呈线性关系,这种线性关系产生的原因为FFT/IFFT的每级输出以及旋转因子的字长对系统IEVM的单独影响呈线性关系[12].字长每增加1位,系统IEVM性能提升约6dB,而ADC/DAC的字长对系统IEVM也产生同样的影响.因此若假设上述参数对系统的影响相互独立,则在满足设定的情况下,根据图1所建立的模型不难得出系统的映射表字长与ADC/DAC的量化字长呈线性关系.图5的优化字长映射表也验证了上述假设.在ADC/DAC位宽相同的条件下,FFT的输出字长通常比IFFT的输出字长增加大约2位.从图5(b)和(d)可以看出,基于ADC/DAC量化的IFFT与FFT的旋转因子映射表存在一个台阶,这是由于基于DIF-2的FFT/IFFT的stage2,stage3和stage4旋转因子存在与文献[11]相似的特性.当stage4旋转因子的量化字长在[8,12]区间时,其量化数值保持不变;当stage3的旋转因子的量化字长在[9,12]区间时,其量化数值保持不变.

尽管本研究仅仅针对定点的64点FFT/IFFT进行数值仿真并获得优化字长映射表,但是利用图5中的各个参数的发展趋势,该映射表可以进一步扩展到采用全并行结构的任意点数的FFT/IFFT.对于系统给定的DAC/ADC,该字长映射表为FFT/IFFT各级信号的最优化字长选择提供了一种简单、有效的方法,这在很大程度上简化了高性能OOFDM收发机和其他基于FFT/IFFT系统的设计.

3 离线验证

为了验证仿真实验结果的可靠性,本研究在实际平台上对实验数据进行了离线验证.测试结构如图6所示,在PC机上使用Matlab软件产生OFDM帧信号,存为文本文件,再通过任意波形发生器(arbitrary waveform generator,AWG)将信号发送出去.OFDM信号经过实际的物理光传输链路后,通过示波器采样信号,再将信号导入PC端的Matlab软件,分析系统IEVM.

图6 系统离线测试结构Fig.6 Verification architecture of offline system

实验仪器的基本参数设置如下:AWG可支持数字6~10bit的输入;系统采用同步方式,即AWG和示波器共用同一个时钟源;系统采用过采样方式,AWG的采样时钟为1GHz,示波器的采样时钟为5GHz.本实验的光路采用分布式反馈(distributed feed back,DFB)激光器进行光强调制,经过25km的光纤链路,再通过光电二极管探测器进行光电转换.

系统分别对浮点型IFFT/FFT运算和基于字长映射表的IFFT/FFT运算进行分析对比.通过离线测试平台,得到系统的性能指标IEVM(重复测试5次,取平均值).通过比较二者之间的差异来验证优化结果的准确性.

图7是浮点型的IFFT/FFT和基于字长映射表的IFFT/FFT所得结果的差值.从图中数据可以看出,二者的误差大约保持在0.5dB范围内,基本满足要求.

图7 浮点型IFFT/FFT和优化后的IFFT/FFT的IEVM数值之间的误差值Fig.7 IEVM differences of ideal IFFT/FFT and optimized IFFT/FFT

4 逻辑资源统计

本研究在Xilinx的Virtex6器件上实现了基于字长映射表的全并行64点FFT模块.为了进行FFT模块的性能分析,本研究采用8bitADC信号输入,根据字长映射表,蝶形每级字长分别选择{131413141516},得到基于字长映射表的64点FFT处理器;同时本研究也使用Spiral工具生成了同样的全并行64点FFT处理器.为了与研究设计性能相匹配,Spiral工具采用16bit定点计算.这两种设计方案的综合对比结果如表3和4所示.

表3给出了基于优化字长映射表的FFT处理器和Spiral工具生成的FFT处理器中乘法器和加减法器的利用情况对比.从对比结果可以看出,本研究的FFT处理器在乘法器数量上和Spiral工具一致,但是由于对数据字长进行了优化,故乘法器的数据位宽相对较小,加法器和减法器也存在同样的现象.因此,本FFT处理器的设计相较于Spiral工具生成的FFT处理器更加节省硬件资源.

表3 FFT处理器中乘法器和加减法器的利用情况Table 3 Usage of multipliers and subtractors for FFT processor

在表4中列出了整个FFT处理器的资源利用结果.从对比结果可以看出,基于字长映射表的FFT处理器相对于Spiral工具性能更优,在Slice LUTs方面可以节约37.2%左右的硬件资源.另外,表4还增加了和文献[9,11-12]中FFT设计之间的对比.由于文献[10]所采用的是Spiral设计[13],故没有单独列在表中.值得一提的是,文献[11-12]是本研究组的前期工作,虽然在资源利用方面没有很大的提升,但是本研究设计采用了更优的搜索算法,缩短了字长优化的搜索时间.

表4 FPGA实现的不同FFT处理器的资源利用结果和对比Table 4 Logic resource usage for different FFT FPGA structures

5 结束语

在OOFDM-PON系统中IFFT/FFT的高资源占用率的情况下,本研究主要通过优化IFFT/FFT模块的字长来降低系统的硬件资源.系统采用IFFT和FFT联合优化的方式,优化了包括蝶形运算的输出字长和旋转因子的字长在内的参数.由于面临系统的高复杂度,软件寻找最优化字长的耗时长,故本研究通过缩小字长搜索范围来降低软件耗时,最终完成软件上的OFDM系统字长优化,同时在离线的实际平台上验证了实验所得数据的准确性.另外,本研究使用Verilog硬件编程语言实现全并行流水线结构的FFT功能模块,与目前使用的Spiral设计相比,本设计的资源在Slice LUTs方面可以节约37.2%左右.

[1]FISCHER J K,ALREESH S,ELSCHNER R,et al.Bandwidth-variable transceivers based on 4D modulation formats for future flexible networks[C]//ECOC.2013:279-281.

[2]JIN X Q,TANG J M.Experimental investigations of wavelength spacing and colorlessness of RSOA-based ONUs in real-time optical OFDMA PONs[J].Journal of Lightwave Technology, 2012,30(16):2603-2609.

[3]INAN B,ADHIKARI S,KARAKAYA O,et al.Real-time 93.8-Gb/s polarization-multiplexed OFDM transmitter with 1024-point IFFT[J].Opt Exp,2011,19(26):B64-B68.

[4]CHEN M,HE J,CHEN L.Real-time optical OFDM long-reach PON system over 100 km SSMF using a sirectly modulated DFB laser[J].Journal of Optical Communications and Networking, 2014,6(1):18-25.

[5]汪敏,虞礼辉,冯俊飞,等.基于异步时钟的高速实时光OFDM收发系统[J].上海大学学报(自然科学版),2013,19(3):250-253.

[6]WOLD E H,DESPAIN A M.Pipelined and parallel-pipeline FFT processors for VLSI implementation[J].IEEE Trans Computers,1984,33(5):414-426.

[7]Spiral software/hardware generation for DSP algorithms[EB/OL].[2014-10-18]http://www. spiral.net/hardware/dftgen.html.

[8]JOHANSSON S,HE S,NILSSON P.Wordlength optimization of a pipelined FFT processor[C]// Proc 42nd Midwest Symp Circuits and Systems.1999:501-503.

[9]TSAI P Y,CHEN C W,HUANG M Y.Automatic IP generation of FFT/IFFT processors with word-length optimization for MIMO-OFDM systems[J].EURASIP Journal on Advances in Signal Processing,2011,DOI:10.1155/2011/136319.

[10]BOUZIANE R,KOUTSOYANNIS R,MILDER P,et al.Optimizing FFT precision in optical OFDM transceivers[J].IEEE Photon Technol Lett,2011,23(20):1550-1552.

[11]TANG J M,ZHANG J J,TUAN W Y,et al.Stage-dependent minimum bit resolution maps for real-time optical OFDM transceivers[C]//OFC.2014.

[12]ZHANG J J,YUAN W Y,WANG K,et al.Stage-dependent minimum bit resolution maps of full-parallel pipelined FFT/IFFT for real-time optical OFDM transceivers[C]//ACP.2014.

[13]MILDER P A,BOUZIANE R,KOUTSOYANNIS R,et al.Design and simulation of 25 Gb/s optical OFDM transceiver ASICs[J].Optics Express,2011(26):B337-B342.

本文彩色版可登陆本刊网站查询:http://www.journal.shu.edu.cn

Design and implementation of FFT/IFFT processors with word-length optimization for OOFDM-PON system

WANG Kai,WU Qi,LI Jiaqi,XUE Ziwei,ZHANG Junjie

(School of Communication and Information Engineering,Shanghai University,Shanghai 200444,China)

High-speed parallel fast Fourier transform/inverse fast Fourier transform(FFT/ IFFT)module has become one of the most significant obstacle to practically developing realtime high-speed optic orthogonal frequency division multiplexing(OOFDM)system based on field programmable gate array(FPGA)platform due to its high complexity.This paper builds a simulation platform for OOFDM transceivers and realizes joint optimization of the IFFT and FFT module to reduce logic resource usage.The algorithm shortens word-length boundaries to reduce the time for searching optimized word-length and builds a mapping table of the optimal word-lengths.Error between simulation results and verification results on an offline platform is within 0.5 dB indicating correctness of the proposed optimization algorithm.In addition,the FFT module based on the mapping table saves about 37.2%resource compared to the Spiral design.

optical orthogonal frequency division multiplexing-passive optical network(OOFDM-PON);fast Fourier transform/inverse fast Fourier transform(FFT/IFFT);wordlength optimization;inverse error vector magnitude(IEVM)

TN 913.7

A

1007-2861(2016)04-0398-10

10.3969/j.issn.1007-2861.2014.05.018

2014-11-26

国家自然科学基金资助项目(61132004,61275073,61420106011);上海市科委重点资助项目(13JC1402600,14511100100,15511105400,15530500600)

张俊杰(1978—),男,高级工程师,博士,研究方向为光接入网等.E-mail:zjj@staff.shu.edu.cn