恒定导通时间电路的设计与实现

2016-09-09杨金亮李天生赣州师范高等专科学校计算机系江西赣州34000电子科技大学微电子与固体电子学院成都60054

杨金亮,李天生(.赣州师范高等专科学校 计算机系,江西 赣州 34000; .电子科技大学 微电子与固体电子学院,成都 60054)

恒定导通时间电路的设计与实现

杨金亮1,李天生2

(1.赣州师范高等专科学校 计算机系,江西 赣州 341000; 2.电子科技大学 微电子与固体电子学院,成都 610054)

电子产品便携式及大功率的应用,要求供电芯片具有快速瞬态响应及高稳定性.采用与输入电压成正比的电流进行充电,并利用输出电压作为参考电压,设计一种恒定导通时间电路,可有效解决恒定电流充电下系统滤波器设计难的问题,同时可提高系统对输入的响应速度.仿真验证表明,恒定导通时间电路有效地提升了电流的精确度及系统的响应速度.

恒定导通时间;电路;降压型变换器;自适应

0 引 言

电子产品的发展要求电源的高性能、高稳定性及快速响应[1],恒定导通时间(Constant On-Time,COT)控制方式比传统的电流或电压模式具有更加优良的瞬态响应及简单的电路[2].现阶段COT电路的研究,基本在从真正意义上的时间恒定到根据具体的输入输出电压产生自适应的导通时间的范围内,在自适应导通时间控制下的电源系统由于其工作频率稳定而较为受设计者青睐.文献[2]所设计的COT电路为最原始发展阶段,采用恒定电流对电容进行充电,产生真正意义上恒定不变的导通时间.由降压型开关电源变换器基本公式可知,恒定不变的导通时间意味着同时随输入和输出变化的开关频率,这对于电源整体的电磁兼容性及后级滤波器的设计带来巨大的困难[1].文献[3]在此基础上进行了改进设计,采用与输入相关的电流对电容进行充电,使开关频率不随输入电压的变化而变化,大大简化了后级系统的设计,但依旧未能达到恒频工作的要求.在相关研究[2-8]的基础上,本文设计一种COT电路,采用与输入电压成正比的电流给电容充电,以输出电压作为基准电压,使得导通时间成为随输入电压成正比与输出电压成反比的自适应COT,保证了电源的恒频工作,降低了电磁兼容性及后级滤波器的设计.

1 恒定导通时间控制模式Buck变换器工作原理

恒定导通时间DC-DC变换器电路结构如图1所示.

其工作原理为:电路运行时,当输出电压Vout的反馈信号VFB低于参考电平VREF时,比较器U2输出为正.若最小关断时间产生器U3输出也为正,则与门U4输出为正,根据RS触发器的特性,S端为正,使之输出Q为正.此正的信号Q通过驱动器U6将上管M1打开,下管M2关闭,使得输出电压Vout升高,反馈信号VFB也升高.同时,此正的信号Q触发恒定导通时间产生器U1开始计时.当输出电压Vout升高至VFB大于参考电平VREF时,比较器U2输出为负,进而RS触发器的置位S端为零,根据RS触发器的特性,S端为零,其输出Q保持原来的状态.当恒定导通时间产生器U1达到预设时间后,其输出端O变为高,进而RS触发器U5的置位R端为高,使得RS触发器的输出变为0.驱动器U6关断上管M1,开启下管M2,输出电压Vout开始下降.同时触发最小时间产生器U3开始计时.U3被触发后,在预设的最小关断时间内,输出一直为0.增加最小时间产生器U 3的目的,是保证自举电容上有足够的电量,进而保证在利用高端自举电路有足够的驱动上端功率管的能力.最小时间产生器U3被触发后,经过最小关断时间后,其输出又变为正.当输出电压Vout下降,使得反馈信号VFB低于参考电平VREF时,重新开始一个新的周期.

图1 恒定导通时间DC-DC变换器电路结构

2 恒定导通时间模块系统及各模块电路的设计与实现

随输入电压变化的充电电流的产生是自适应恒定导通时间的基础.文献[3]采用外接电阻的方法将输入电压转换成电流,文献[7]则采用输入电压分压之后通过运放箝位施加在电阻上产生与输入电压成正比的充电电流.在综合考虑系统的复杂性,以及由于运放的失调、频率特性及共模范围的前提下,本文将输入电流通过三极管的形式与基本偏置电流叠加,得到精确而抗噪性强的充电电流.恒定导通时间模块系统如图2所示.

图2 恒定导通时间模块系统

恒定导通时间模块系统包括充电电流产生模块(Charging Current)、充电模块(Charging)和充电比较器模块(Charging Compare).充电电流产生模块用来产生一个与输入成正比的充电电流.充电模块利用该电流对电容进行充电计时.在充电比较器模块内电容上所充的电压与输出电压进行比较产生一个最后的控制信号输出,并通过系统其他部分控制充电的进行与否.

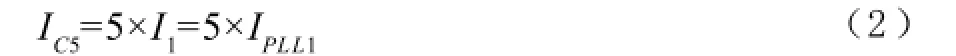

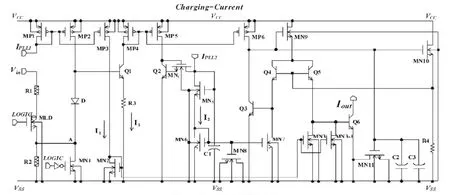

2.1充电电流产生模块电路

充电电流产生模块电路如图3所示.

由图3可知,由左往右,Vin通过电阻阵列R1,LDMOS,电阻阵列R2,在A点处由R1,R2分压产生一个1/20Vin的分压,R1=997.5K,R2=52.5K.A点电压通过二极管D上升一个管压降,再通过Q1下降一个VBE,则有R3上的管压降与A点电压一致,MP4的漏极电流I3为:

其中R3=178.5K.I3通过MP4和MP5镜像至Q3作为其集电极电流IC3.IPLL1通过MP1,MP3和MN2,MN3, MN3-1镜像以比例1:5至Q5的发射极,作为Q5的发射极电流,近似为集电极电流IC5,则IC5为:

在最后一股电流IPLL2的镜像上进行优化,通过分析电路结构可发现,Q4的发射电流、MN7的漏极电流和Q3的积极电流满足条件:

如果I2直接等于IPLL2的话,那镜像至Q4后就会多出一个基极电流,为实现精确镜像,在由IPLL2至I2的过程中必须满足条件:

图3 充电电流产生模块电路

Q2和MN4的加入使得I2和IPLL2满足(4)式的关系之后,则有:

由Q3,Q4,Q5和Q6构成电路的充电电流产生模块的核心部分连接方式为:

根据三极管的电流电压关系得:

Q3,Q4,Q5和Q6充电电流产生模块的所有参数都一致时,则它们的IS一致,化简(7)式得到电流关系为:

其中IC6为充电电流产生模块的输出电流,即Iout为:

代入IPLL1=1uA和IPLL2=3.56e-12XfSW,得到Iout和Vin的数值关系式为:

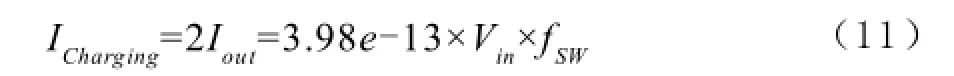

由该模块产生的输出电流在充电模块进行1:2镜像后对充电电容充电,可得到最终的充电电流为:

由电容充电公式IChargingXt=CXVCharging,t即为导通时间,代入C=0.795pF,VCharging=0.5Vout,得到最终导通时间Ton为:

由此可发现,由本文设计的COT模块产生的导通时间理论值几乎相等.

2.2充电模块电路

充电模块电路如图4所示.

图4 充电模块电路

R2的加入保证在充电不使能时电流不会流向充电电容,同时也作比较器延时的补偿.一方面,电路中利用串联的三对PMOS管进行镜像ICharge的目的,是降低由于沟道长度调制效应引起的镜像不精确问题,这是对电路的优化;另一方面,加入右边庞大的电路,防止A点电压过低而导致镜像不精确及电路损坏问题.

2.3充电比较器模块电路

充电比较器模块电路如图5所示.

在该模块中,对VCharging和VREF电压进行比较控制充电使能.当VCharging低于VREF时,VCompare为低电平,充电继续,直至VCharging等于VREF时,A点电平保持不变,进而VCharging将要大于VREF时,VCompare由低到高翻转,控制充电结束.由MN9和MN10引入迟滞电流,使充电比较器的上下翻转点分裂,保证系统的稳定性和比较器的精确度.

图5 充电比较器模块电路

3 仿真验证

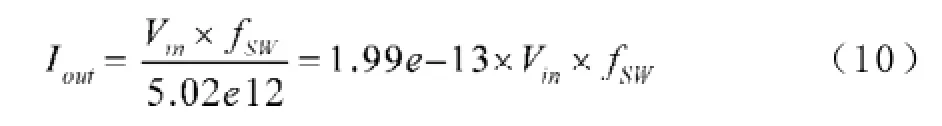

3.1充电电流产生模块电路的仿真验证

当fSW=1MHz,输入电压6~38V之内,充电电流产生模块实际Iout与理论值波形比较仿真曲线如图6所示.

图6 充电电流产生模块实际Iout与理论值波形比较仿真曲线

由图6可知,实际产生的Iout与(8)式理论计算差值在50n以内,计算Iout与Vin近似呈线性关系,即:

与(10)式相比,其误差在3%左右,说明小电压下会存在一定的误差,但总体上在输入电压范围内精确度高,完全满足系统设计要求.

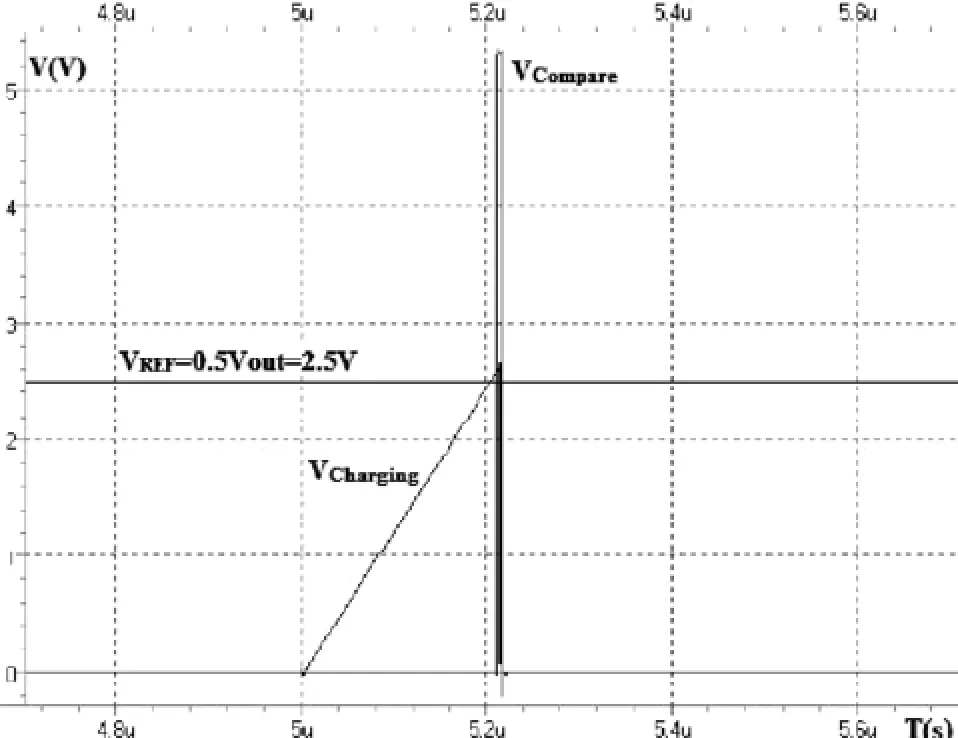

3.2充电比较器模块电路的仿真验证

取Vout=5V(VREF=2.5V),Vin=20V,设置充电控制信号从10us开始充电,充电比较器瞬态响应波形如图7所示.

通过测量该仿真波形得到充电比较器延时Tdelay= 9.77ns可发现,充电比较器响应速度比较快,符合系统设计的要求.

图7 充电比较器瞬态响应波形

3.3恒定导通时间模块的整体仿真验证

对恒定导通时间模块的整体仿真可进一步验证其功能特性.设置Vin=20V,Vout=5V,fSW=1MHz,Control-1为周期T=5us、占空比D=5%的方波,得到恒定导通时间模块的整体仿真曲线,如图8所示.

图8 恒定导通时间模块的整体仿真曲线

通过图8测量得出,充电时间t=248ns,Iout=4.1uA, Tdelay=8.07ns.由(10)式和(12)式理论计算而得的Iout和充电时间t分别为Iout=4.1uA,t=250ns,这与实际测量值几乎一致.

4 结 论

本文设计的恒定导通时间电路具有快速、精准的优点,工作频率与输入电压无关,减小了系统电源EMI滤波器的设计难度,工作频率也可通过外部编程电阻来调整,并通过在充电电流中加入一股与工作频率相关的电流,有效地提高了效率,可很好地应用于高速、高精度Buck系统中.目前,恒定导通时间电路已应用于Ga N器件驱动的大电流需求供电降压芯片中,实际产品正在等待流片测试,应用前景可观.

[1]普利斯曼.开关电源设计[M].3版.王志强,肖文勋,虞龙,等译.北京:电子工业出版社,2010.

[2]BERNARD S.Switching Regulator Architectures Application[R].California:National Semiconductor,2005.

[3]张占松,蔡宣三.开关电源的原理与设计[M].北京:电子工业出版社,199 8.

[4]谢海武.一款恒定导通时间控制模式的降压型变换器的分析与设计[D].成都:电子科技大学微电子与固体电子学院,2 0 1 3.

[5]黄建刚,吴杰,谢海武,等.一种适用于恒定导通时间控制的高性能定时器电路[J].中国集成电路,2012,160(9):40-44.

[6]李演明,来新泉,袁冰,等.自适应开启时间的Buck型DC-DC控制器设计实现[J].半导体学报,2008,29(7):1396-1402.

[7]明鑫,付奎,李天生,等.一种适用于Buck变换器的导通时间产生电路:CN201510204582X[P].2015-10-20.

[8]吴晓辉,吴晓波.一种新型准定频迟滞模式Buck变换器的设计[J].微电子学,2011,41(2):155-159.

[责任编辑:谢树林,乔维德]

Design and Realization of Constant On-Time (COT) Control Mode

YANG Jinliang1, LI Tiansheng2

(1.Computer Department, Ganzhou Teachers College, Ganzhou, 341000, China; 2.College of Micro-electronics and Solid-state Electronics, University of Electronic Science and Technology of china, Chengdu, 610054, China)

Being portable and of great power, electronic devices usually require power supply chips of quick and instant response and of high stability. By means of using the circuit proportionate to input voltage to charge and also use the output voltage as the reference voltage, the Constant On-Time (COT) control mode is designed which can effectively solve the difficult problem of constant circuit filter in charging system and which can also cause the system to give a quicker response to input. Emulational experiments prove that the Constant On-Time (COT) control mode can effectively upgrade circuit accuracy and speed up the response of the system.

Constant On-Time (COT); Circuit; Buck converter; Adaptive

2015年人大复印资料全文转载及索引收录本刊情况摭览

TN402

A

1671-4326(2016)02-0046-05

10.13669/j.cnki.33-1276/z.2016.036

2016-03-14

杨金亮(1976-),男,江西赣州人,赣州师范高等专科学校计算机系讲师,硕士;李天生(1993-),男,江西赣州人,电子科技大学微电子与固体电子学院硕士研究生.