相控阵雷达多通道数字收发电路的设计

2016-01-10

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

当前相控阵雷达的收发分系统多采用全数字阵列的技术体制,收发分系统以数字阵列模块(DAM)为核心,采用搭积木的方式构筑雷达的有源天线阵面,每个阵列单元均包含完整的数字化收发通道[1]。

收发分系统是一个多通道的数字化收发分系统。接收通道完成回波信号的接收、放大、变频、滤波和数字化接收,形成数字基带信号,从而由信号处理分系统实现接收DBF;发射通道完成雷达波形信号的DDS形成、变频、滤波放大,经功放输出送天馈分系统,其DDS波形形成技术能够实现高精度相位控制,可以实现发射DBF[2]。

本文介绍了一种多通道数字收发电路的设计,从系统的工作原理、器件优选、电路设计以及指标测试等不同方面进行了阐述。

1 工作原理

全数字阵列体制的雷达采用搭积木的方式构筑雷达的有源天线阵面,根据应用需求可以选取任意数量的DAM进行系统组合,每个DAM内部通常由8路或16路收发通道组成。

单路收发通道分系统的工作原理如图1所示。接收通道接收来自天馈系统的射频回波信号,经限幅低噪放放大滤波后,再经模拟下变频、滤波后形成中频信号,经ADC数字化采样形成数字基带信号,通过光纤传输给信号处理分系统实现DBF接收;发射通道先经过FPGA控制的DDS形成雷达波形信号,经模拟上变频、滤波放大,再经功率放大送天馈分系统,其数字化的DDS波形形成技术能够实现高精度相位控制。

图1 收发分系统工作原理

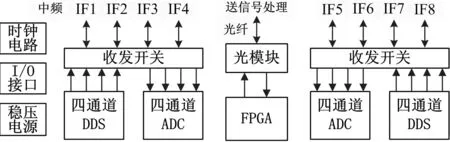

作为DAM内部的核心电路,多通道数字收发电路是数字、模拟电路混合设计,其设计的成功与否直接影响收发系统的技术指标[3]。本文以八通道设计为例,该电路的工作框图如图2所示。

图2 八通道数字收发电路的工作框图

八通道数字收发电路以FPGA为核心,控制其外围的多通道ADC、DDS实现各独立通道的信号发射与接收,通过收发开关的控制实现收发中频端口的共用。DDS的发射波形控制和ADC的接收数据回传均通过光模块的光纤通信设计实现。时钟电路分别为FPGA、ADC、DDS提供基准时钟、采样时钟和工作时钟。电路设计中还包括不同数量的输入、输出I/O接口信号。

2 器件选择

正确选择ADC和DDS器件是设计全数字阵列体制收发系统的重要一环,这将直接影响系统的工作频率动态范围、带宽和总体成本[4]。

Nyquist采样定理指出:当采样频率ωS>2ωM(ωM为输入信号的最高频率)时,采样后的信号能准确地确定原信号。

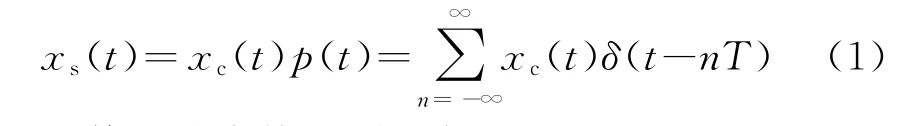

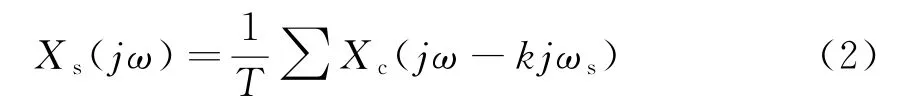

给定一个连续时间信号xc(t),采样后的离散时间信号xs可表示为原信号与一个周期冲激信号p(t)的乘积,如式(1)所示,T为采样周期。

经傅里叶变换,可得到

式中,ωs=2π/T为采样频率。设xc(t)为带限信号,带宽为ωN,当|ω|>ωN时Xc(jω)=0,由式(2)可知xc(t)经采样后的频谱Xs(jω)就是将Xc(jω)在频率轴上搬移到0,±ωs,±2ωs,…,±nωs处。因此,只有当ωS>2ωN时,频谱不会发生混叠[5]。

本系统要求中频输入信号小于100MHz,信号带宽小于10MHz,根据上述分析,ADC的采样时钟不需要选择较高。本电路选择一款四通道14位ADC,最大采样率125MHz,典型满刻度输入信号电平是2.0 VP-P(50Ω阻抗),可通过串行LVDS低电压差分信号输出接口与各种FPGA直接互连。该ADC的参数设置与正常工作均通过FPGA串行配置编程实现控制。

基于DDS的相位控制和波形产生是数字收发单元的关键技术之一,相控阵雷达的工作方式要求雷达信号具有多种波形形式,需要改变信号的频率、脉宽、带宽等参数,这就要求雷达的波形形成非常灵活,而DDS恰能满足这一要求。DDS可以直接对产生的信号波形参数(如频率、相位、幅度)中的一个、二个或三个同时进行直接调制。以调频为例,对于一个DDS系统其输出频率为

式中,k为频率控制字,fclock为DDS输入时钟频率,n为相位累加器的位数[6]。

本系统设计采用一款四通道宽带雷达信号源芯片,该DDS工作时钟频率为400MHz,输出以fout中心频率带宽为10MHz的数字信号;其频率控制码为32 bit,相位控制码为16 bit,理论上移相精度可达到:(360°/216)≈0.005°。

FPGA完成对其外围电路的时序控制、数据采集、波形产生、光纤通信等功能。对FPGA使用资源的评估主要针对软件算法中乘法器的使用情况,主要体现在数字接收通道所需要的数字下变频、数字滤波器、DBF合成等乘法器资源。本设计选用的是Altera公司EP4SGX180系列芯片,该器件包含920个18 bit×18 bit乘法器、44对高速差分接口,最大支持6.5 Gbit/s的光模块传输。

光模块的选型需要根据单个DAM最高数据传输速率的要求,这取决于接收通道数量、传输基带信号(I/Q)的瞬时带宽,以及传输数据的位数。通常情况下对于大型全数字相控阵雷达,最高传输速率为6.5 Gbit/s的光模块可以满足大部分应用。

收发开关的选型应考虑收发隔离度足够高,避免发射通道对接收通道的影响;收发开关的中频(或射频)信号1 d B压缩点功率值(P-1dB)应较大于实际应用的最大功率值,避免因收发开关临近饱和而出现信号高次交调。

3 电路设计

作为数模混合电路,多通道数字收发电路设计需要处理好数字电路对模拟电路的影响,如数字时钟的丰富频谱、开关电源的辐射泄漏对模拟电路的干扰、PCB布局、布线不合理导致数字信号对模拟信号的串扰等。在电路设计中应本着“重模拟、轻数字”的思想开展优化设计,可以有效加以控制。

(1)电源的设计

在原理图设计阶段应合理规划电路所需的电源品种和应用划分,合理的设计可以确保电源上的干扰较小,干净的电源系统对模拟电路的技术指标意义重大。

数字收发板的电源按照数字地和模拟地划分,针对ADC、DDS等模拟电路的电源设计应选用线性稳压电源,而FPGA等数字电路的电源由于电源品种较多、电压低、电流大,可采用效率较高的DC-DC开关电源。应优先考虑模拟系统电源设计,不应使用开关电源参与供电,可独立应用线性电源实现模拟电源设计,避免开关电源的开关频谱泄漏对模拟系统的污染。相同电源电压、不同电源品种的应用,通常以磁珠、电容等实现电源的隔离与滤波。

(2)元器件布局

针对数模混合电路的PCB设计,元器件的合理布局不仅有利于模拟电路与数字电路的划分,还方便电路的内电层分割和信号走线,对于电路的抗干扰能力、实测指标等方面有重要影响。

元器件布局时需要考虑的因素有:电路结构设计要求、贴装器件工艺生产要求、发热器件的散热、良好的接地、易损器材的更换维修等,重点应考虑有利于模拟电路与数字电路的划分。

如图3所示,电路板根据模拟地与数字地划分为两个区域,模拟电路相对集中放置在模拟地区域,数字电路对应数字地区域,两者不能交叉重叠,图中虚线为模拟系统与数字系统的分界线。对于ADC、DDS电路的模拟输入、输出端口,按照器件对应管脚方向放置于模拟区域,而与FPGA相连的数字信号端口对应于数字区域。

图3 元器件布局示意图

用于电源输入或输出的大容量极性电容则应放置在电源模块的周边,而直接给FPGA、ADC或DDS供电的容量较大的极性滤波电容应放置于该元器件的附近,起到供电“蓄水池”的功用。对于数量众多的小容量滤波电容,布局时应尽可能放置在关键元器件的管脚上,这对于ADC模拟电路尤为重要,不合理的布局会严重影响模拟系统的实测指标。

模拟电路应远离FPGA、DC-DC开关电源,模拟时钟电路尽量靠近ADC、DDS放置,避免数字信号干扰模拟电路。在布局时应确保模拟中频(或射频)单端信号的连接路径尽量短,转换为差分信号以后则可以长线匹配传输。

(3)内电层设计

通常情况数字收发板的内电层设计多达十几层,为了确保信号走线对地的直接回流,规划内电层时应确保每个信号层都有对应的地层与之相邻。模拟信号层可以设定为印制板的正、反两面,相邻的两个内电层对应为模拟地层AGND。将干扰较严重的数字信号设定为信号内电层,再由不同的数字地层DGND隔离开并封闭于电路板内层,以防辐射泄漏到模拟系统。

被定义为电源和地的内电层,在进行分割划分时需要按照图3所示布局图中的虚线进行统一整体分割。每个内电层都可严格划分为模拟区域和数字区域,这样可以实现模拟系统和数字系统在印制板每一层的水平方向上、层与层之间的垂直方向上都没有重叠区域,实现两者的完全隔离。

(4)PCB走线设计

印制板布线时需优先关注模拟信号,考虑模拟信号的工作频率、阻抗匹配需求,模拟差分信号走线时应根据印制板材的介电常数、层间距、线径、线距等参数调整为合适的匹配阻抗(通常为50 Ω);应尽量确保模拟信号在模拟区域走线、数字信号在数字区域走线,在走线设计中进一步确保两个区域的隔离。

在内电层走信号线时应确保两点之间的连线不要有过孔将连接信号转入其他信号层,除非是起始和终点需要连接至元器件的管脚焊盘。可以通过优化调整原理图网表连接关系,使得同一层的信号线走相对平行线,如图4所示。

图4 信号内电层走线示意图

由于没有过孔将该电层的信号线窜入其他信号层,同时该信号层的相邻两层均为地层,可以将数字信号在传输过程中产生的干扰有效封闭在该层内部。

对于高速时序信号的走线需要走等长线,可以通过走线折叠弯曲的方式设计实现。为了实现信号线等长的精确控制,不同的高速电路芯片内部管芯到不同管脚的初始长度也不相同,需要将芯片的初始偏移量计算入实际走线总长度。

另外,为了尽量提高多通道数字收发电路的收发隔离度、通道间隔离度等指标,对关键模拟通道支路进行局部大面积覆铜、包地、打密孔等处理,做好对重要模拟信号的隔离和电路安全接地。

图5 实物图

4 指标测试

图6所示为DDS输出的中心频率70MHz、信号带宽10MHz的线性调频信号频谱图,脉内信噪比实测结果高达80 dBc。

图6 DDS输出频谱图

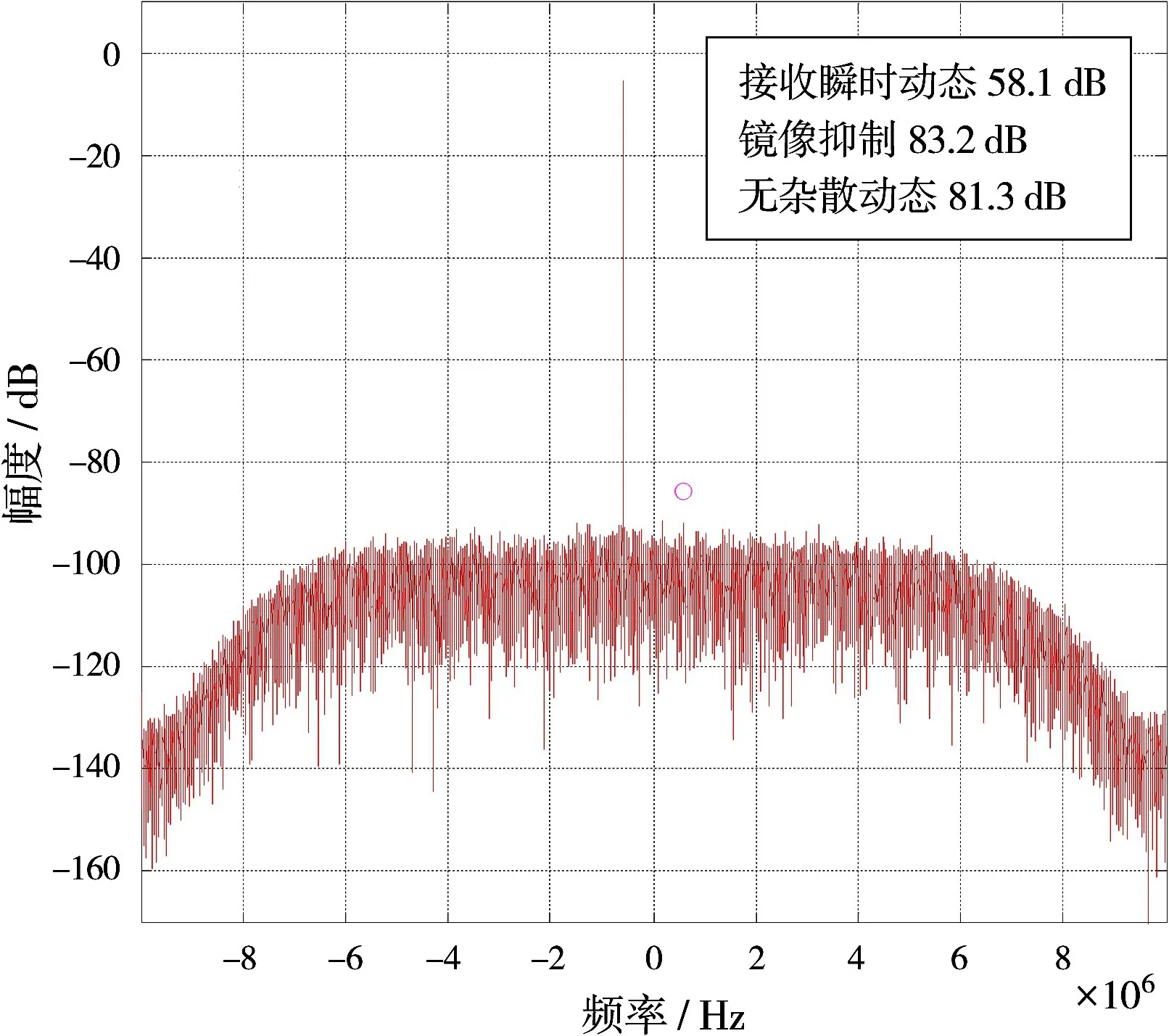

图7所示为该数字收发板在DAM中某接收通道的实测数据。

图7 接收通道数据

经实测,接收瞬时动态大于55 dB,接收镜像抑制和无杂散动态均在70 dBc以上;发射和接收通道的通道间隔离度均达到50 d Bc以上。

5 结束语

综上所述,本文介绍的多通道数字收发电路从系统原理、器件选择、电源和地的规划以及PCB设计等各个环节充分考虑,本着“重模拟、轻数字”的设计理念,实现了相控阵雷达体制下全数字接收和发射技术,已成功应用于某大型相控阵雷达,并为其他不同型号产品所借用。

[1]胡明春,周志鹏,严伟.相控阵雷达收发组件技术[M].北京:国防工业出版社,2010:6-9.

[2]张光义,赵玉洁.相控阵雷达技术[M].北京:电子工业出版社,2006:301-313.

[3]弋稳.雷达接收机技术[M].北京:电子工业出版社,2005:77-82.

[4]姜宇柏,游思晴.软件无线电原理与工程应用[M].北京:机械工业出版社,2007:13-19.

[5]张奕,谭剑美.DAM中多通道数字收发的设计与实现[J].雷达科学与技术,2012,10(3):320-323.

[6]张奕,余海龙,谭剑美.四通道高速数据采集系统设计[J].现代电子技术,2012,35(9):10-12.