动态自适应低密度奇偶校验码译码器的FPGA实现

2015-10-31兰亚柱杨海钢

兰亚柱 杨海钢 林 郁

动态自适应低密度奇偶校验码译码器的FPGA实现

兰亚柱①②杨海钢*①林 郁①

①(中国科学院电子学研究所可编程芯片与系统研究室 北京 100190)②(中国科学院大学 北京 100049)

在复杂深空通信环境中,自适应能力的强弱对低密度奇偶校验(LDPC)码译码器能否保持长期稳定工作具有重要影响。该文通过对DVB-S2标准LDPC码译码器各功能模块的IP化设计,将动态自适应理论参数化映射到各功能模块中,实现动态自适应LDPC码译码器的设计。基于Stratix IV系列FPGA的验证结果表明,动态自适应LDPC译码器可以满足不同码率码长及不同性能需求下的译码。同时,单译码通道可以保证译码数据信息吞吐率达到40.9~71.7 Mbps。

LDPC码译码器;动态自适应;DVB-S2标准;FPGA

1 引言

DVB-S2是欧洲数字视频广播联盟在2004年提出的第2代卫星数字视频广播通信标准。DVB-S2标准采用低密度奇偶校验(Low Density Parity Check, LDPC)码作为信道编码的解决方案。

20世纪60年代初,LDPC码首次被提出[1]。在后续数十年中,除了Tanner图理论外,LDPC码很少有进一步的实质性研究成果。90年中后期,文献[2]通过一系列创新性研究,促使LDPC码迅速成为信道编码领域关注和研究的热点。

在国内,文献[3]对DVB-S2标准相同码长、不同码率的LDPC码纠错性能进行了对比分析,并未涉及硬件逻辑实现及验证。文献[4]针对DVB-S2标准LDPC码的改进最小和译码算法,提出一种FPGA实现方案,但其在码长及码率灵活度方面不足。

在国外,文献[5]基于DVB-S2标准LDPC码提出一种可以支持所有码率的LDPC译码器实现方案,但是该方案需要消耗的硬件逻辑存储资源过大。为了有效降低对硬件逻辑存储资源的消耗,文献[6]通过有效降低LDPC码译码器的并行度的方法,但该方法的代价是降低了译码器的整体译码数据吞吐率。

随着我国在载人航天和探月工程等重大专项的深入发展,LDPC码在未来深空通信领域将具有很高的应用价值。目前,国内学者对LDPC码的研究结论往往是对某一算法的验证或是特定结构LDPC码的实现,难以普遍应用。面向DVB-S2标准LDPC码在我国深空通信领域的应用,本文以FPGA为硬件逻辑平台,完成动态自适应LDPC码译码器的IP化设计实现及验证。

2 核心算法及理论基础

2.1 层次化修正最小和(Min-Sum, MS)算法

鉴于此,本文选取层次化修正MS算法作为动态自适应LDPC码译码器硬件逻辑实现的基本迭代译码算法模型。

2.2 IP化设计思想

本文对LDPC码译码器采用IP化设计思想,即利用IP核可重构配置性强的特点,对LDPC码译码器进行硬件逻辑实现。LDPC码译码器IP化设计思想主要包括(1)采用自上而下的方法对LDPC码译码器系统进行功能模块划分;(2)利用自下而上的方法对各个功能模块进行IP化设计实现;(3)对LDPC码译码器参数化功能进行设计实现;(4)通过系统性功能验证,完成LDPC码译码器的设计。

LDPC码译码器的整体硬件逻辑设计结构如图1所示。基于IP化设计思想,将LDPC码译码器划分为4个相互独立功能模块以及参数配置模块、控制模块和信息输出模块。

图1 LDPC码译码器IP化模块划分结构

量化模块负责将信道端接收到的浮点数据信息进行硬件量化处理及存储。信息模块主要包括校验节点信息更新、变量节点信息更新。校验节点更新主要由数值比特位运算模块和符号比特位运算模块构成。变量节点更新由比特位加法器构成。存储模块负责以360为基本因子,对校验矩阵的地址进行存储和循环调度。迭代模块负责译码器的迭代数据信息检测及反馈。参数配置模块负责对译码器的各种参数进行配置。控制模块负责对译码器的各个功能独立的模块进行调度控制。信息输出模块将迭代译码终止迭代后数据信息及有效标志位输出。

2.3 动态自适应理论

本文采用的动态自适应理论包括动态主动自适应和动态被动自适应两种。主动自适应主要为了保证译码器功能自适应,包括码率码长等。被动自适应主要为了保证译码器性能的自适应,包括译码精度、数据吞吐率等。

本文将动态自适应理论以IP化的设计思想融入LDPC码译码器的设计中。按照图1的模块划分,对功能上相互独立的量化模块、信息模块、存储模块和迭代模块等4个模块进行动态自适应IP化设计。针对各个功能化模块,IP化设计思想均会对其进行动态自适应理论方面的参数配置及标准映射。LDPC码译码器IP化设计参数配置如图2所示。

图2 LDPC码译码器IP化设计参数配置及映射标准

在对LDPC码译码器进行IP化模块划分时,会对数据接口的位宽及控制接口的有效性进行参数化处理。在此基础上,LDPC码译码器IP化设计参数配置便可以通过数据接口位宽及控制接口有效性的不同设置,保证各功能模块之间的功能性一致。总之,通过IP化设计,动态自适应功能会通过各功能模块之间及内部的合理配置而整体有效地体现出来。

3 动态自适应LDPC码译码器的设计

3.1动态自适应量化模块

层次化修正MS译码算法在硬件逻辑实现中,随着迭代次数的递增,变量节点信息会出现定点量化范围的边界饱和,严重影响译码性能。为了在量化边界饱和与逻辑资源消耗间取得有效平衡,动态自适应量化模块采用被动自适应方式处理初始化阶段的数据量化,采用主动自适应方式处理迭代译码阶段的数据量化。

动态自适应量化模块的配置如图3所示。初始化量化比特位数设置为8,其中,1 bit数据符号位1为正0为负,7 bit的数据大小值。保留位会给初始化量化提供两种不同的配置选择,(1)采用低位表示数据符号位的策略;(2)采用高位表示数据符号位的策略。

图3 动态自适应量化模块配置

3.2动态自适应信息模块

层次化修正MS译码算法中,迭代译码需要存储迭代信息的最小值和次最小值。

动态自适应信息模块的配置1如图4所示。基于该配置信息,可以解压出校验节点传递给所有变量节点的信息。动态自适应信息模块选取校验矩阵的行重为30,与之相对应共有30 bit的符号位,对应传递给30个变量节点信息的符号。同时,选取最小值和次小值绝对值均采用5 bit整数和2 bit小数量化形式。

图4 动态自适应信息模块配置1

在迭代译码过程中,对码长64800或16200的数据信息进行存储,需要消耗64800(16200)×bit(为量化位宽)的硬件存储资源。如果采用整体例化存储资源的方式,译码器的系统时钟最高可达151 MHz。为了提高译码器系统时钟,动态自适应信息模块采用被动自适应方式,对数据信息进行分布式存储。

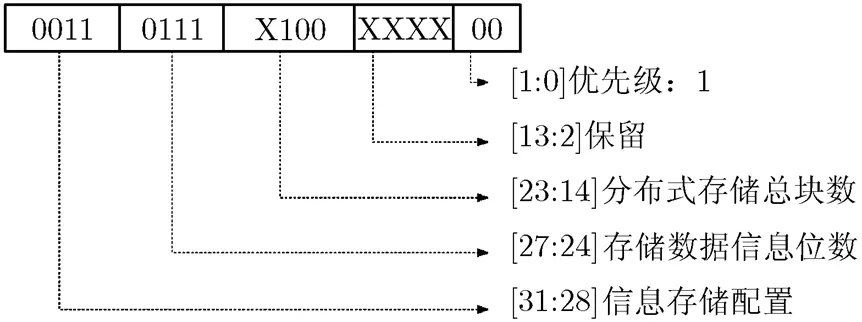

动态自适应信息模块的配置3如图5所示。基于该配置信息,动态自适应信息模块采用分布式例化存储资源的方式时,即将64800深度的RAM分配为4块深度为16320的RAM,而通过整体的RAM数据信息读写调度模块,对4块RAM进行读写管理,可以使译码器的系统时钟最高可达182.5 MHz。

图5 动态自适应信息模块配置2

3.3动态自适应存储模块

在LDPC码译码器中,动态自适应存储模块采用被动自适应方式处理采用码率及码长范围的选择,采用主动自适应方式处理实际译码过程中的码率及码长的确定。

动态自适应存储模块的配置如图6所示。动态自适应存储模块以码长为基准,将DVB-S2标准11种码率的校验节点地址在ROM中采用指针式分级存储。在综合编译时,针对动态自适应存储模块配置参数进行不同的综合适配,生成针对用户设定不同码率的可执行文件。

图6 动态自适应存储模块配置

3.4动态自适应迭代模块

在迭代译码过程中,如何有效地终止译码,是提高译码效率的关键。动态自适应迭代模块中,采用被动自适应方式接收最大迭代译码次数,采用主动自适应方式检测译码数据并控制终止译码。

动态自适应迭代模块的配置如图7所示。迭代译码次数表示最大迭代译码次数。迭代终止使能标志位表示动态自适应迭代模块开启主动自适应迭代功能。动态自适应迭代模块可以保证在不进行重复编译的条件下,动态检测译码数据是否正确。当译码数据正确时,动态自适应迭代模块会主动终止迭代译码。

图7 动态自适应迭代模块配置

4 动态自适应LDPC码译码器的验证与分析

4.1 译码器的实现分析

在Quartus II环境下,本文选用Stratix IV系列EP4SGX230KF40C4 FPGA作为硬件逻辑实现平台,对译码器的逻辑资源耗用进行分析。其中,(1)通过动态配置文件,将译码器的功能自适应设置为64800码长、1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9, 9/10等11种码率。(2)译码器设置最大迭代次数为10次。Quartus II综合编译结果显示,译码器的硬件资源消耗为:ALM逻辑单元(5270)、寄存器(2300)、存储块(12941950 bit)。通过Time Quest分析,译码器的系统时钟可以达到179.95~ 191.13 MHz。

4.2译码器的功能自适应验证

本文采用ModelSim 10.1b环境,配合FPGA及Quartus II,对动态自适应LDPC码译码器进行功能自适应验证。其中,(1)通过动态配置文件,将译码器的功能自适应设置为64800和16200两种码长、1/5, 1/2, 7/9 3种码率。(2)利用Quartus II和Stratix IV系列的EP4SGX230KF40C4 FPGA构建硬件验证平台。(3)在采用AWGN信道,利用Matlab R2012b构造码长码率不断变化的随机信道数据信息。(4)在FPGA硬件验证平台上,对LDPC译码器的功能自适应进行验证。

通过SignalTap II对译码器的输出数据信息与ModelSim 10.1b的功能仿真数据信息进行比对,进而可以确定译码器的功能正确性。同时,为了突出译码器的功能验证的针对性和对比性,本文选用码长为16200,码率为1/5的LDPC码,将动态自适应LDPC译码器的译码性能与在Matlab R2012b环境下浮点型迭代译码的译码性能进行对比分析。针对500帧译码数据信息,最大迭代次数为15次,译码性能的误码率及误帧率如图8所示。

图8 蒙特卡洛实验结果

由数据可知,动态自适应LDPC码译码器的译码性能与Mtalab R2012b的浮点型迭代译码的译码性能已经相当接近,且随着动态自适应LDPC码译码器的硬件量化位宽的增大接近效果越好。以信噪比为1.5 dB时为例,硬件量化位宽为8 bit时,二者间约有半个数量级的差距。如果增加硬件量化位宽为12 bit时,动态自适应LDPC码译码器可以取得和浮点型迭代译码相当接近的出色译码性能。

4.3译码器的性能自适应分析

动态自适应LDPC码译码器的性能自适应主要包括译码精度、译码数据吞吐率的自适应能力。本文经过选用Stratix IV系列EP4SGX230KF40C4作为硬件逻辑实现平台,利用Quartus II综合编译,借助TimeQuest得出硬件电路的系统时钟,进而对译码器的数据吞吐率进行评估。译码器的数据吞吐率计算如式(1)所示。

当码长为64800时,译码器的数据吞吐率评估结果如表1所示。其中,将每一种码率组合分别进行10次综合编译而得出系统时钟的平均值作为式(1)中所对应的系统时钟。由评估可知,(1)系统时钟随着译码器所包含的码率变多而有所下降,但影响不大约为10 MHz左右;(2)译码器的数据吞吐率最小为40.90 Mbps,最大为63.71 Mbps;(3)随着动态译码迭代次数的增大,译码器的数据吞吐率会有所降低。按照相同评估原理,当码长为16200时,译码器的数据吞吐率最小为45.46 Mbps,最大为71.67 Mbps。

表1译码器的数据吞吐率(iter=1)

需要指出的是,以上译码器的数据吞吐率均是在迭代次数为1的情况下得出。按照式(1),随着迭代次数增加,译码器的数据吞吐率会逐渐降低。因此,如果需要获得更高的数据吞吐率,可以选择增加动态自适应译码器的数目。虽然该方法可以通过简单的配置实现,但是其在提高数据吞吐率方面受到硬件逻辑资源的限制。在此情况下,式(1)可以进一步修正为:

4.4译码器动态自适应性能比较

为了对动态自适应LDPC码译码器与现有的其他设计方案进行对比,本文选用从2008年到2014年间,文献[11-15]分别提出的LDPC码译码器的硬件逻辑实现方案为比较对象。针对各种方案实现的LDPC码译码器自适应性能,进行比较的内容包括:可参数化配置、自适应范围、自适应译码精度、自适应译码效率等方面。译码器自适应性能比较数据如表2所示。

表2译码器自适应性能比较

由数据可知,本文提出的动态自适应LDPC码译码器,具有比较明显的动态自适应功能优势。文献[11-13,15]均是将码率码长自适应功能的实现建立在特定LDPC码校验矩阵的基础上。其中,文献[13,15]更是利用基矩阵构建校验矩阵的方案实现多种码率码长的自适应。基于DVB-S2标准LDPC码译码器对应的校验矩阵必须遵守DVB-S2标准,不宜被修正优化。文献[14]与本文都未对标准校验矩阵进行改变。不同的是,文献[14]仅对码率码长自适应进行可参数化配置设计,而没有涉及更为广泛的自适应范围。除此之外,文献[16]提出了可重构LDPC码译码器的ASIC实现。其中,可重构是通过对校验矩阵的特征化存储来实现,但是自适应能力未被充分考虑。

动态自适应LDPC码译码器在整体自适应处理流程上比非自适应处理具有明显优势。具有动态自适应功能的LDPC码译码器可以在译码环境因素发生改变时,自适应调整内部各模块的功能,在不需要重新选择LDPC码译码器及FPGA综合、编译及配置可执行文件的情况下,顺利完成对数据信息的迭代译码。非自适应处理在译码环境因素改变时,则需要重新进行LDPC码译码器的选择及FPGA综合、编译及配置可执行文件等处理。在耗用大量时间的同时,更会对在深空通信中的LDPC码译码带来不稳定因素。

5 结束语

本文基于DVB-S2标准设计实现的动态自适应LDPC码译码器可以适应不同码长、不同码率、不同迭代次数、不同译码精度、不同译码性能等译码环境下的动态自适应迭代译码。基于Stratix IV系列FPGA的验证数据表明:与现有实现方法相比,动态自适应LDPC码译码器在自适应方式及范围上都有明显的优势,从而可以有效保证DVB-S2标准LDPC码在深空通信中的实际应用,促进我国在深空通信领域水平的提高。

参考文献

[1] Gallager R G. Low density parity check codes[J]., 1962, 8(1): 21-28.

[2] Mackay D J C and Neal R M. Near Shannon limit performance of low-density parity check codes[J]., 1996, 32(18): 1645-1646.

[3] 陈豪威, 王秀敏. 基于DVB-S2标准的LDPC码编译码器设计研究[J].电视技术, 2012, 36(3): 1-3.

Chen Hao-wei and Wang Xiu-min. Study on design of LDPC encoder and decoder for DVB-S2[J]., 2012, 36(3): 1-3.

[4] 江桂芳, 彭克荣. 基于FPGA的高速并行DVB-S2标准LDPC译码[J]. 空间电子技术, 2013, 10(1): 58-61, 95.

Jiang Gui-fang and Peng Ke-rong. A FPGA-dased high-speed paraller LDPC decoder for DVB-S2 system[J]., 2013, 10(1): 58-61, 95.

[5] Kienle F, Brack T, and Wehn N. A synthesizable IP core for DVB-S2 LDPC code decoding[C]. Proceedings of the Design, Automation and Test in Europe conference, Munich Germany, 2005: 100-105.

[6] Gomes M, Falcão G, Silva V,.. Flexible parallel architecture for DVB-S2 LDPC decoders[C]. Proceedings of the Global Telecommunications Conference, Washington, DC, USA, 2007: 3265-3269.

[7] 张高远, 周亮, 苏伟伟, 等. 基于平均幅度的 LDPC 码加权比特翻转译码算法[J]. 电子与信息学报, 2013, 35(11): 2572-2578.

Zhang Gao-yuan, Zhou Liang, Su Wei-wei,.. Average magnitude based weighted bit-flipping decoding algorithm for LDPC codes[J].&, 2013, 35(11): 2572-2578.

[8] 孙锦华, 刘鹏, 吴小钧. 联合旋转平均周期图和解调软信息的载波同步方法[J]. 电子与信息学报, 2013, 35(9): 2200-2205.

Sun Jin-hua, Liu Peng, and Wu Xiao-jun. A joint rotational periodogram averaging and demodulation soft information carrier synchronization algorithm[J].&, 2013, 35(9): 2200-2205.

[9] 钟州, 金梁, 黄开枝, 等. 基于二维信息修正减小LDPC码安全间隙的译码算法[J]. 电子与信息学报, 2013, 35(8): 1946-1951.

Zhong Zhou, Jin Liang, Huang Kai-zhi,.. Decoding algorithm for reducing security gap of LDPC codes based on two-dimensional information correction[J].&, 2013, 35(8): 1946-1951.

[10] Roberts M K and Jayabalan R. A modified optimally quantized offset min-sum decoding algorithm for low- complexity LDPC decoder[J]., 2014, 80(2): 1-10.

[11] 倪俊枫, 甘小莺, 张海滨, 等. 改进的分层修正最小和LDPC译码算法及译码器设计[J]. 系统工程与电子技术, 2008, 30(12): 2531-2535.

Ni Jun-feng, Gan Xiao-ying, Zhang Hai-bin,.. Improved layered modified minimal sun LDPC decoding algorithm and LDPC decoder design[J]., 2008, 30(12): 2531-2535.

[12] 管武, 乔华, 董明科, 等. 多码率LDPC码高速译码器的设计与实现[J]. 电路与系统学报, 2009, 14(2): 1-6.

Guan Wu, Qiao Hua, Dong Ming-ke,.. Design and implementation of a high-throughput decoder for multi-rate LDPC code[J]., 2009, 14(2): 1-6.

[13] 赵旦峰, 赵辉, 许元志, 等. 可配置LDPC码译码器的FPGA设计与实现[J]. 黑龙江大学自然科学学报, 2012, 29(2): 259-264.

Zhao Dan-feng, Zhao Hui, Xu Yuan-zhi,.. Design and implementation of configurable LDPC decoder based on FPGA[J]., 2012, 29(2): 259-264.

[14] 唐凯林, 杜慧敏, 段高攀, 等. 多码率、多码长LDPC译码器的设计与实现[J]. 电子技术应用, 2013, 39(12): 58-60.

Tang Kai-lin, Du Hui-min, Duan Gao-pan,.. Design and implementation of multi-rate and multi-length LDPC decoder[J]., 2013, 39(12): 58-60.

[15] 林梅英, 许肖梅, 陈友淦, 等. 码率兼容QC-LDPC码在水声通信中的应用[J]. 声学技术, 2014, 15(5): 460-463.

Lin Mei-ying, Xu Xiao-mei, Chen You-gan,.. Applications of rate-compatible QC-LDPC codes in underwater acoustic communication[J]., 2014, 15(5): 460-463.

[16] 栾志斌, 裴玉奎, 葛宁, 等. 低存储高速可重构LDPC码译码器设计及ASIC实现[J]. 电子与信息学报, 2014, 36(10): 2287-2292.

Luan Zhi-bin, Pei Yu-kui, Ge Ning,.. Design and ASIC implementation of low memory high throughput reconfigurable LDPC decoder[J].&, 2014, 36(10): 2287-2292.

Design of Dynamic Adaptive LDPC Decoder Based on FPGA

Lan Ya-zhu①②Yang Hai-gang①Lin Yu①

①(,,,100190,)②(,100049,)

Faced with the complex environment of deep space communication, the adaptive capacity can have an impact on the ability of the Low Density Parity Check (LDPC) code decoder to maintain long-term stability. This paper proposes a design method of dynamic adaptive LDPC code decoder. Through the IP-based design of each function module, the design method of dynamic adaptive can be mapped to each function module in DVB-S2 LDPC code decoder. The verification results based on the Stratix IV FPGA show the dynamic adaptive LDPC code decoder not only can decode under the different code length and code rate, but also can decode under the different decoding performance. Meanwhile, the single-channel decoder can ensure the information throughput to reach to 40.9~71.7 Mbps.

Low Density Parity Check (LDPC) code decoder; Dynamic adaptive; DVB-S2 standard; FPGA

TN911.22; TN402

A

1009-5896(2015)08-1937-07

10.11999/JEIT141609

杨海钢 yanghg@mail.ie.ac.cn

2014-12-15收到,2015-02-15改回,2015-05-11网络优先出版

国家自然科学基金(61404140, 61271149, 61106033)资助课题

兰亚柱: 男,1983年生,博士生,研究方向为FPGA软核设计、网络及信道编码技术等.

杨海钢: 男,1960年生,博士,研究员,研究方向为高速可编程逻辑芯片设计技术、数模混合信号SOC设计技术等.

林 郁: 男,1983年生,博士,助理研究员,研究方向为FPGA结构、FPGA CAD、高层综合和FPGA高性能计算等.