移动通信实验系统软硬件设计与实现

2015-04-17张晓宇

徐 军, 张晓宇

(华北科技学院 电信工程学院, 河北 燕郊 065201)

移动通信实验系统软硬件设计与实现

徐 军, 张晓宇

(华北科技学院 电信工程学院, 河北 燕郊 065201)

目前高校通信类专业所用实验设备主要完成调制、交织、信道编码和系统信令实验,较难配合3GPP标准来完成教学、科研、课程设计及毕业设计等实践教学环节的任务。充分研究3GPP标准文档后,在自主开发的ARM和DSP单板上完成了3G/4G系统UE侧和eNodeB/NodeB侧物理层、MAC、RLC、PDCP、RRC、NAS的开发。文中对单板结构进行了研究,对UE侧和eNodeB侧的操作系统进行了移植。对RRC、RLC、物理层实现的部分过程进行了描述。通过同样硬件结构的两块单板,可以组成一个TD-LTE移动通信系统,较好地配合了教学和科研工作,对3GPP标准的演进过程的跟踪教学与研究也有一定作用。

第三代合作伙伴项目; 数字信号处理器; 信道编解码; 协议栈

0 引 言

大多数嵌入式设备都使用ARM[1-13]芯片作为微处理器,经过几十年的发展,ARM技术已经发展得很成熟。但是由于多媒体以及大数据的发展,对数据的处理提出了很高要求,不仅要求系统具有很高的正确率,还要求有很高的处理速率。普通的ARM芯片不能达到要求,大大的限制了嵌入式设备的发展。而DSP[14-15]芯片却能很好地解决这些问题。DSP芯片是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。因此本文设计了ARM和DSP一体的嵌入式开发平台。具有ARM和DSP各自的优点,既能起到控制芯片的功能,又能提高处理数据的能力。在此基础上,搭建了Linux系统和VxWorks系统,植入操作系统使得操作更加方便人性化,同时使得软件平台的自由度大。同时,本文在自主开发的ARM和DSP单板上完成了3G和4G系统协议栈开发。实现了MAC[1,7]、RLC[4,6]、PDCP[8]、RRC[9]、NAS[10]、NBAP[5]、RANAP[2]、S1AP[3]等协议的开发。

1 硬件系统

1.1 硬件结构

系统主要芯片为ARM芯片,DSP芯片,FPGA芯片,并含有一个RS232接口、网络接口及一个FLASH和两块SDRAM。在DSP子系统中包含一个FLASH、一块SDRAM,FLASH用于存放DSP系统的程序;通过JTAG接口可以对DSP进行调试、下载DSP程序到FLASH中。DSP系统通过HPI方式与ARM进行数据交互。硬件架构是基于ARM和DSP的,两者既是单独存在也是彼此联系着的,它们之间可以实现资源共享、数据传输、控制功能(双向控制)等等,这些无疑是采用这种架构设计的最突出的优势。同时,它们也是彼此分开的,对于ARM来说,起到主要的控制作用,可以看出,ARM可以控制很多其他扩展的模块,比如USB模块、串口模块、网络接口模块、SDRAM模块、FLASH模块;对于DSP来说,其起到辅助的作用,同时,DSP芯片也是一部分模块的控制单元,连接了其他的模块,比如,SDRAM模块和FLASH模块。而在ARM和DSP之间,建立了用于连接两者数据、资源的32位HPI协议程序,方便实现不同架构的资源共享。本硬件平台可以满足开发人员的多种应用要求,比如,串口模块和USB模块可以利用在数据传输相关的应用开发中,网络接口模块可以利用在网络协议相关的应用开发中,SDRAM模块和FLASH模块可以使用在数据处理相关的应用开发中。这些扩展模块可以满足大部分的开发应用,同时,DSP的使用,又使得本软件平台的应用厚度增强。32位HPI的使用,使得ARM和DSP紧密结合在一起,达到资源共享,资源合理分配,智能调度的效果。

ARM芯片可以使用LINUX操作系统和VxWorks操作系统,3G,4G移动通信系统协议栈L2,L3,NAS层在ARM上实现。DSP和FPGA用于实现物理层算法。

1.2 硬件设计

硬件设计中包括几个主要模块的设计,包括ARM中心模块的设计、DSP中心模块的设计和系统电源模块。选择三星公司设计的S3C2410芯片完成多种外接模块的设计。由于管脚较多,需要对管脚进行分组,每一组为一层,进行多层板的设计,本次设计的ARM中心模块的多层设计,分别以A、B、C、D来区分。

在ARM的A层原理图中,主要利用通用I/O口,定义了一些地址接口和数据接口,形成了地址总线和数据总线,用于操作系统的基本操作;另外,同时也定义了一些系统时钟模块接入I/O口或者部分功能模块的工作时钟接入I/O口;定义了ARM芯片的工作模式选择的I/O口,如OM0、OM1、OM2、OM3;定义了一些功能模块的输入输出I/O口,如网络接口模块、SDRAM模块、FLASH模块;最后,本层的原理图中还开辟了其他通用I/O口作为其他拓展功能的备用接口,比如接入以后需要拓展的FPGA模块等。在ARM的B层原理图中,利用通用I/O口定义了一些外围功能模块,比如,VD总线就是定义于外接LCD模块,此外,B层也定义了串口通信模块,用于数据传输,可以通过串口与外接设备进行数据通信或者烧写程序到ARM芯片中,也可以打印串口消息;同时,系统定义了DN0、DN1、DP0、DP1接口,用于对两个USB接口的接口定义,用于与一些移动设备的数据通信;还有一些接口是定义了ARM_Jtag接口,连接一些外围仿真器,此设计使用的是20针的Jtag口,用于烧写、调试程序,使开发更方便;最后,在该层上还有一些系统已经定义的I/O口,用于系统的特殊功能。在ARM的C层原理图中,主要是一些系统的I/O口,可以定义为电源接地层,该层主要是把一些需要提供电源和接地的I/O口组合使用,从图看出,ARM芯片一共需要两种电源,分别是1.8 V和3.3 V,另外,该层还有一些系统I/O口,比如重置接口RESET,指示系统工作状态的LED 0-3等,还有一些自定义接口,如ARM_EINT0、ARM_EINT1、ARM_EINT2、ARM_EINT3、ARM_EINT7等,用于连接其他设备。

DSP选择TI公司的TMS320C6416,将其进行分组设计,每一组为一层,共分为A、B、C、D、E、F、G、H八层。由于A层涉及到电平选择的作用,因此加了一个功能芯片SN74CBTD3384DW,用于实现10位FET总线开关和电平转换的作用,以达到DSP芯片的工作要求。在该层中,定义了DSPCLKIN——时钟电路的输入I/O接口,DSP_nRESET——DSP芯片重置I/O接口,DSPEXT_INT4、DSPEXT_INT5——DSP外部时钟电路输入I/O接口,在SN74CBTD3384DW的输入端口包括DSP_TMS、DSP_TDO、DSP_TDI、DSP_TCK、DSP_nTRST、DSP_EMU0、DSP_EMU1,作为DSP芯片烧写、调试程序的功能。B层为DSP芯片的中心层,定义了一些地址总线,并命名为TAEA,共有20位地址总线,同时定义了数据总线,命名为TAED,共有32位数据总线,通过之间的连接关系说明地址与数据之间的处理关系。此外,还有一些控制端口,如TABE 0-7——8位控制总线,用于控制数据处理方案,最后还有其他的控制端,用于对数据的控制。C层原理图中,依然设置了地址总线和数据总线,分别命名为TBEA、TBED,宽度依次为20位、16位,其余I/O口依次命名为BECLKIN、BEKO1、BEKO2、TBARE、TBAOE、TBAWE、BHOLD、BBUSREQ、BHOLDA,都是对本层数据和地址的控制端口,达到控制作用,实现一定的处理方案,在本层中,还有一些端口连接了电源,主要是因为这些端口实现上电才能完成特定功能。在D层原理图中,主要体现了DSP芯片同ARM芯片之间的数据交换功能,如定义了DATA,宽度为32位,连接ARM芯片相对应的位置,实现ARM与DSP之间的数据传输、共享等功能。此外,D层有一个特殊的定义,HPI_MODEBIT5——用于ARM与DSP之间的HPI测试,此HPI测试是我们自行编写的一个测试硬件通信能力的程序。DSPnHINT、DSPHCNITL0、DSPHCNITL1、DSPHHWIL、DSPnHDS2、 DSPnHR/nW、DSPnHCS、DSPnHDS1等管脚则是关于芯片功能的设置管脚,可以控制芯片处于特定模式的工作状态下。由于DSP中心模块原理图的E层、F层没有实现任何功能,此处都设置为悬空,作为扩展用。DSP的G层、H层都没有特定的功能,只是提供电源和接地功能,也可以称之为接地层和电源层。

由于设计中使用到很多不同种类的芯片,而这些不同的芯片都工作在不同的电压,这就造成了存在很多的工作电压,而设置不同的电压对模块来说是不现实的,所以模块内部应该有电平转换功能,该设计中,有5、3.3、1.8 V,该电源模块必须有这些电压的输出。

2 软件结构

2.1 操作系统

基于ARM和DSP的硬件架构,可以让我们设计更加高效、丰富、全面的软件系统,操作系统采用Linux+VxWorks的软件架构,其中,Linux系统是主要的嵌入式操作,负责所有的系统文件的管理和程序的运行,主要负责一般性业务,而对于一些对可靠性、精度、运行速度或者效率要求较高的情形时,则选择VxWorks系统,在系统开机运行时,我们设置了选择系统的选项,用户可根据事务自行选择系统,这样在方便用户的同时,也增强了设备的多样性。

下面从总体上说明两种系统操作系统搭建移植的步骤。

(1) Linux系统。安装虚拟机嵌入式系统、搭建GNU编译链、编译Boot镜像、编译Linux内核镜像、烧写镜像文件、移植系统。

(2) VxWorks系统。安装Tornado 2.2、安装DFB2410 VxWorks BSP、编译VxWorks Boot ROM镜像、编译VxWorks内核镜像、烧写镜像文件、移植系统。

2.2 应用系统

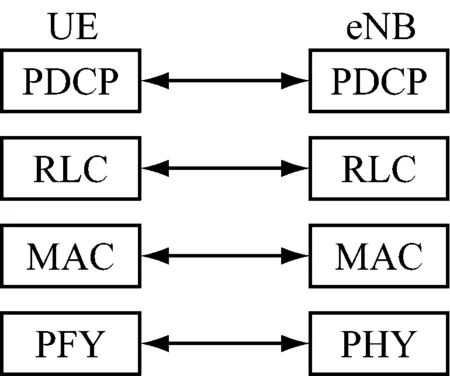

在本系统中,利用两块单板完成TD-LTE系统开发。单板间的通信通过网口进行通信。分别完成UE和eNodeB的功能。通过串口与PC机的监控系统通信。E-UTRAN的无线协议接口包含用户面协议接口和控制面协议接口。用户面协议栈如图1所示,包含PDCP(分组数据汇聚)子层、RLC(无线链路控制子层)以及MAC(媒体接入控制)子层,分别完成头压缩、计算、ARQ(自动重传)和HARQ(混合自动重传)。

图1 用户面协议栈

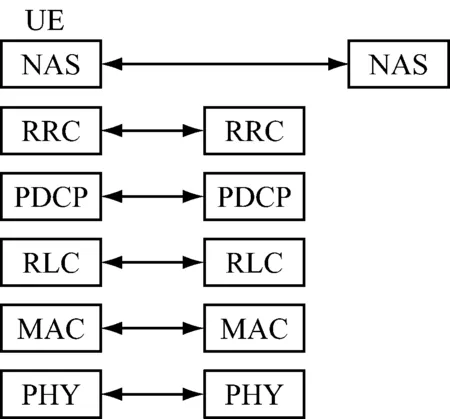

控制面协议栈如图2所示,其中PDCP子层完成计算加密和完整性保护功能。RLC 和MAC子层与用户面相同。RRC完成广播、寻呼、RRC连接管理、RB(资源块)控制、移动性以及UE的测量上报和控制。NAS完成EPS承载管理、鉴权、EMC(EPS连接管理)空闲移动操作。EMC(EPS连接管理)发起空闲寻呼。安全控制。

图2 控制面协议栈

ARM中运行的软件完成高层协议对物理层的指示,实现对物理层各子系统的控制,并完成业务面数据在MAC和物理层之间的传送。软件环境为在eNB侧为嵌入式操作系统VxWorks。编程语言是标准C语言,使用的C语言编译器为DIAB。在UE侧为Linux操作系统。

MAC、RLC、PDCP、NAS等层协议均包括4个模块:高层协议处理模块,信令调度模块,业务数据调度模块,业务面数据传送模块。以MAC层为例,高层协议处理模块主要处理高层信令流程,根据高层协议对物理层的指示,完成高层和物理层资源映射,从而实现对物理层各子系统的控制。信令调度模块主要处理封装了RRC等高层协议消息及HPI的消息发送,为高层协议处理模块提供了一个消息发送平台,对来自RRC,HPI的消息进行解析,分发和函数调度。业务面数据传送模块主要实现业务面数据在MAC和物理层之间的传送,以及随机接入时触发高层协议处理模块的随机接入过程。业务数据调度模块封装了MAC、DPRAM的消息发送,为业务面数据传送模块提供了一个消息发送平台,并对来自MAC和DPRAM的消息进行解析、分发和函数调度。

又如RRC层协议,根据LTE协议栈软件需求,使用效率较高的C语言实现。RRC层模块由2层进程组成,第一层是一个RRC主进程,该进程作为根进程,实现中断导引功能,将具体的消息传给对应UE的RRC子进程。第二层是由RRC主进程创建的子进程。它的子进程可以分为两类:① RRM子进程,该进程实现整个RNC的无线资源管理功能,并为调用它的用户提供相应的RRM功能;② RRC子进程,每一个此类进程对应一个处于RRC连接状态下的UE,其区分是依靠每个UE的U_RNTI。该进程完成UE接入服务中需要的各种信令交互和配置过程,在进行特定公共过程时动态创建对应子进程,在完成后将其删掉。RRC主进程是RRC模块的缺省根进程,它负责对第二层子进程的管理,并将各种信令消息分发给对应UE的RRC子进程。ASN.1编解码模块采用结构化设计,但子函数层应尽可能少,提供编码和解码两个接口函数。

在RLC发送侧进行TFC选择的流程:

(1) 首先,把RRC配置的CTFC值转换成每个传输信道的TF。

(2) 开辟一个二维数组A[x][y],x的最大值为N,N为传输信道的个数;y的最大值是TFCS size。

(3)A[0][y]是一个大小为TFCS size的Boolean类型的数组,用来指示对应下标的TFC是否可用。(叫做“TFC可用数组”)进入TFC选择函数的时候,该数组所有成员被赋值为OPC_TRUE。

(4)A[1][y]~A[N][y]中的1~N与传输信道编号有关,保证传输信道编号从小到大排列(N是传输信道的个数,但是需要自己维护传输信道的编号和数组下标的映射关系);第二维以每个传输信道的TF为编号,第二维的大小就是TFCS的size。需要将配置的CTFC转换成具体的TFS。

(5) 如果此时不是某个RB的TTI的起始时刻,此时不会invoke RLC,则RLC没有数据交给MAC,所以选择TF0。

(6) 要求RRC的配置消息中,传输信道id的分配不能时刻保证是从1开始,按序递增的,所以要自己维护TrCH id和数组下标的映射关系。

(7) 发送侧进行TFC选择的流程。举例:有3条传输信道,TFCS size为6,TFC0为(TF0,TF0,TF0),TFC1为(TF1,TF0,TF0),TFC2为(TF2,TF1,TF1),TFC3为(TF1,TF1,TF0),TFC4为(TF2,TF0,TF0),TFC5为(TF1,TF0,TF1)。在TFC选择的某个时刻,TFC0,TFC2,TFC5是可用的。RLC优先级调度函数必须保证,在一个传输信道的TTI之内,调用的逻辑信道必须是同一个。也就是说,逻辑信道的调度是以这些逻辑信道映射到的传输信道的TTI为周期的。

接收到下行处理中断的发送处理流程:首先检查RB映射的配置,看是否有多个逻辑信道复用到同一个传输信道,如果有,则调用函数进行优先级调度处理。优先级调度完成后,可以确定在这个下行处理中断时刻,有N个RB对应的传输信道会组合在一个TFC中。将这些RB的ID写进一个数组,数组大小为N,下标从0~N-1,遍历这N个RB的模式,激活RLC子进程或者调用函数,获取每个RB进行TF选择所需要的参数。在遍历完了每个可用的RB后,调用TFC选择函数,进行TFC的选择。(需要保证TFC中传输信道的排列顺序是按照传输信道编号从小到大的顺序)根据TFC选择的结果,从共享内存list中或者buffer中读出规定数量的PDU,按照MAC的配置信息,加上MAC头,再将一个TTI内所有的TB合并在一起,加上包头发送给上层协议。

DSP中运行的软件实现物理层部分功能。主要为信道编解码功能实现。信道编解码用于对空中传输的信息进行检错及纠错,以最大限度地降低由于信道质量和其它干扰问题造成的信息传输错误。信道编解码包括CRC校验,卷积编码,viterbi解码,速率匹配,交织,信道复用以及传输信道到物理信道的映射等步骤。信道解码是相应信道编码模块的逆过程。除Viterbi 解码模块在FPGA中实现以外,信道编解码的其它所有模块都是在DSP 上实现的。信道编解码子系统软件运行的软、硬件平台包括:单板处理器 DSP6416,CCS2.12,嵌入式实时操作系统OSEck3.1,编程语言:标准C,汇编语言。

3 结 语

针对目前普遍使用的移动通信实验系统不能完成依据3GPP标准的演进而随之进行针对性的教学工作,本文提出并实现了一种在ARM和DSP及FPGA一体的单板上实现物理层、层二、层三及NAS层的协议栈教学设备。通过利用两块相同硬件结构的单板,分别完成UE和eNodeB的部分功能,通过单板的串口,将协议数据传送到PC机的监控软件中,完成实时消息跟踪。该系统已应用到教学中。下一步工作为改造单板,构成一个具有FER语音和射频功能的系统。

[1] Medium Access Control (MAC) protocol specification (Release 10)[S]. 3GPP TS36.321 V10.0.0,2010.12.

[2] 3GPP TS25.413v4.8.0, (2002-12) Radio Access Network Application Part(RANAP) signalling[S].

[3] 3GPP.Evolved Universal Terresttial Radio Acess Network (E-UTRAN) S1 Application Protocol (SIAP) [S]. 3GPP TS 36.413 V8.3.0.2008.

[4] 3GPP TS 36.322: Evolved Universal Terrestrial Radio Access (E-UTRA) Radio Link Control (RLC) protocol specification.[S]. 2009.9.

[5] 3GPP TS25.413v4.8.0, (2002-12) NodeB Application Part(NBAP) signalling[S].2009.

[6] 3GPP TS 36.322: Evolved Universal Terrestrial Radio Access (E-UTRA) Radio Link Control (RLC) protocol specification[S]. 2009.9.

[7] 3GPP TS 36.321: Evolved Universal Terrestrial Radio Access (E-UTRA); Medium Access Control (MAC) protocol specification[S]. 2009.9.

[8] 3GPP TS 25.323 V4.6.0 (2002-12) Packet Data Convergence Protocol (PDCP) specification[S].

[9] 3GPP TS 25.331 V4.8.0 (2002-12) Radio Resource Control (RRC) protocol specification.

[10] 3GPP TS 24.008 NAS protocol specification[S].

[11] 杜春雷.ARM体系结构与编程[M].北京:清华大学出版社,2003.

[12] 田 泽.嵌入式系统开发与应用[M].北京:北京航空航天大学出版社,2005.

[13] 田 泽.嵌入式系统开发与应用实验教程[M].北京:北京航空航天大学出版社,2004.

[14] 刘和平.TMS320LF240xDSP结构、原理及应用[M].北京:北京航天航空人学出版社,2002.

[15] 江思敏.TMS320LF240xDSP硬件开发教程[M].北京:机械工业出版社,2003.

The Hardware and Software Design and Implementation of Mobile Communication Experiment System

XUJun,ZHANGXiao-yu

(School of Telecommunications Engineering, North China Institute of Science and Technology, Yanjiao 065201, China)

The experiments of communication specialty mainly are to use equipmentto perform interleaving, modulation, channel coding and system signaling experiments, it is more difficult with the 3GPP standard to complete teaching, scientific research, the course design, and graduation design task. Under a full study of 3GPP standard document, a 4G system was developed. The system can complete UE and eNodeB/NodeB sides on the physical layer, and realize the independent development of MAC, RLC, PDCP RRC, NAS on the ARM and the DSP boards. The single board structure was studied, the operating system on the UE side and eNodeB side were transplanted. Part of the process of implementing the RRC, RLC, and physical layer were described. Two single boards are taken as hardware structure, they can be composed of a mobile communication system,. and can connect with the work of teaching and scientific research, and promote evolution of teaching and research of 3GPP standard.

the 3rd generation partnership project; DSP; channel codec; protocol

2014-07-18

国家自然科学基金(61304024)支持项目;中央高校基本业务经费(DX1201A);河北省自然科学基金(F2013508110)

徐 军(1970-),男,湖南新宁人,博士,高级工程师,副教授,研究方向,移动通信系统,嵌入式系统。E-mail:jtcembx@sina.com

TN 929.5

A

1006-7167(2015)05-0100-04