DC/DC开关电源对低压差分信号线干扰模型研究

2014-09-20和军平冯巨标李远航

和军平, 冯巨标, 李远航

(哈尔滨工业大学深圳研究生院,广东深圳 518055)

0 引言

数字信号畸变的成因和预测是高速数字电路信号完整性设计和电源完整性设计中的关键问题[1-2]。当今高密度印制电路板中繁多的高频数字信号、复杂结构和分布的互连线、过孔、电源分配网络(PDN)等使得信号间相互影响的准确分析和预测更具高度的挑战性[3-5]。在印制电路板信号完整性分析及设计领域,国内外研究多集中在信号线间的噪声串扰、反射、时延等方面[6-7]。对于电源分配网络,人们多从供电电压允许波动幅值的角度研究阻抗降低、电容解耦、空腔谐振等现象[8-9]。而事实上,在目前高密度印制电路板中,电源分配网络对高速敏感信号线的近场干扰也成为数字电路工作异常的一个重要原因。特别的,目前同步Buck变换器因其高效、体积小而在负载端DC/DC电源中得到了广泛应用,Buck变换器的高速开关会在印制电路板电源分配网络中产生高幅值的瞬态尖峰噪声,易对临近高速数字信号产生危害,然而对电源分配网络与信号线间相互影响的细致研究尚少[10-11]。

本文即针对某一多层印制电路板中电源分配网络对临近低压差分线(LVDS)的干扰现象进行量化研究,在分析干扰源特征和耦合机理的基础上,建立同步Buck变换器干扰源的高频电路模型,继而利用有限时域积分技术提取出复杂结构的近场干扰耦合通道的电路模型,再将两者结合起来,实现对低压差分线干扰的准确预测。论文首先介绍所研究的多层印制电路板的结构和干扰现象,随后对干扰形成和传播机理进行分析,进而利用场-路结合、实测和电磁仿真结合的方式建立噪声源和耦合通道模型,实现对干扰的预测,并与实际测量结果进行了对比。最后,本文对几种典型布局下,干扰的耦合特性情况也进行了细致分析,并提出了改善措施。

1 多层印制板开关电源对LVDS信号的干扰

所研究高速数字电路的印制电路的主要结构和组成具体如图1所示。其印制板为6层结构、FR4材质、4mil层厚。其在板同步Buck变换器安装在顶层,该变换器通过过孔从下方的12 V电源分配网络PDN抽取电流。信号层与电源层相邻,且经大面积的地层与顶层、底层的元器件隔开。自然的,电源层的12 V电源分配网络与信号层的低压差分信号线对(LVDS)容易相邻。差分信号虽有良好的抗外界干扰能力,但其在高密度印制电路板中也不易做到理想对称。该电路工作时即观测到LVDS信号误码率偏高。实测发现该LVDS线间存在峰峰值可达几十毫伏的尖峰噪声,且该尖峰噪声与12 V电源分配网络上的尖峰噪声、Buck变换器开关上的电压跳变在时间上同步,具体波形如图2所示。

图1 多层PCB板中PDN与信号线的布局结构Fig.1 Layout of PDN and LVDS in a multilayer PCB

已有研究表明,同步Buck变换器功率管高速通断,并与电路的寄生参数共同作用,会在功率开关、Buck输入线/输出线、周围空间形成高幅值的瞬态尖峰电压或电流噪声,严重时即可造成干扰[11-13]。由于本同步Buck变换器处于顶层,其紧邻下方为具有高频屏蔽功能的大面积地层,因而Buck主电路的空间电磁场很难直接耦合到介于两地层间的高速信号线上;然而,同步Buck变换器在开关瞬态时会从12V电源分配网络中抽取高幅值的瞬时电流,造成12V电源分配网络上出现尖峰电压噪声。同处于两GND层间的12V电源分配网络与高速信号线临近,其间易存在近场耦合,尖峰噪声即可通过耦合而传播到LVDS线对上,进而产生干扰。

图2 Buck变换器对LVDS信号线干扰实测波形Fig.2 Measured EMI waveforms from Buck to LVDS

故而高密度印制电路中电源分配网络易对临近高速数字信号形成干扰。特别地,目前同步Buck变换器开关瞬态已可短至3ns,涉及频带达百兆赫兹,加之电源分配网络与高速信号线间相对位置复杂,对干扰进行准确预测、量化指导复杂PCB的设计有着相当难度。本文即利用测试、电磁仿真方法建立起噪声源和耦合通道的精确电路模型,实现对瞬态尖峰干扰的快速、准确预测和分析。

2 开关电源对LVDS尖峰干扰的模型

根据电磁干扰三要素原则,本文在分析干扰源、干扰传播路径的基础上,建立起其各自的精确模型,最后组合起来形成尖峰干扰预测模型。

2.1 Buck变换器尖峰噪声模型

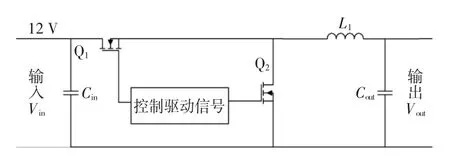

本文同步Buck变换器主电路原理如图3所示,其输入电压12 V、输出电压3.3 V、额定输出电流10 A、工作频率600 kHz。其中,12 V输入电压由12 V电源分配网络得到。分析可知,Buck变换器Q1中的尖峰电流是输入12 V电源分配网络上电压尖峰噪声形成的直接原因。Q2源漏极电压是Buck输出端电压尖峰噪声形成的直接原因。利用准确的开关器件宏模型、准确的电感器、电容器及PCB互连线模型,可以预测Buck变换器的各开关噪声[14-15]。本文采用Agilent4396B实测方法,得到电感、电容等无源器件和Buck电源PCB连线的高频模型,再结合Saber软件库中开关器件宏模型即建立起图4所示的同步Buck变换器噪声的电路仿真模型。

图3 同步Buck变换器主电路Fig.3 Synchronic Buck converter’s main circuit

图4 同步Buck电路高频EMI模型Fig.4 High frequency EMI model of synchronic Buck

在图4模型中,电路交流环路的寄生电感Lloop、MOSFET管源漏极间寄生电容Cds、环路寄生电阻对电压、电流振荡尖峰峰值幅值、频率起着重要作用[11]。对该模型进行时域仿真,可得到开关管Q2两端的电压、12 V电源分配网络上的噪声电压波形。图5显示了仿真Q2两端的电压整形和12 V电源分配网络的噪声波形。可见,在功率开关开通、关断瞬间,在Q2两端和12 V电源分配网络上均出现了尖峰电压。图6显示了相应的实测噪声波形。比较后可看出,两者在尖峰振荡频率、幅值及趋势上一致,表明所建噪声源的模型是有效的。

图5 Q2两端电压及12 V PDN噪声电压仿真波形Fig.5 Simulated waveforms of Q2Vds and 12 V PDN noise

图6 实测12 V输入线电压噪声波形Fig.6 Measured waveforms of Q2voltage and 12 V PDN noise

2.2 PDN与LVDS近场耦合模型

所研究的12 V电源分配网络与低压差分信号线的细致结构如图7所示。电源分配网络和差分信号线处于不同层,两者的尺寸及相对位置也不很规则。它们通过各自的过孔与顶层的元器件相接。其中,12 V电源分配网络宽3 cm、长10 cm。差分信号线线宽4 mil、线间距8 mil、线长7 cm,以保持50 Ω特性阻抗。严格来讲,在各过孔、电源分配网络及差分信号线均存在近场耦合,但由于上述结构复杂,其耦合关系难用解析形式求出,用简单集总电路元件来描述也存在微小参数测量困难、高频时分布效应明显等问题,故本文利用基于有限时域积分电磁计算工具提取三维耦合的PEEC高频电路模型。

图712 V PDN与LVDS布局示意Fig.7 Detail layout of PDN and LVDS

2.2.1PDN与LVDS耦合参数模型的提取

部分元等效电路(PEEC)法以麦克斯韦积分电磁方程为出发点,将三维结构导体分解为多个网格单元,每个网格单元由电阻、电感和电容代表,再计算出这些单元间的互感和互容,从而将三维导体等效成一个复杂的电路模型。PEEC方法具有精度高,速度快等优点,可准确地得出复杂结构导体的高频电路模型[16]。利用PEEC方法,复杂结构的PCB导体也可通过合理的剖分,转化成由集总元件组成的等效电路模型,进而利用通用的电路分析方法或软件进行时域、频域的分析。

本研究利用CST PCB Module软件对图7所示的PCB进行PEEC电路参数提取。CST PCB Module软件可以方便的导入Protel的PCB设计,再设定适当的剖分尺寸参数,即可得到整个PCB的高频电路模型,从而得到了包含12 V电源分配网络与低压差分信号线间耦合效应的电路模型,该模型具体参数过多,故用图8中间的方块进行对外等效示意。

2.2 .2PDN与LVDS端接器件的等效模型

众所周知,近场耦合干扰的强弱还与12 V电源分配网络、差分信号线对的端接器件有密切关系。12 V电源分配网络的一端接Buck变换器的输入,另一端接一组解耦电容;差分信号线对的两端则分别接差分驱动器和差分接收器。上述端接器件的内部结构复杂,为简化处理,本文利用这些器件的端口等效阻抗来近似其端接效应。12 V电源分配网络的解耦电容的阻抗可测量得出,其值设为Z。差分驱动器和差分接收器的内部电路结构复杂,本文在分析其主要结构基础上,确定差分信号驱动器和接收器对外等效阻抗模型。

差分驱动器主要由平衡驱动电路和反馈回路构成[17]。根据其结构,本文使用10 kΩ接地电阻表示驱动器电流源的内阻,用连接于两条驱动线间的100 Ω电阻表示阻抗匹配电阻,这样得到图8右侧所示的驱动器等效阻抗[17];由于差分接收器输入阻抗与差分线对的特性阻抗匹配,本文在两根差分线的接收端上各接一个50 Ω接地电阻,以匹配差分线的差模阻抗,具体电路如图8左侧部分[17]。当然,差分信号驱动器和接收器的等效端接电阻还会有寄生电容,但其值很小、影响不大,故本模型未予标出。

将上述PDN与LVDS的近场耦合PEEC电路模型、PDN与LVDS端接器件的等效阻抗模型组合起来,就得到图8所示的PDN与LVDS近场耦合的高频电路模型。

图8 PDN与LVDS间耦合效应的CST模型Fig.8 Coupling effect CST model between PDN and LVDS

3 干扰模型的验证和分析

3.1 干扰模型的预测和验证

将同步Buck变换器的干扰源高频电路模型和干扰耦合通道高频模型结合起来,就可以预测干扰。然而,直接将两个高频电路连接起来进行时域仿真,会因开关瞬态时间短、耦合通道参数多而运算时间很长。本文进而采用先用Saber软件仿真出Buck变换器产生的12 V电源分配网络的噪声波形,再将其导入图8所示的耦合通道模型进行仿真,从而快速得到LVDS上遭受到干扰波形。

具体来讲,将图5仿真得到的12 V电源分配网络的噪声再作为激励源,加入到图8的激励源端口,由CST Circuit模块进行仿真运算。图9(a)显示了12 V电源分配网络与差分信号线对平行、间距10 mil时,仿真得到LVDS线间干扰波形,图9(b)进一步显示了Q2关断瞬间实测和仿真的干扰细节波形,可以看出两者在幅值、振荡频率、变化趋势上很接近,表明所建的干扰预测模型是有效的。

图9 LVDS实测和仿真干扰波形Fig.9 Measured and simulated EMI waveforms in LVDS

3.2 PDN与LVDS耦合分析与改善

除预测干扰外,所建的干扰模型还可用来量化考察不同布局下电源分配网络与低压差分信号线间的耦合情况,以指导PCB改善设计。本节即对几种典型布局时的耦合情况进行分析。

首先考察12 V电源分配网络与LVDS平行、而两者水平间距不同时的耦合强弱变化情况,具体布局示意如图10所示。仿真时,设LVDS长为10 cm,两者间距分别为10、20、40和60 mil。利用图8所示方法可得到12 V电源分配网络到LVDS线-线间的干扰电压传递函数,不同间距时干扰的传递函数如图11所示。图中曲线从上到下,依次为10、20、40和60 mil。可以看出,当间距很小时,感应到的噪声变化很小,但随着间距增大到4倍时,感应到的噪声迅速减小。用时域仿真也可得出上述间距下LVDS感应到的干扰峰值分别为41、37、5、1.5 mV,可见两者趋势一致。产生上述现象的原因,主要是12 V电源分配网络边沿处的电场、磁场分布变化很不均匀而引起的。

图10 间距/长度不同时的布局Fig.10 Layouts with different distances and lengthens

图11 间距不同时的传递函数Fig.11 Transfer function curves with different distances

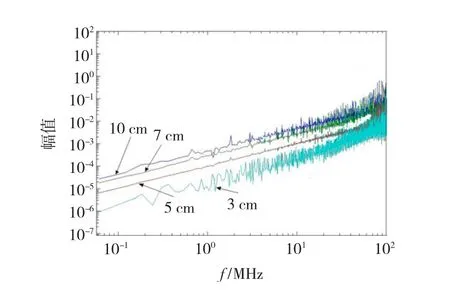

类似地,保持10 mil间距不变,仅改变LVDS的长度,可仿真得到3、5、7、10 cm长度时LVDS的感应噪声的传递函数,具体如图12所示。可以看出,在100 MHz前,噪声与长度近似成线性关系。

图12 不同LVDS长度时的传递函数Fig.12 Transfer function curves with different lengthens

对于本多层印制板中Buck变换器经12 V电源分配网络对LVDS信号造成的尖峰干扰,可以通过在开关器件上施加阻容或阻感缓冲电路、选择软反向恢复MOSFET管等措施从源头减小干扰大小;也可以在12 V电源分配网络上施加高频滤波等解耦措施来降低耦合程度。此外,使LVDS远离电源分配网络或在电源分配网络与LVDS间添加局部GND线屏蔽,也能有效降低两者间的干扰传播。

4 结论

本文对多层印制电路中在板DC/DC同步Buck变换器经电源分配网络而对LVDS信号造成干扰现象的机理、预测模型和抑制进行了细致研究,得到如下结论:

1)同步Buck变换器开通、关断瞬间的电压和电流尖峰是主要干扰源,印制板GND层间的12 V电源分配网络与LVDS信号线的近场耦合是干扰主要传播通道;

2)基于PEEC原理,提取和建立了描述12 V电源分配网络与LVDS信号线间近场耦合的高频电路模型,仿真表明电源分配网络与LVDS信号线间距离、长度对耦合大小影响强烈;

3)建立起同步Buck变换器的噪声模型,结合耦合通道的高频电路模型,实现了LVDS感应干扰的较准确预测,证明了所提模型和方法的有效性。

[1]FAN Jun,YE Xiaoning,KIM Jingook,et al.Signal integrity design for high-speed digital circuits:progress and directions[J].IEEE Transactions on Electromagnetic Compatibility,2010,52(2):392-400.

[2]GOYAL R.Managing signal integrity PCB design[J].IEEE Spectrum,1994,31(3):54-58.

[3]WU Boping,TSANG Leung.Signal integrity analysis of package and printed circuit board with multiple vias in substrate of layered dielectrics[J].IEEE Transactions on Advanced Packaging,2010,33(2):510-516.

[4]CHANG R W Y,SEE Kyeyak,CHUA Engkee.Comprehensive analysis of the impact of via design on high-speed signal integrity[C]//IEEE 9th Electronics Packaging Technology Conference,December 10-12,2007,Singapore.2007:262-266.

[5]LIU Enxiao,LI Erping,LI Lewei,et al.Finite-difference timedomain macro-model for simulation of electromagnetic interference at high-speed interconnects[J].IEEE Transactions on Magnetics,2004,41(1):65-71.

[6]LI DING,BLAAUW D,MAZUMDER P.Accurate crosstalk noise modeling for early signal integrity analysis[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2003,22(5):627-634.

[7]NAKHLA N M,DOUNAVIS A,ACHAR R,et al.Depact:delay extraction-based passive compact transmission-line macromodeling algorithm[J].IEEE Transactions on Advanced Packaging,2003,22(5):627-634.

[8]SWAMINATHAN M,CHUNG Daehyun,GRIVET-TALOCIA S,et al.Designing and modeling for power integrity[J].IEEE Transactions on Advanced Packaging,2005,28(1):13-23.

[9]WU Tzonglin,CHUANG Haohsiang,WANG Tingkuang Overview of power integrity solutions on package and PCB:decoupling and EBG isolation[J].IEEE Transactions on Advanced Packaging,2010,52(2):346-356.

[10]WU Songping,KAM Keong,POMMERENKE D,et al.Investigation of noise coupling from switching power supply to signal nets[C]//2010 IEEE International Symposium on Electromagnetic Compatibility,July 25-30,2010,Fort Lauderdale,USA.2010:79-84.

[11]LI Zhe,POMMERENKE D.EMI specifics of synchronous DCDC buck converters[C]//2005 IEEE International Symposium on Electromagnetic Compatibility,August 9-13,2005,Chicago,USA.2005:711-714.

[12]AOUINE O,LABARRE C,COSTA F.Measurement and modeling of the magnetic near field radiated by a Buck chopper[J].IEEE Transactions on Electromagnetic Compatibility,2008,50(2):445-449.

[13]张晓光,和军平,孙力,等.Flyback开关电源近场磁辐射预测与抑制[J],电机与控制学报,2010,2010,14(10):21-25.

ZHANG Xiaoguang,HE Junping,SUN LI,et al.Magnetic near field predication and suppression of a Flyback SMPS[J].Electric Machines and Control,2010,14(10):21-25.

[14]和军平,姜建国.离线式PWM开关电源传导电磁干扰的分析研究[J].中国电机工程学报,2003,23(6):91-95.

HE Junping,JIANG Jianguo.Research on conducted EMI of an off-line PWM switched mode power supply[J].Proceedings of the CSEE,2003,23(6):91-95.

[15]曹毅,李征帆,毛吉峰.互连封装结构电特性分析中的改进PEEC三维建模[J].电子学报,2000,28(2):65-71.

CAO Yi,LI Zhengfan,MAO Jifeng.A modified 3-D PEEC model in interconnect and packaging electric analysis[J].Acta Electronica Sinica,2000,2000,28(2):65-71.

[16]CONG Guorui,NI Guyan,LUO Jianshu,et al.Analysis of S-parameters of a coupler based on the partial element equivalent circuit method[C]//2011 International Conference on Electronics Communications and Control,September 9-11,2011,Ningbo,China.2011:739-742.

[17]CHEN Mingdeng,SILVA-MARTNEZ J,NIX M,et al.Low-voltage low-power LVDS drivers[J].IEEE Journal of Solid-State Circuits,2005,40(2):472-479.