基于链式的信号转移冗余TSV方案

2014-07-08王伟张欢方芳陈田刘军汪秀敏

王伟,张欢,方芳,陈田,刘军,汪秀敏

1.合肥工业大学,合肥 230009

2.情感计算与先进智能机器安徽省重点实验室,合肥 230009

◎理论研究、研发设计◎

基于链式的信号转移冗余TSV方案

王伟1,2,张欢1,2,方芳1,陈田1,2,刘军1,2,汪秀敏1

1.合肥工业大学,合肥 230009

2.情感计算与先进智能机器安徽省重点实验室,合肥 230009

三维集成电路(3D IC)带来了诸多的益处,譬如高带宽,低功耗,外形尺寸小。基于硅通孔的三维集成得到了行业的广泛采用。然而,硅通孔的制造过程引入了新的缺陷机制。一个失效的硅通孔会使整个芯片失效,会极大地增加成本。增加冗余硅通孔修复失效硅通孔可能是最有效的提高良率的方法,但是却带来了面积成本。提出了一种基于链式的信号转移冗余方案,输入端从下一分组选择信号硅通孔传输信号。在基于概率模型下,提出的冗余结构良率可以达到99%,同时可以减少冗余TSV的数目。

三维集成电路;硅通孔;容错

1 引言

随着集成电路的发展,为了在一定尺寸的芯片上实现更多功能,延续摩尔定律,三维方向上的封装应运而生。硅通孔(Through-Silicon-Via,TSV)作为新兴的互连技术,是指在晶圆和晶圆之间、芯片和芯片之间制作垂直导通,实现芯片间的信号传输[1]。3D技术拥有诸多益处,可以达到更高的密度,拥有小的外形尺寸,以及低功耗和高带宽等优点。但是,增加的功耗密度,制造工艺的复杂,良率问题等都对这项新兴技术提出了挑战[2]。为了解决这些问题,最近几年,国内外对于这些问题的研究可以分为三类,一类是热量问题,降低功耗密度,通过对散热通孔的分配缓解散热问题[3-4]。一类是测试问题,包括绑定前测试和绑定后测试[5]。还有一类是容错技术,在制造工艺中出现的错误,通过恢复机制避免芯片无法正常工作,提高良率。

3D芯片是将多层芯片堆叠,硅通孔(Through-Silicon-Via,TSV)是3D互连的其中一项技术。图1所示为基于硅通孔(TSV)的三维芯片示意图。根据堆叠方式的不同,分为芯片到芯片的堆叠(D2D),芯片到硅片的堆叠(D2W),硅片到硅片的堆叠(W 2W)[6]。W 2W的生产效率高于其他两种堆叠方式,但是良率较低,D2W可以通过筛选实现已知合格芯片(Known Good Die,KGD)间的堆叠,所以良率较高。

图1 基于硅通孔的三维芯片堆叠示意图

3D工艺三种常见的技术有硅通孔(TSV)的形成,晶圆的打薄和晶圆的对齐或者芯片的绑定[7]。硅通孔(TSV)的制作过程可以分为5个阶段:打孔,氧化物沉淀,铜钟子沉淀,注入导电铜,化学机械抛光[8]。硅通孔(TSV)与其他互连通孔的差异主要体现在尺寸小和穿通硅衬底两个方面。

2 硅通孔(TSV)的故障问题及良率分析

由于三维芯片的发展仍处于起步阶段,硅通孔(TSV)的制作工艺仍不成熟,在不同阶段硅通孔(TSV)会出现不同的故障。

2.1 基于硅通孔(TSV)的故障问题

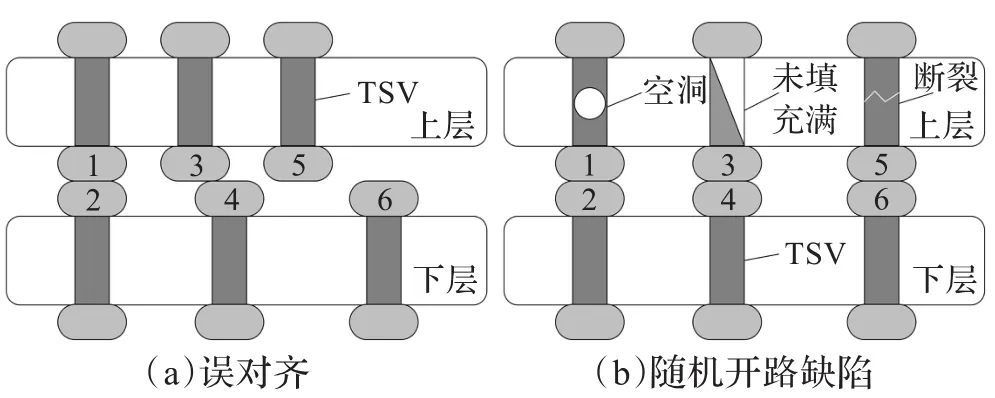

在三维集成中主要存在着两种良率损失,堆叠良率损失和封装良率损失[9]。堆叠良率损失是在多个芯片的堆叠过程中产生的,通过绑定前测试和匹配策略避免堆叠损坏芯片。封装过程也产生各种各样的故障问题,传统的2D晶圆的厚度在600~900 μm之间,但是在3D晶圆中,由于每一个晶圆需要一个薄化的过程来将硅通孔(TSV)从硅衬底中暴露出来,导致厚度下降至15~60 μm[10],由于厚度直线下降,3D晶圆变得十分脆弱,容易卷曲造成断裂。三维芯片需要绑定上下层的硅通孔(TSV),形成信号的通路,但是硅通孔(TSV)的直径非常小,一般为4~8 μm之间,再加上硅通孔(TSV)的数目非常多,上下层的对齐变得非常困难,再加上3D晶圆的厚度非常小,容易卷曲造成上下层的误对齐现象,这些都对绑定精度提出了更高的要求。随机开路缺陷和误对齐成为了硅通孔(TSV)失效的两个主要原因[11]。

图2所示分别表示了两种情况,图2(a)中椭圆是衬垫,在上下层的绑定中衬垫3和衬垫4发生了偏移,没有完全绑定在一起,此时信号可以传输,但是却影响电气特性,而衬垫5和衬垫6完全没有绑定在一起,此外,硅通孔(TSV)和衬垫之间也有可能出现接触故障[12]。图2(b)中在通孔注入导电材料时,可能会发生填充不完整的情况,此时在硅通孔(TSV)内部造成空洞,影响信号的正常传输。

图2 TSV失效原因

图3所示有三种冗余结构,图3(a)单链方案[13]将所有硅通孔(TSV)通过多路选择器(MUX)连接形成硅通孔(TSV)链,在一条链上只有一个冗余硅通孔(TSV),单链方案中容错能力较差,单个链上只可以出现一个失效硅通孔(TSV)。为了提高良率,必须在链的长度上加以限制,最终得出为了达到90%以上的良率,需要限制单链的硅通孔(TSV)数目为50个。图3(b)所示,分组内冗余比率为4∶2,在300个硅通孔(TSV)的数目下,良率可以达到99.8%。替换方案不明确冗余硅通孔(TSV)的位置,当分组内出现失效时,使用相邻的硅通孔(TSV)传输信号,虽然方案可以达到较高的良率,但是冗余比率较高,在硅通孔(TSV)间距为40 μm的情况下,冗余硅通孔(TSV)的开销占用了0.3%,当硅通孔(TSV)的数目上升时,相应的冗余成本会渐渐升高。绑定过程出现问题十分容易造成硅通孔(TSV)失效呈现聚类分布,即失效硅通孔(TSV)并不是等概率分布在一个平面内,图3(c)中转换器(Switch)的设计可以使信号的传输相互交叉而彼此不影响,转换器(Switch)由三个多路选择器组成,路由方案可以允许信号使用较远的硅通孔(TSV)传输信号,文献[14]在此基础上又提出了相关算法解决信号传输方向问题。此外在文献[15-17]同样提出了不同的冗余方案。

2.2 针对绑定和硅通孔的良率分析

图3 冗余方案

基于三维堆叠集成电路的良率模型十分复杂,这是由于复杂多变的工艺过程造成的。良率模型不仅需要考虑芯片的良率,还要考虑堆叠良率和封装良率。3D集成出现了额外的制造步骤,譬如硅通孔(TSV)的形成和绑定,这些都是三维集成电路所独有的。在文献[6,10]中对3D良率模型进行了深入的探讨,针对新型缺陷,在未考虑任何冗余方案的情况下,最终的良率可以如下表示:

Yield是指仅考虑绑定和硅通孔(TSV)损坏下的最终良率。Ybonding是一次绑定过程中的绑定良率,fTSV是单个硅通孔(TSV)失效的概率,NTSV是硅通孔(TSV)的数目,Ntier是绑定层数,在不考虑任何冗余方案的情况下,硅通孔(TSV)的良率是所有硅通孔(TSV)都完好的概率,考虑绑定过程的良率是绑定良率的层数减一次方。目前,还没有一个准确的绑定良率的准确模型,通常被假定为一个常数,不同的制造工艺下以及不同的TSV的尺寸,单个TSV的失效率也不是一个固定的数值,目前还没有一个准确的失效数值,通常是将硅通孔(TSV)的失效率设在0.001%~0.01%之间。

图4是未考虑冗余方案的良率示意图,横坐标表示的是硅通孔(TSV)的总数,从1 000个到15 000个,基本满足了基于NOC设计所需的硅通孔(TSV)数目,纵坐标表示的是最终良率,为了对比不同数量和不同层数间的良率关系,单个硅通孔(TSV)的失效率设为0.001%和0.01%,层数分别为3,5,绑定良率假定为0.95,图中不同曲线代表的是不同层数和不同的硅通孔(TSV)失效率下的最终良率。当硅通孔(TSV)的失效率较低时,最终良率呈现较平缓的下降趋势,而当硅通孔(TSV)的失效率较高时,随着层数和硅通孔(TSV)数目的增加,曲线下降明显,当TSV数目超过5 000个时,良率降为50%以下,当硅通孔(TSV)数目为15 000个时,良率就只在13%~19%之间。即使单个硅通孔(TSV)的失效率较低,当硅通孔(TSV)数目达到6 000个时,良率最终下降到80%以下。

图4 未考虑冗余方案的良率图

由于假定的绑定的芯片都是已知良好的,所以实际的良率可能会更低,单个硅通孔(TSV)的失效有可能会引起整个芯片无法正常工作,而丢弃堆叠芯片的成本是相当高的,基于成本分析,通过冗余方案增加硅通孔提高良率是一项非常有效的方法。

3 基于链式的信号转移冗余方案

3.1 基于链式的多路冗余方案

本文基于链式的设计,提出了将信号依序转移至下一分组的冗余硅通孔方案。图5所示为基于链式的信号转移冗余方案,图中所示连接两层的是硅通孔,对所有硅通孔进行了分组,分为信号硅通孔组和冗余硅通孔组,在信号硅通孔组里每一个分组包括N个硅通孔,分组间通过N条信号线相连,冗余分组在分组的末端,如图所示,分组中的硅通孔进行了排序,分别为1,2,…,N。分组内的输入信号可以通过分组间的连线传递到下一分组,并可以通过下一分组的任一硅通孔传输信号。

图5 基于链式的信号转移冗余方案

当出现失效硅通孔时,输入信号使用下一分组的信号硅通孔传输信号,而此时下一分组的硅通孔被占用,则下一分组被占用的输入信号依次使用下一分组的信号硅通孔,直至冗余硅通孔。从失效硅通孔直至冗余硅通孔形成的信号转移路径,形成了一条信号链。

假设有M个分组,每一分组中的第1个硅通孔形成一条信号转移链,称之为1链,包含M个硅通孔,依次类推,每一分组的最后一个硅通孔形成N链,当1链中的某个硅通孔出现失效时,将输入信号转移至下一分组的信号硅通孔传输,此时下一分组的1链中的硅通孔被上一分组的输入信号占用,本该从这个硅通孔传输信号的输入信号转移到下一分组,直至最后一个输入信号使用冗余分组中的硅通孔传输信号。

图5中所示,当1链中的第一个硅通孔出现失效时,in_1使用下一分组1链中的硅通孔传输信号,分组2的in_1由于初始硅通孔被前一分组占用,信号传输到下一分组的同一位置的硅通孔,依次转移信号,直至最后一个in_1使用冗余硅通孔传输信号。当1条链上出现两个以上失效硅通孔时,由于一条链上只允许一个硅通孔发生故障问题,此时选择从下一分组开始的第一条没有失效硅通孔的链,即转移至另一条链进行信号的依序转移。冗余分组中有N个硅通孔,可以通过控制多路选择器(MUX),达到修复N个以下的失效硅通孔的目的,当失效硅通孔出现大于N的情况时,由于冗余分组只有N个硅通孔,所以无法完成容错。

图6所示是当N=2时分组r和分组r+1的结构示意图,每个分组中有两个硅通孔,当分组r中的第一个硅通孔出现失效时,通过控制多路选择器(MUX),使得信号从分组r+1的第一个硅通孔传输,如图中红色实线标识,而原先需要从这传输的信号则顺序转移至下一分组的第一个硅通孔,直到这条链的最后一个输入使用冗余硅通孔传输信号。

图6 当N=2时分组间结构示意图

从图6中可以看出,在分组中由于多路选择器(MUX)的作用,分组中一个输入可以通过分组内的所有TSV传输信号,也可以通过多路选择器(MUX)的作用使信号转移到下一分组。

3.2 修复过程

方案由M个分组构成,每个分组包括N个硅通孔,分组中的硅通孔依序分为1,2,…,N,在最后一个分组之后是冗余硅通孔分组,分组中的硅通孔数目也为N。每个分组中的第一个硅通孔组成一条链,称之为1链,每个分组中的第二个硅通孔也构成一条链,称之为2链,依次类推,最后一个硅通孔构成的链称之为N链。

在测试阶段,对硅通孔进行信号测试,测试出所有失效硅通孔的位置,位置包括分组位置和组内位置。分组位置是指失效硅通孔处于哪一个分组内,组内位置是指失效硅通孔在组内的位置,一个分组包括N个硅通孔。

确定了失效硅通孔的位置后,根据失效硅通孔在分组链中的先后顺序依次确定修复路径,修复路径是指为了实现信号的正常传输信号依次使用相邻分组的硅通孔传输信号而从失效硅通孔到冗余硅通孔形成的一条链,由于方案只有N条链,所以最终的修复路径最多只有N个,即容错能力只有N,本方案的修复原则是从失效硅通孔的下一分组寻找第一条不含失效硅通孔的链进行信号的传输,直至最后一个冗余分组的冗余硅通孔,依序使每一个失效硅通孔都可以有一条链进行信号的传输,当失效硅通孔的数目超过N时,本方案无法完成容错。

图7所示为修复过程,黑色矩形代表的是信号硅通孔,白色矩形代表的是冗余硅通孔,用M表示分组,N表示分组内硅通孔,M1表示第一个分组,N1表示第一个硅通孔,依次类推。图示利用当M和N均为4时阐述两种失效硅通孔分布情况下的修复过程,利用矩阵来表示失效硅通孔的分布情况,M为行数,N为列数。在情况1下,A11,A22,A33,A44分别出现了失效硅通孔,当A11出现失效时,从下一分组找到1链中不含失效硅通孔,所以本应从A11传输的信号从A21传输,依序使用下一分组的1链中的硅通孔传输信号,直至冗余硅通孔,如图中黑色虚线所示,所有失效硅通孔可以利用矩阵如图所示,A11利用1链顺序转移信号,A22利用2链顺序转移信号,A33利用3链顺序转移信号,A44利用4链顺序转移信号。在情况2下,A11,A21,A22,A23出现了失效硅通孔,由于A21是失效硅通孔,所以A11不能使用1链顺序转移信号,可以得到4链是第一个不含失效硅通孔的链,所以本应在A11传输的信号利用A24传输信号,顺序利用4链中的硅通孔顺序转移信号。A21利用1链顺序转移信号,A22利用2链顺序转移信号,A23利用3链顺序转移信号。可以看出当失效硅通孔超过4个时,本方案无法完成容错。

4 实验结果与分析

图7 修复过程

本文提出的容错方法是基于链式的信号转移方法,在设计中就需要确定N,在实际的设计中,硅通孔通常是以网格的形式分布在功能块之间的空白区域,从而形成了块状分布,块中硅通孔的数目通常不会很大,为了确定N,硅通孔的数目在1 000~15 000之间变化。

4.1 良率比较

在良率模型中可以建立概率模型分析出现n个失效硅通孔的概率,n个失效硅通孔可以由二项分布得到,基于单个硅通孔的失效率,计算出现n个失效硅通孔的概率。

N代表的是硅通孔的总数,n是出现失效硅通孔的数目,fTSV是单个硅通孔的失效率,出现n个失效硅通孔的概率可以由公式(2)得到。公式(3)表示的是出现n个以及n个以下失效硅通孔的概率。

单个硅通孔的失效率假设为0.01%,将Totalfault_TSV=n大于99.9%下的失效硅通孔的数目,定义为最大失效数,得到的最大硅通孔失效数目如图8所示,横坐标表示的是硅通孔的总数,当数目达到12 000个时,出现6个以下失效硅通孔的概率为99.97%,即当一个块中的硅通孔数目达到12 000个时,出现6个以下失效硅通孔的概率高于99.9%,可以看出出现高于6个失效硅通孔的概率仅在0.03%以下。当一个块中的TSV数目为1 000个时,出现2个以下失效硅通孔的概率多于99.9%,本方案的N为2,此时只需要增加两个冗余硅通孔。由于硅通孔占的面积要远高于其他部件,过多增加冗余硅通孔会增加不必要的成本。

Precovery_TSV代表的是修复率,在本方案中失效硅通孔小于N的情况可以达到100%的修复率,乘以出现n个失效硅通孔的概率可以得到本方案的最终良率。当硅通孔的数目为1 000时,最大失效数为2,出现0个失效硅通孔的概率为90.483%,出现1个失效硅通孔的概率为9.049%,出现2个失效硅通孔的概率为0.452%,修复率为99.984%。

图8 最大失效数

在文献[13]中为了提高方案的良率,必须对分组当中的硅通孔的数目进行一定程度的限制,在实际的硅通孔块中如果硅通孔的数目较高时就必须进行分组的划分,为了达到较高的良率,最终确定分组中硅通孔数目为50个时较为合适,为了对良率进行完整的比较,单链方案中分组硅通孔数目在这里分别取50个和200个。

图9所示横坐标代表的是硅通孔的数目,纵坐标代表的是良率,随着数目的增加,良率都呈现下降的趋势,而本方案随着硅通孔数目的增加良率仍然可以维持一个较高的数值,从图9中的比较可以看出本方案相对分组中硅通孔数目分别为50个和200个的单链方案在良率上有着较大的提升,当TSV的数目达到15 000个时,良率相较50个和200个的单链方案有着0.36%和1.44%的提升,而相对于没有采取任何冗余方案的良率有着高达77.7%的提升。

图9 良率比较

表1 硬件成本对比

4.2 面积成本

为了实现冗余方案,带来了额外的硬件成本,不同冗余方案的冗余比率不同,在这里的面积成本主要分为两类,一类是冗余硅通孔带来的面积成本,另一类是多路选择器(MUX)带来的面积成本。为了对比详细的成本,假定信号硅通孔的数目为5 000个,从表1中可以看出各开销对比。表中所示数据单位为个,第二行为冗余硅通孔个数,单链方案分组中的硅通孔数目分别取50个和200个。从表中可以看出本文方案在冗余TSV数目上远低于其他方案,由于本方案使用了多路选择器(MUX)进行信号的转移,所以多路选择器(MUX)的成本也相对较大。由于硅通孔的面积远高于其他电路,所以这种代价是可接受的。

电路面积依据标准单元库,并查找工艺库中对应单元的面积参数,综合得到各方案的面积开销。在90 nm工艺下,硅通孔的面积取10 μm×10 μm,在这里不考虑耦合带来的信号完整性问题,由于单链方案需要考虑分组数来提高良率,所以限制分组数会提高冗余硅通孔的数目。图10所示,横轴代表的是硅通孔的数目,分别取1 000个,5 000个,10 000个。纵轴代表面积成本,分为四种方案比较,文献[14]的网格按(16×16)∶32的比例,16×16是指硅通孔呈16行16列分布,32代表的是冗余硅通孔的数目。从图中可以看出文献[14]的面积成本较大,这是因为在转换器(Switch)中有三个多路选择器(MUX)组成,一个信号通过一个多路选择器(MUX)控制信号方向,冗余比率也较其他方案较高,以(N×N)∶2N为例,冗余比率为2N/N2,可以看出相应的面积成本会高于其他方案。本方案和分组数为200的单链方案相比开销较大,这是因为分组数较高的话,冗余硅通孔数目会显著降低,降低了面积成本,但是最终良率会降低,文献[11]的冗余硅通孔数目相较其他方案较高,面积成本也较高。

图10 面积成本

5 总结

本文提出了一种基于链式的转移信号容错方案,根据不同硅通孔数目带来的最大失效数确定冗余硅通孔的数目,以此提高最终的良率。经过对多路选择器(MUX)的配置,在假设单个硅通孔失效率为0.01%的前提下,方案可以保证容错率达到99.9%以上,但是使用相邻分组硅通孔传输信号带来了相应的延迟开销。

[1]童志义.3DIC集成与硅通孔(TSV)互连[J].电子工业专用设备,2009,38(3):27-34.

[2]Cassidy C,Kraft J,Carniello S,et al.Through silicon via reliability[J].IEEE Transactions on Device and Materials Reliability,2012,12(2):285-295.

[3]王伟,张欢,方芳,等.2TF:一种协同考虑过硅通孔和热量的三维芯片布图规划算法[J].电子学报,2012,40(5):971-976.

[4]余慧,吴昊,陈更生,等.一种堆叠式3DIC的最小边界热分析方法[J].电子学报,2012,40(5):865-870.

[5]Chen P Y,Wu C W,Kwai D M.On-chip testing of blind and open-sleeve TSVs for 3D IC before bonding[C]//2010 28th VLSI Test Symposium(VTS),2010:263-268.

[6]邓丹,吴丰顺,周龙早,等.3D封装及其最新研究进展[J].微纳电子技术,2010,47(7):443-450.

[7]Garrou P,Bower C,Ramm P.Handbook of 3D integration:volume 1-technology and applications of 3D integrated circuits[M].[S.l.]:Wiley,2011.

[8]Marinissen E J,Zorian Y.Testing 3D chips containing through-silicon vias[C]//International Test Conference,2009:1-11.

[9]Xu Qiang,Jiang Li,Li Huiyun,et al.Yield enhancement for 3D-stacked ICs:recent advances and challenges[C]//2012 17th Asia and South Pacific Design Automation Conference(ASP-DAC),2012:731-737.

[10]Lung Chiaoling,Chien Juihung,Shi Yiyu,et al.TSV fault-tolerant mechanisms with application to 3D clock networks[C]//2011 International SoC Design Conference(ISOCC),2011:127-130.

[11]Kang U,Chung H J,Heo S,et al.8Gb 3D DDR3 DRAM using through-silicon-via technology[C]//IEEE International Solid-State Circuits Conference-Digest of Technical Papers,2009:130-131.

[12]Chew P C,Li L,Xue J,et al.Through Silicon Via(TSV)redundancy-a high reliability,networking product perspective[C]//2012 14th International Conference on Electronic Materials and Packaging(EMAP),2012:1-5.

[13]Hsieh A C,Hwang T T.TSV redundancy:architecture and design issues in 3-D IC[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2012,20(4):711-722.

[14]Jiang Li,Xu Qiang,Eklow B.On effective TSV repair for 3D-stacked ICs[C]//Design,Automation&Test in Europe Conference&Exhibition(DATE),2012:793-798.

[15]Laisne M,A rabi K,Petrov T.Systems and methods utilizing redundancy in semiconductor chip interconnects:US,Patent Application 12/480,754[P].2009-06-09.

[16]Huang T C.High-performance built-in self-routing for through-silicon vias[J].Electronics Letters,2012,48(9):480-482.

[17]王伟,董福弟,方芳,等.一种多链式结构的3D-SIC过硅通孔(TSV)容错方案[J].计算机工程与应用,2012,48(20):75-80.

WANG Wei1,2,ZHANG Huan1,2,FANG Fang1,CHEN Tian1,2,LIU Jun1,2,WANG Xium in1

1.Hefei University of Technology, Hefei 230009, China

2.Anhui Province Key Laboratory of Affective Computing and Advanced Intelligent Machine, Hefei 230009, China

Three-Dimensional Integrated Circuits(3D IC)have brought many benefits, such as high-bandwidth, low-power,and small form-factor. Three-Dimensional(3D)integration based on Through-Silicon-Via(TSV)is rapidly adopted in industry. However, manufacturing processes for TSVs introduce new failure mechanisms. A defective TSV can fail the entire chip, this can severely increase the cost. Adding redundant TSVs to repair faulty ones is probably the most effective method to enhance yield, but it increases the cost of area. This paper presents a signal shift redundant TSVs scheme based on chain design, the input transfers signal by selecting signal TSVs from the next group. Based on probabilistic model, the proposed structure can achieve 99% yield, at the same time, it can reduce the number of redundant TSVs.

Three-Dimensional Integrated Circuits(3D IC); through-silicon-via; fault-tolerant

WANG Wei, ZHANG Huan, FANG Fang, et al. Redundant TSV scheme using signal shifting based on chain design.Computer Engineering and Applications, 2014, 50(17):34-39.

A

TP391.7

10.3778/j.issn.1002-8331.1310-0108

国家自然科学基金(No.61106037,No.61204046,No.61306049);国家高技术研究发展计划(863)(No.2012AA 011103);安徽省科技攻关项目资助(No.1206c0805039);中央高校基本科研业务费专项资金资助。

王伟(1979—),男,博士,副教授,研究领域为微系统、嵌入式系统、低功耗技术等;张欢(1988—),男,硕士,研究领域为三维集成电路容错技术、3D芯片结构与设计方法;方芳(1979—),女,博士,副教授,主要研究方向为NOC测试调度、低功耗测试技术;陈田(1974—),女,博士,副教授,主要研究方向为低功耗测试技术、测试数据压缩技术;刘军(1978—),男,博士,副教授,主要研究方向为内建自测试、测试数据压缩;汪秀敏(1984—),女,博士,讲师,主要研究方向为无线网络、网络编码、分布式存储。E-mail:happyzhang5023@163.com

2013-10-14

2014-01-16

1002-8331(2014)17-0034-06

CNKI网络优先出版:2014-03-12,http://www.cnki.net/kcms/doi/10.3778/j.issn.1002-8331.1310-0108.htm l