一种精确测量MOSFET晶圆导通电阻的方法

2014-03-22顾汉玉武乾文

顾汉玉,武乾文

(1. 华润赛美科微电子(深圳)有限公司,广东 深圳 518116;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

一种精确测量MOSFET晶圆导通电阻的方法

顾汉玉1,武乾文2

(1. 华润赛美科微电子(深圳)有限公司,广东 深圳 518116;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

导通电阻的准确测量是低导通电阻MOSFET晶圆测试中的一个难点。要实现毫欧级导通电阻的测试,必须用开尔文测试法;但实际的MOSFET晶圆表面只有两个电极(G、S),另外一个电极(D)在圆片的背面,通常只能将开尔文的短接点接在承载圆片的吸盘边缘,无法做到真正的开尔文连接,由于吸盘接触电阻无法补偿而且变化没有规律,导致导通电阻无法精确测量。介绍了一种借用临近管芯实现真正开尔文测试的方法,可以实现MOSFET晶圆毫欧级导通电阻准确稳定的测量。

MOS管;导通电阻;开尔文连接;自动测试设备;待测器件;晶圆测试;管芯

1 引言

MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)是金属-氧化层-半导体场效晶体管的简称,中文简称MOS管,是一种常见的半导体功率器件。随着半导体技术的不断进步,MOS管性能提升明显,应用日益广泛。电源控制和电源转换是MOS管大量使用的一个重要领域,在这类应用中,MOS管通常作为开关使用,导通电阻是最为关键的参数之一,直接影响到应用电路的稳定性;因此,导通电阻的准确测量成为MOS测试的重点。

2 低导通电阻MOS管简介

MOS管按照栅极的功能可分为增强型和耗尽型,按照沟道的材料类型可分为P沟道或N沟道,两种组合起来就有共四种类型,一般主要应用的为增强型NMOS管和增强型PMOS管。和传统的晶体管相比,MOS管具有开关速度快、输入阻抗高、安全工作区大、热稳定性好等优点[1]。MOS管的主要参数有:

V(BR)DS:漏源极击穿电压;

RDS(on):MOS导通时漏源之间的电阻;

RDS(on)@ID:漏极工作电流为ID时的漏源极导通电阻;

ID:最大漏极工作电流;

PD:最大漏极耗散功率。

半导体厂家设计了多种规格的MOS管满足各种不同的应用需求。漏源极击穿电压的范围从几伏到上千伏,最大漏极耗散功率从几瓦到几百瓦,导通电阻从几毫欧到数百欧,设计工程师可以选择合适的型号满足设计要求。

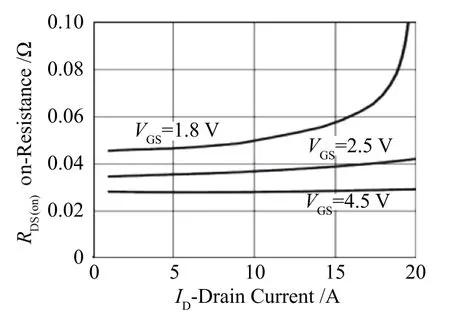

随着半导体工艺技术的不断发展,MOS管的性能不断提升,击穿电压越来越高,导通电阻越来越小,很多产品的导通电阻已经在毫欧的量级(我们称为低导通电阻MOS管),这对于产品应用非常有利,可以降低MOS管的功耗,实现更大的工作电流,也提高了电路的转换效率。8205是一款广泛用在锂电池保护电路中的NMOS管,其典型导通电阻为20 mΩ左右。图1 为RDS(on)和ID、VGS的变化关系。

图1 RDS(on)、ID、VGS关系

3 MOSFET晶圆测试

在MOSFET生产制造过程中,测试是保证其质量及剔除不良品的重要环节。测试通常由自动测试设备(Automatic Test Equipment,简称ATE)、探针台(PROBER)、负载板(LOADBOARD,也叫DUT板)等构成的系统来完成。典型MOSFET晶圆测试系统结构如图2所示。

图2 典型MOSFET晶圆测试系统

ATE是由测试单元和计算机组合而成的系统,拥有各种参数测试必须的资源,包括PMU(精密测量单元,Precision Measurement Unit)、DPS(器件供电单元,Device Power Supplies)、高速存储器(Pattern Memory)、向量生成器、继电器控制矩阵等。负载板(LOADBOARD)是把ATE资源信号转换为被测器件所需信号的电路模块;探针台(PROBER)的作用是承载圆片,通过机械装置的周期性动作,依次逐个将需要测试的管芯(简称 DIE)通过针卡(PROBERCARD)连接到测试回路中,并根据ATE测试的结果(PASS/FAIL),将数据记录在MAPPING文件中。

在后续的工序中,可以根据MAPING文件对相应的管芯用专用墨水进行标记(称为打INK),不良品会打上墨点,有墨点标记的芯片在封装工序会被舍弃(目前有不少封装厂家采用INKLESS工艺,封装设备直接根据探针台的MAPPING进行封装,省去打INK工序)。

4 开尔文(Kelvin)测试

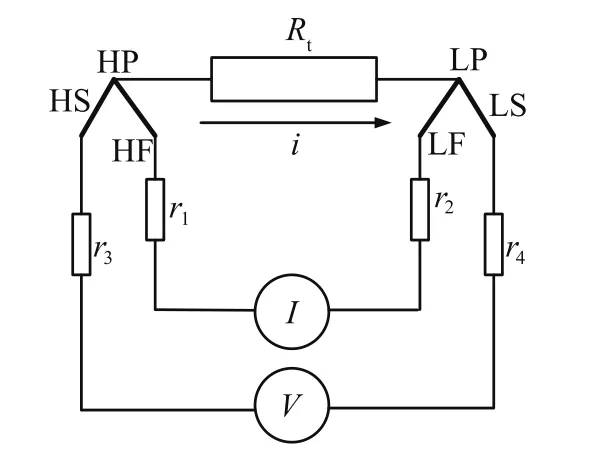

对于较小电阻的测量(数欧以下),需要采用开尔文测试(或称四线测试法),如图3所示。开尔文连接有两个要求:对于每个测试点都有一条激励线F和一条检测线S,二者严格分开,各自构成独立回路;同时要求S线必须接到一个有极高输入阻抗的测试回路上,使流过检测线S的电流极小,近似为零。图3中r表示引线电阻和探针与测试点的接触电阻之和。由于流过测试回路的电流为零,在r3、r4上的压降也为零,而激励电流i在r1、r2上的压降不影响i在被测电阻上的压降,所以电压表可以准确测出Rt两端的电压值,从而准确测量出Rt的阻值。测试结果和r无关,有效地减小了测量误差。按照作用和电位的高低,这四条线分别被称为高电位施加线(HF)、低电位施加线(LF)、高电位检测线(HS)和低电位检测线(LS)。

图3 开尔文测试法

在ATE设计中,PMU均采用了开尔文设计,即每个PMU的高电位端(H)、低电位端(L)都有Force和Sense线,图4是ATE开尔文测试电阻的标准接法,通过这种方式,可以准确测量毫欧级别甚至更小的电阻。

图4 ATE实现开尔文测试

5 传统低导通电阻MOSFET晶圆测试中的问题

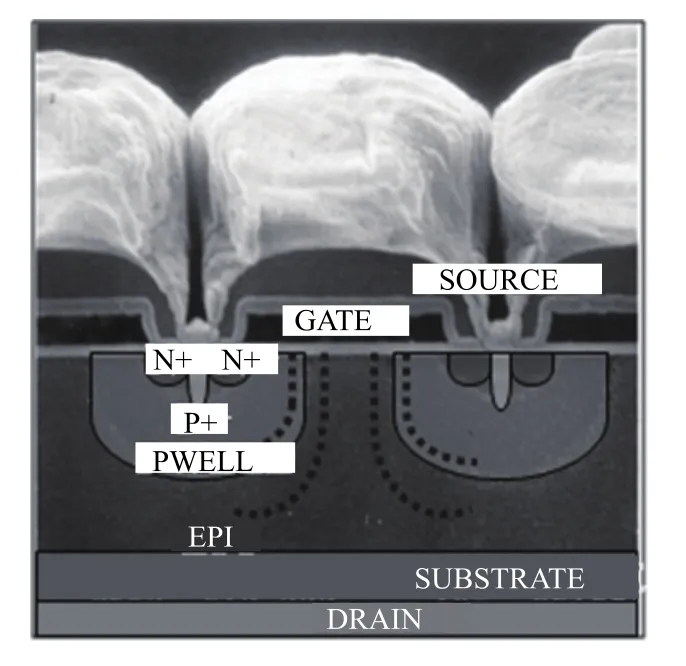

图5是MOSFET典型的纵向结构,源区(S)、栅区(G)通过金属连接,由表面的焊盘(称为PAD位,晶圆测试时作为探针卡的接触位,封装时为打线位)引出,而漏区(D)通过低电阻率的外延层连接到晶圆背面的金属层(用背面工艺制作的镀金或镀银层)。

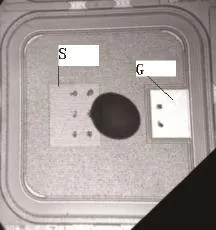

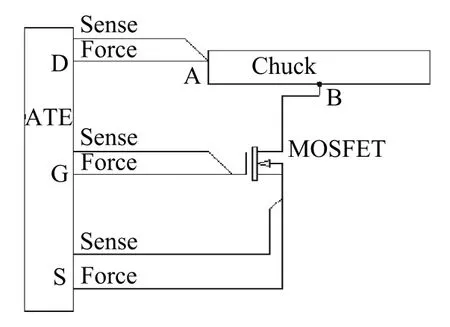

由于MOSFET的这种结构限制,实际晶圆表面只有G和S两个PAD位(参考图6),G端和S端可以同时扎2根探针,将Force、Sense接到PAD位;而D端在圆片的背面,由于测试时整个圆片吸附在探针台的吸盘(Chuck)上,只能将开尔文的双线连接到吸盘的边缘,无法实现真正的开尔文连接,等效示意图为图7。图中A、B两点之间的电阻会影响测试的结果,同时由于圆片背面的接触是随机变化的,AB间的电阻也是不确定的,测试的RDS(on)结果不仅偏大,而且不稳定。

图5 MOSFET纵向结构

图6 MOSFET 表面焊盘(PAD位)

图7 传统MOSFET晶圆测试等效图

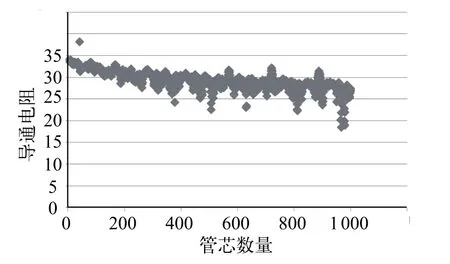

图8是传统方法测试的8205RDS(on)1 000个管芯数据的分布。测试的条件是ID=1.00 A,VGS=4.5 V。RDS(on)平均值是30.58 mΩ,STDEV值为2.140。

6 改进后的测试方案

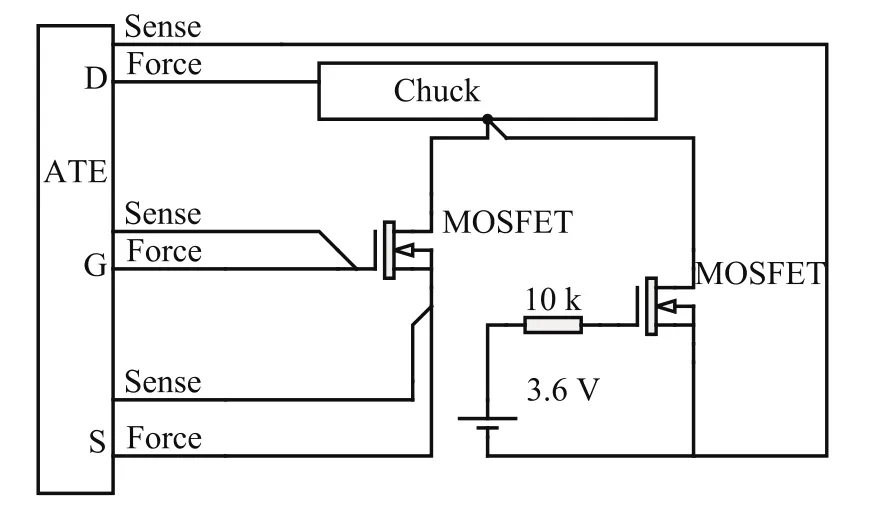

由MOSFET的工作原理可知,当VGS大于开启电压时,MOSFET处于导通状态,源漏(DS)之间的电阻变小。在MOSFET晶圆上,有大量共漏极的管芯存在,只要开启临近辅助管芯,利用DS回路,就可以构建Sense回路,实现真正的开尔文连接,从而实现RDS(on)稳定准确的测试,如图9所示。

图9中是以8205为例的,电池采用3.6 V一次性电池,开启后RDS(on)在数十毫欧,对于高阻抗的Sense回路,此电阻可以忽略不计。同时因为MOSFET是电压控制器件,栅极电流非常小,电池的使用寿命很长。

图8 传统方法测试的RDS(on)数据分布

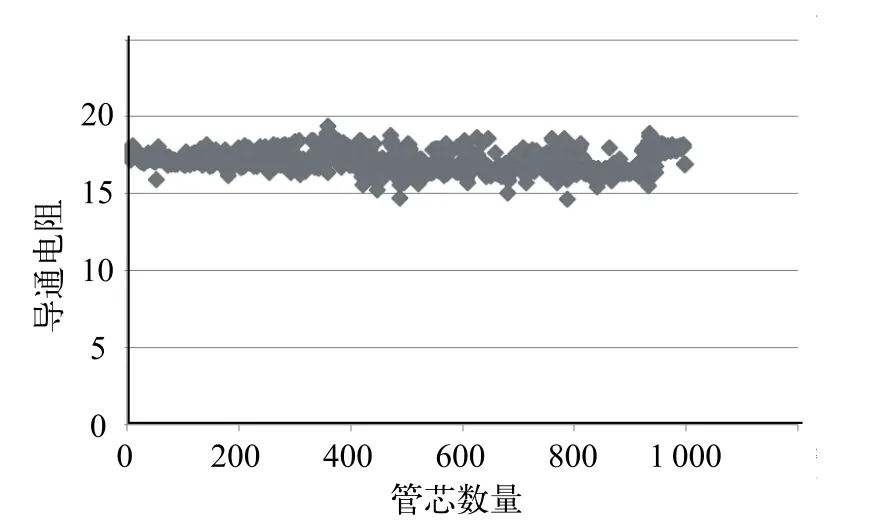

由于是真正的开尔文测试,测试非常稳定,而且数据准确。图10是用此方法测试的RDS(on)1 000个数据分布,测试条件与图8的相同。RDS(on)平均值是18.09 mΩ,STDEV值为0.197。与图8中的数据对比,RDS(on)显著减小,同时分布较为集中。

图9 改进后的MOSFET晶圆测试等效图

图10 补偿法测试的RDS(on)数据分布

测试的条件:ID=1.00 A,VGS=4.5 V。

RDS(on)平均值是18.09 mΩ,STDEV值为0.197。

为防止辅助管芯失效导致误判以及边缘管芯的误判,可以用左右两个辅助管芯并在一起做辅助测试。另外,在多管芯同时测试的方案中,可以直接借用临近管芯的测试探针实现开启功能,省去辅助探针。对于PMOS管,VGS需要变为反向电压。

7 结束语

在低导通电阻MOSFET晶圆测试中,针对传统测试方案无法准确测量毫欧级电阻的困难,本文提出了一种辅助管芯测试的方法,从原理上实现了真正的开尔文测试,对低导通电阻MOSFET的晶圆测试具有重要意义。

[1] 陆坤,等. 电子设计技术[M]. 成都:电子科技大学出版社,1997.

[2] Essentials of Electronic Testing for Digital, memory and Mixed-signal VLSI CIRCUITS [Z]. KLUWER ACADEMIC PUBLISHERS, Copyright 2002, New York, Boston.

[3] 顾汉玉,等. 低导通电阻MOSFET测试中的自动校验技术[J]. 微型机与应用,2013, 3.

[4] 王水平. MOSFET/IGBT驱动集成电路及应用[M]. 北京:人民邮电出版社,2009.

[5] 朱正涌. 半导体集成电路[M]. 北京:北京大学出版社,2001.

[6] NMOS管8205A数据手册[EB/OL]. http://www.ic5.cn/ p_CEG8205A_c90b.html.

[7] 赵英伟,庞克俭. Kelvin 四线连接电阻测试技术及应用[J]. 测试原理,2005,(11): 3-4.

[8] 北京华峰测控技术有限公司. ATE应用文集[P]. 2012.

A Skillful Technology for Low MOSFET RDS(on)Testing

GU Hanyu1, WU Qianwen2

(1.China Resources Semicon,Shenzhen518116,China; 2.China Electronics Technology Group Corpration No.58Research Institute,Wuxi214035,China)

It is diff i cult to measure lowRDS(on)of MOSFET exactly in wafer testing(CP). It is necessary to use Kelven connections for testing resistor whose resistance is lower than several milliohms. Actually, for MOSFET wafer, there are only 2 pads(G and S)which can be connected in Kelvin connections on the wafer surface. The third pole(D)is on the bottom of wafer, can only connect to edge of the chuck which hold the wafer in the course of CP, can’t achieve really Kelvin connections for MOSFET wafer testing in normal way. As the connect status for wafer and chuck is unstable, the testing result is unstable too. The paper presents a way to carry really Kelvin connections for MOSFET wafer testing by using a nearby DIE which is turned on. By this way,RDS(on)low than several milliohms can be measured exactly and stably.

MOSFET;RDS(on); kelvin connections; auto test equipment; device under test; circuit probing; DIE

TN307

A

1681-1070(2014)09-0017-04

顾汉玉(1968—),男,毕业于西安交通大学半导体物理与器件专业,高级工程师,长期从事半导体设备的升级改造、集成电路测试、ATE研制工作。

2014-04-11