高精度ADC测试技术研究

2014-03-22朱江

朱 江

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

高精度ADC测试技术研究

朱 江

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

随着高性能ADC器件的不断出现,传统的ADC器件测试评价方法已经越来越不适用于高性能ADC器件。为从工程上实现高性能ADC器件的测试评价,提供了一种高性能ADC器件关键参数评价的新算法,同时详细地分析新算法的原理并且论证了新算法的正确性。目前该算法已经大量地应用到高性能ADC器件的实际测试评价中去,解决了高性能ADC器件难以评价的问题。

高精度ADC;微分非线性;积分非线性

1 引言

随着数字信号处理技术和数字电路工作速度的不断提高,以及对系统灵敏度等要求的不断提高,很多系统中应用的ADC/DAC器件的性能指标也变得越来越高。当有效位数要求超过12位时即进入了高精度ADC/DAC的范畴,传统的测试方法已经渐渐不适用于这些高性能ADC/DAC器件的测试评价。因此研究高精度的ADC/DAC的测试原理和寻找新的测试方法就具有很重要的意义。本文重点介绍一种应用于高精度ADC参数测试的新算法。

2 ADC主要参数及测试原理介绍

从测试角度可以将ADC器件看作一个黑箱子,它仅有两种或三种外部的输入或输出:

(1)模拟信号输入部分:ADC器件的输入一般采用两种形式,即单端输入和差分输入,有些器件通过配置同时支持双端和单端应用。差分输入的抗干扰能力高于单端输入,双端应用的性能指标也优于单端应用。

(2)数字信号输出部分:也分为两种接口形式,串行输出和并行输出,大部份采用CMOS电平,但在数据传输速率很高时,为保证数据传输的可靠性,电路会采用并行LVDS差分模式来实现数据传输。目前在速度越来越高且简化接口的趋势下,已经有高速ADC/DAC电路采用高速串行差分模式进行数据传输。

(3)控制部分:ADC器件的控制部分主要包括模式选择、待机、内外基准选择等,功能复杂的ADC采用SPI等串行总线配置寄存器对电路进行控制。

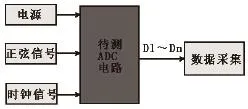

图1 ADC接口示意图

ADC的测试主要是围绕着这些接口进行测试分析。ADC的直流参数测试部分主要包括电压基准、工作和待机电流、输入输出电平、积分非线性、微分非线性、增益误差、零点误差等。ADC的交流参数测试部分主要包括输出数字信号的总谐波失真度、有效位数、信噪声失真比、无失真动态范围、信噪比、互调失真等。ADC的时间参数测试部分主要包括通讯接口时序、转换时序和转换建立时间等。本篇论文的主要内容是介绍一种用于高精度ADC器件直流参数测试的新算法,同时讨论一下在ADC器件交流参数测试中会出现的问题、原因和解决办法。

2.1 直流参数

2.1.1 积分非线性(INL)

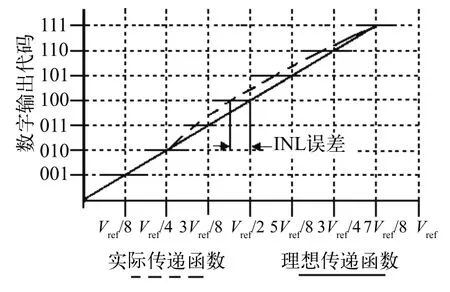

积分非线性表示了ADC器件在所有的数值点上对应的模拟值和真实值之间误差最大的那一点的误差值,也就是输出数值偏离线性最大的距离。单位是LSB。图2直观地给出了参数的定义。

图2 INL示意图

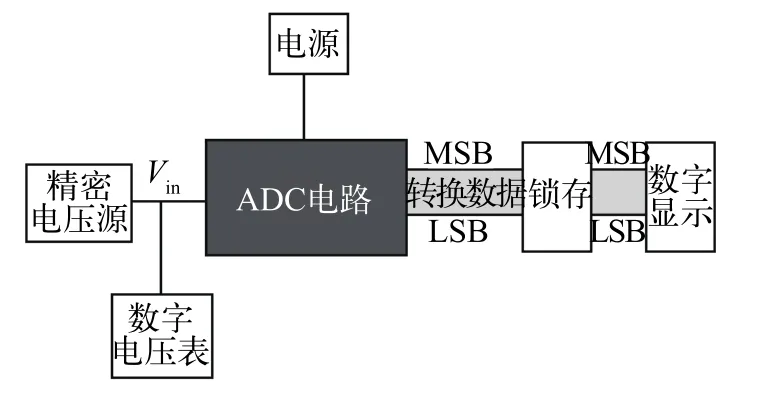

这项参数的测试原理框图如图3所示。

图3 DC测试原理图

理论测试方法简介如下:

(1)将待测ADC电路接入测试系统;

(2)调节输入端电压,由J码变为J-1码,记下输入电压V1;再调节输入电压使J-1码变为J码,记下输入电压V2;同理J码变为J+1码再由J+1码变为J码分别记录V3、V4,J码的实际码宽中心值Vja=(V1+V2+V3+V4)/4,分别测试所有码的实际码中心值;

(3)根据(2)的数据选用合适的数学方法确定最佳拟合直线,得到第J码的模拟输入量Vjc;

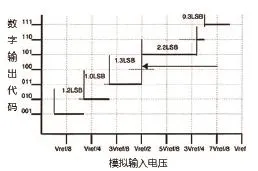

(4)由(2)项和(3)项的数据相比较,取其偏差的绝对最大值dVmax,由式(1)计算出EL:

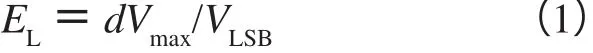

2.1.2 微分非线性(DNL)

理论上说,模数器件相邻两个数据之间,模拟量的差值都是一样的。就好比疏密均匀的尺子。但实际上,相邻两刻度之间的间距不可能都是相等的。所以,ADC相邻两刻度之间最大的差异就叫微分非线性DNL,也称为差分非线性。图4很直观地给出了这项参数的含义。

图4 DNL示意图

这项参数的测试原理图同INL的测试原理图。

测试原理简介如下:

(1)首先用上面项目中所测得的V1、V2、V3、V4按照公式[(V3+V4)/2]-[(V1+V2)/2]算出所有码的实际码宽;

(2)将(1)项的数据和理想1VLSB比较,取其偏差绝对值的最大值dVmax;由式(2)计算出EDL:

2.2 交流参数

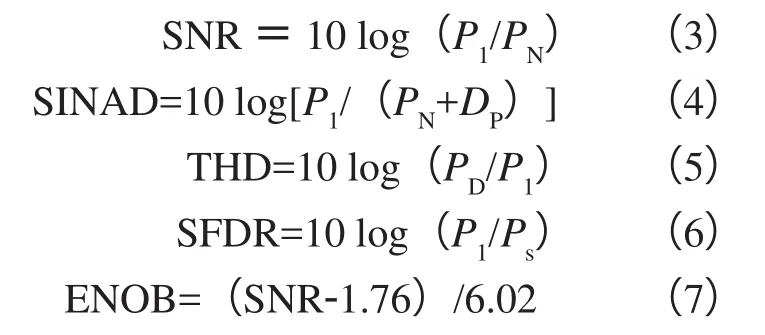

交流参数测试关注的是器件的传输和性能特征,即采样和重现时序变化信号的能力,ADC电路的主要交流参数主要有信噪比(SNR)、信噪声失真比(SINAD)、总谐波失真(THD)、有效位数(ENOB)、无失真动态范围(SFDR),下面是这些项目的具体定义。

信噪比:信号分量功率与噪声分量功率之比;

信噪声失真比:信号分量与噪声功率及谐波分量功率和之比;

总谐波失真:谐波分量功率与信号分量功率之比;

无失真动态范围:信号分量功率与最大杂波分量功率之比;

有效位:是一种折算关系,按理想ADC的信噪比与位数的关系式SNR=6.02N+1.76推算而得到的。交流参数的测试原理框图如图5所示。

图5 交流测试原理图

理论测试方法简介如下:

(1)电源施加合适的电源电压,输出端接规定的负载电阻;

(2)信号源施加规定幅度和频率fs的模拟信号;

(3)施加规定频率fCLK的采样时钟;

(4)待ADC工作稳定后,采集合适数量的ADC输出转换数据;

(5)对采集的数据进行FFT运算,得到ADC转化后的数据功率谱,分别按定义计算出基波信号分量P1,谐波信号分量PD,噪声功率PN,最大杂波分量功率Ps。

由下列公式计算出:

3 关键参数实际测试方法及原理

3.1 直流参数

直流参数说明了静止的模拟信号转换成数字信号的情况,主要关注具体电平与相应数字代码之间的关系。当随着ADC的精度增加即转换位数的增加,会使每个台阶的量化电平(1 LSB)也变小,例如满幅度4.096 V的ADC电路:假设电路是12 bit精度,那么它的最小量化台阶就是1 mV;如果是16位精度的ADC电路,那么它的最小量化台阶就会降至0.062 5 mV。首先测试中采用精度满足要求的模拟电压源成本会比较高,其次由于系统噪声的存在,一个台阶的输入电压变化很容易被噪声淹没。所以上述测试方法只适合位数比较低的ADC电路测试,而不适合高精度ADC电路的测试评价。要对高精度ADC的直流参数进行正确测试和评价,需要考虑采用其他方法,下面就介绍一种已经实际应用的测试方法。

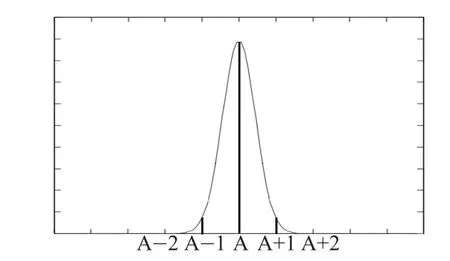

在描述新的测试算法前,需要先分析在实际测试环境中的噪声情况,一个良好稳定的测试环境中所存在的噪声在频谱上的表现就会和白噪声的频谱类似。在这种环境下,如果对同一个电平用待测ADC电路(每个码宽均相同的理想ADC电路)转换测试多次,那么它的测试值就会表现为主要集中在其对应值上,同时有少部分值会偏差到其相邻两边。分布示意图如图6。

图6 测试值分布图

Y轴坐标表示测到的次数,X轴坐标表示测到的码值。当转换次数足够多时,这些点的分布在概率上表现就是满足正态分布,期望值就是电平所对应的码值。标准差和系统噪声、电路的量化台阶密切相关,标准差和噪声成正比,和量化台阶成反比。

为更好地解释新的测试算法的原理,首先简化这种转换数据的分布模型到三个点,就是对某个电平做N次理想的AD转换,结果有三种:

数据A:N-a次;

数据B:a/2次;

数据C:a/2次。(B和C的数字码值比A分别大1或小1)

如果将ADC的输入电平在时间轴上做一个从最小值到最大值按台阶缓慢均匀的拉偏,并对每个模拟输入电压用这只理想ADC电路做N次AD转换。考虑到测试过程中环境未发生变化,所以每个点受噪声影响的情况也都基本相同,那么每个点的测试结果都会符合上面的简化模型。最后对得到的所有数据按数字码值进行次数统计,就会得到一个数列:

n1, n2…nk(k=2M-1,M是ADC电路的位宽)

观察这个数列就会发现:n1, n2…nk每个值都相等,都等于N。这说明每个电平所对应编码的码宽都相同,那么EL=0,EDL=0;

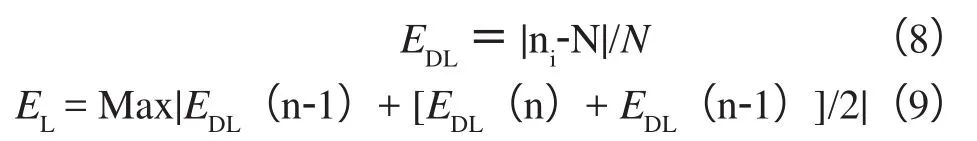

实际上AD器件的转换曲线不会是理想的,那么ni的数值表现在N上下抖动,选取|ni-N|最大值的那个点,那么:

观察数列nk,如果出现某个或某些n值为0,那么就意味着这块电路存在了一定的误码。

如果测试环境存在周期性干扰,就需要改造测试方法,将每个点的采样时间拉长到周期性干扰的整数倍,这样测下来的结果也能够真实地反映电路INL、DNL指标情况。

3.2 交流参数

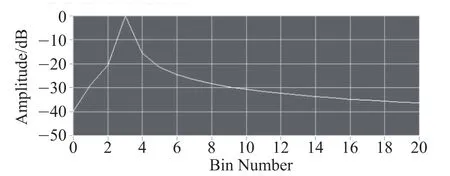

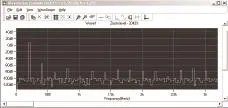

ADC器件的交流参数主要包括SFDR、THD、SNR等,这些参数的共同点是都需要对转换后的数据进行频谱分析,所以得到真实的频谱是交流测试的重点。如果在实际的交流测试中,输入信号频率、周期数、采样点数、采样频率选择得不合适,就会出现如图7所示的现象。

图7 存在能量泄漏的频谱

在这种频谱上进行AC参数计算是错误的,得到的AC参数数据也是不真实的。导致这种现象的原因是采样数据个数有误:没有对信号采集整数周期,导致信号的频谱泄漏。为防止发生以上现象,需要对输入信号频率ft、输入信号的周期数M、采样点数N、采样频率fs做出规定,它们必须满足以下公式:

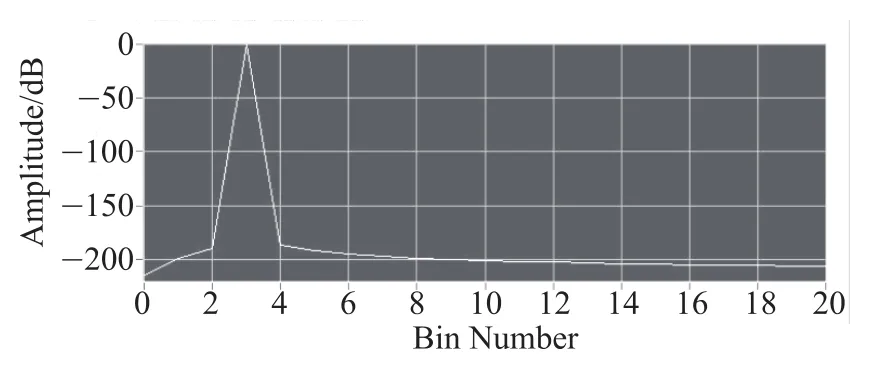

fs/N =ft/M (10)

当所选择的输入信号频率、周期数、采样点数和采样频率满足上述关系后,就能够保证采集的数据点数正好是整数个输入信号周期,这样采集到的数据在频谱上就会表现为信号的能量非常集中,具体的频谱表现如图8所示。

图8 无能量泄漏的频谱

在这个频谱的基础上进行运算,这样得到的AC参数就能真实反映待测ADC电路的性能。

4 实际测试曲线介绍及分析

实际测试的INL和DNL测试曲线如图9所示。

图9 实际INL、DNL测试曲线

图9中示例为一款12 bit ADC,看INL图,INL曲线表现得很像一个锯齿波,这正是ADC电路采用分段数模转换的结果,在段和段的接缝上总是INL变化最大的地方。分析图中数据,我们不难看出电路的INL指标在5~6 LSB,DNL指标小于1 LSB。

实际测试的交流曲线和频谱见图10和图11。

图10 时域测试曲线

图11 频域测试曲线

从时域图中我们可以看到:正好采集了整数个周期的输入信号,这反映到频域上就表现为每根谱线能量非常集中。此电路最终的测试结果为:SNR=79.6 dB

5 结束语

长期以来高性能ADC器件主要依靠国外进口。随着国内科研院所技术水平的不断提升,很多高性能ADC器件已经完成了国产化,更多的高性能ADC器件正在研发。而如何准确评价这些高性能ADC器件就成为了测试的难题。本文所讨论的ADC参数测试的新算法就是为解决这个难题而开发出来的,这种算法为高性能ADC器件关键参数的测试评价提供了一个实现方便、成本低廉、开发简单的解决途径。目前该算法已经成熟,并且在工程上已经形成了一整套ADC电路测试的技术解决方案。通过这个方案的应用已经解决了JAD9268、JAD73311、AD1851的量产测试。

[1] Teradyne Technology, In, UltraFLEX User Manuals [Z].

[2] 理查德·G·莱昂斯. 精简数字信号处理[Z].

[3] Neamen D A. 电子电路分析与设计[Z].

Research on Testing Technology of High Quality ADC

ZHU Jiang

(China Electronics Technology Group Corporation No.58Research Institute,Wuxi214035,China)

With the emergence of high quality ADC, the traditional technology of testing isn’t fit for the new ADC. In order to evaluate high quality ADC, the paper focuses on a new technology for new ADC’s test. In the paper the new technology is described and proved clearly. The conception and technology of ADC testing and the source of ultraf l ex system are described. Now the technology has been used in actual high quality ADC’s test.

high quality ADC; INL; DNL

TN307

A

1681-1070(2014)09-0009-04

2014-06-11