表面贴装集成电路引脚整形研究

2014-03-22杨城,邓勇

杨 城,邓 勇

(湖北航天计量测试技术研究所,湖北 孝感 432100)

表面贴装集成电路引脚整形研究

杨 城,邓 勇

(湖北航天计量测试技术研究所,湖北 孝感 432100)

微电子技术的迅猛发展,促进了电子器件和电子产品小型化的发展。目前,表面贴装集成电路(SMIC)已成为主流封装形式,此类封装集成电路具有集成度高、管脚多、间距小等特点,在生产上满足了向小型化发展的需求,但是也带来了很多问题,其中引脚共面性问题为常见的问题之一。结合SMIC在使用过程中因引脚共面性引起的焊接问题,对SMIC的引脚整形试验展开研究。

表面贴装集成电路;共面性;整形

1 引言

随着电子元器件向小型化、复合化、轻量化、多功能、高可靠、长寿命的方向变革,相继出现了各种类型的表面贴装集成电路(SMIC),此类封装集成电路具有集成度高、管脚多、间距小等特点,生产上满足了向小型化发展的需求,但是也带来了很多问题,其中引脚共面性问题为常见的问题之一。

据统计,表面贴装技术(SMT)中出现的焊点开路故障,达总故障数的三分之一以上。其中,引脚的共面性差是引起故障的最主要原因之一。为提高焊接过程中的可靠性,湖北航天计量测试技术研究所通过对引脚有问题的表贴集成电路进行整形,并通过共面性检测,减少因共面性差而造成的焊接故障,降低生产成本,提高生产质量和效率。

2 引脚整形设备应用背景

微电子技术的迅猛发展,促进了电子器件和电子产品的小型化发展。电子产品的高密度组装使得传统的通孔安装技术THT无能为力。SMT则较好地解决了电子产品发展的组装需求。SMT是指采用拾放机直接粘贴到印刷电路板(PCB)上,通过焊接成为一个电子部件的装配技术。SMT相对于THT,其优点有:

(1)组装密度高、电子产品体积小、重量轻,与通孔插装技术相比,SMT节省PCB空间60%~70%,使重量减轻70%~80%;

(2)可靠性高,抗振能力强;

(3)高频特性好;

(4)易于实现自动化,提高生产效率;

(5)可以降低成本。

正是由于SMT的这些优势,SMIC的发展在近几年非常迅猛,原有的双列直插封装集成电路(DIP),许多已被适合SMT组装用的小外形封装集成电路(SOP)所代替。近年来出现的超大规模集成电路(VLSIC)和专用集成电路(ASIC),其引脚数的增多使得SOP已满足不了设计需要,因而出现了大量采用四面出线扁平封装的集成电路,如塑料封装J型引脚的集成电路PLCC 和陶瓷无引脚的集成电路(LCCC)以及方形扁平封装集成电路QFP。根据封装技术和组装形态的不同,同种封装尺寸下芯片的引脚数有所不同,从而导致了各种不同封装集成电路引脚中心间距的差异。而且,随着半导体技术的不断发展,IC集成度越来越高,芯片也不断增大,相应I/O数的增加也异常惊人,在对其封装时,在其限度内就必须不断减小引脚的间距。对于QFP来说,引脚间距越来越小,从通常的0.635 mm到0.5 mm,甚至0.3 mm[1]。图1为典型的表贴集成电路封装形式。

图1 典型的表贴集成电路封装形式

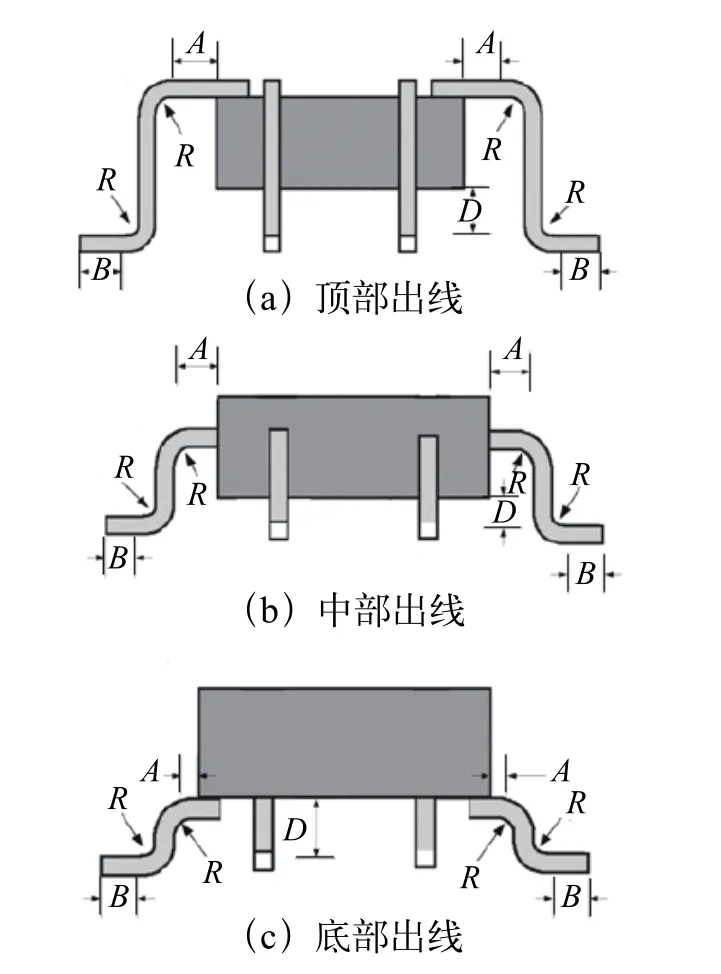

精细间距集成电路的局限性在于细引脚易弯曲、质脆而易断,对于引脚间的共面性和贴装精度的要求很高。因此要实现精确安装就要求引脚具有很高的精度。以QFP封装集成电路为例,除特殊情况外,其引脚有如图2所示的三种出线方式,分别为顶部出线方式、中部出线方式及底部出线方式。

图2 QFP封装集成电路引脚的出线方式及关键参数

在引脚参数中,有如下几个关键技术参数[2]:

(1)肩宽(A):即引脚根部到第一个弯曲点的距离,如图2所示,成形过程中器件两边肩宽应基本保持一致,引脚不得在器件本体根部弯曲,器件本体到引脚弯曲点间平直部分距离为A。

(2)焊接面长度(B):即引脚切割点到第二个引脚弯曲点的距离,如图2所示;

(3)站高(D):即成形后元器件本体与安装面间的距离,如图2所示。在元器件引脚成形过程中,提供一定尺寸的站高是非常必要的,其主要原因也是考虑到应力释放的问题,避免元器件本体与PCB表面间形成硬接触后造成应力无释放空间,进而损伤器件。另一方面,在三防和灌封过程中,三防漆及灌封胶能够有效浸入芯片本体底部,固化后将有效提高芯片对PCB的附着强度,增强抗振效果。

(4)引脚弯曲半径(R):如图2所示,为了保证集成电路引脚成形后,其引脚焊接面具有良好的共面度(不大于0.1 mm),由于成形过程中,器件引脚存在反弹,不同材料和不同引脚厚度(直径)的反弹系数存在一定的差别,因此引脚成形过程中应控制好引脚弯曲半径,确保成形后引脚焊接面共面度良好。

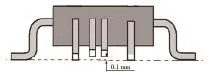

(5)引脚共面性:共面性是最低落脚平面与最高引脚之间的垂直距离,如图3所示。共面性是集成电路引脚成形的一个重要参数,共面性差是造成集成电路与PCB板焊点开路故障的主要原因。

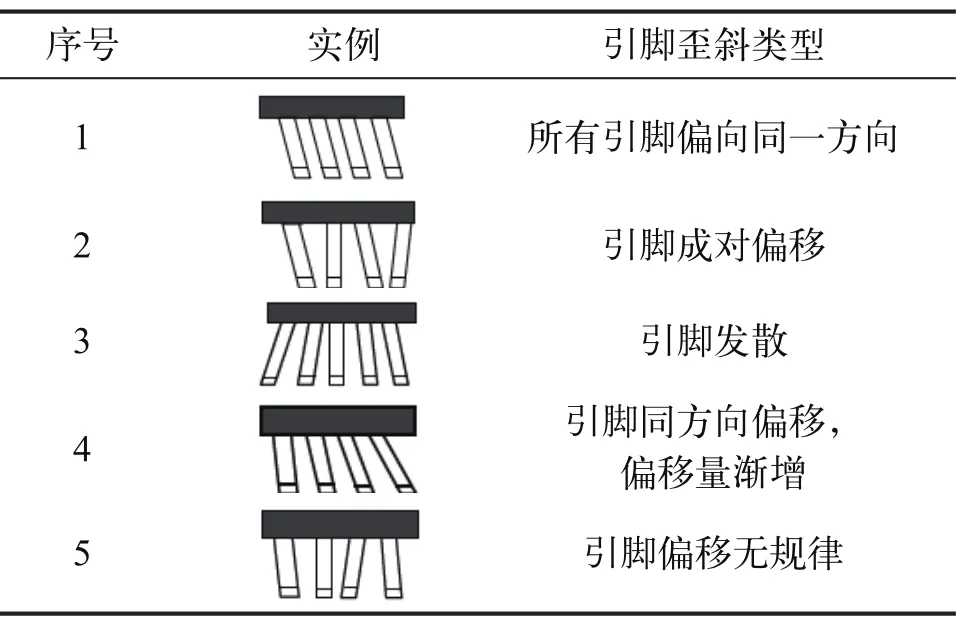

(6)引脚歪斜:引脚歪斜是指相对于封装的中心线测量,其成形的引脚从其理论位置的偏移。通常情况下可通过外观进行定性判断,其主要方法是将成形后的集成电路放置于待焊接的PCB焊盘上,观察引脚与PCB焊盘的相对位置,应保证最大侧面偏移不得超过引脚宽度的25%,如图4所示。

图3 引脚共面性定义

图4 集成电路引脚最大侧面偏移

引脚歪斜的不同类型见表1。

表1 引脚歪斜的不同类型

在实际生产中,因引脚共面性及引脚歪斜问题造成的集成电路引脚接触不良或焊接不良,几乎占总故障数的80%。

3 应用QFP-208封装形式遇到的问题及解决方案

3.1 问题介绍

某厂在使用Silicon SculptorⅡ编译器对Actel公司生产的A42MX24PQ208M进行程序编译及写入的过程中发现该器件空检查错误,无法对其进行程序编译及写入。

该厂将该器件委托湖北航天计量测试技术研究所进行试验,分析上述现象产生的原因。使用SP-3160V 超大规模集成电路测试系统对其进行了连通性测试,测试数据显示第93、94、95、96、97、103、104、121、125等引脚接触不良。

对该器件进行外部目检,发现部分引脚歪斜、翘曲,引脚损伤外部目检图见图5,与连通性测试接触不良的引脚位置基本对应。

图5 引脚损伤外部目检图

3.2 制定解决方案

通过对该厂提供的器件进行连通性检查及外部目检试验,初步判断编程失败的原因为器件的引脚歪斜、翘曲造成接触不良,歪斜、翘曲的引脚在空检查步骤不能接收和反馈信号。

解决方案:

(1)使用FP-50引脚整形设备对该器件整形;

(2)将整形后的器件进行外部目检和连通性检查试验;

(3)再次对检查合格的器件进行程序编译及写入;

(4)根据编程结果确定下一步试验方案或下结论。

4 FP-50引脚整形设备介绍

4.1 FP-50引脚整形设备简介

FP-50引脚整形设备被设计用于各种表面贴装集成电路(如QFP、TQFP、SSOP、TSOP等)的返修工作。该设备引脚整形装置为模块化设计,主要由集成电路支撑架与引脚返修工装两部分组成:集成电路支撑架用于整形过程中固定集成电路;引脚返修工装用于引脚的整形。图6为FP-50引脚整形设备。

通过FP-50引脚整形设备的整形,可对表面贴装集成电路引脚的以下参数进行整形,达到设计方或使用方所要求的尺寸:

(1)引脚歪斜(Lead Bend);

(2)引脚共面性(Coplanarity);

(3)引脚终端尺寸(Terminal Dimension);

(4)引脚间距(Pitch)。

图6 FP-50引脚整形设备

4.2 FP-50引脚整形设备整形原理

首先通过支柱与压块固定集成电路,然后通过Comb(梳子)与Coplan的一系列协同动作对引脚进行整形,最后支柱旋转,对表面贴装集成电路的其余各边进行整形。

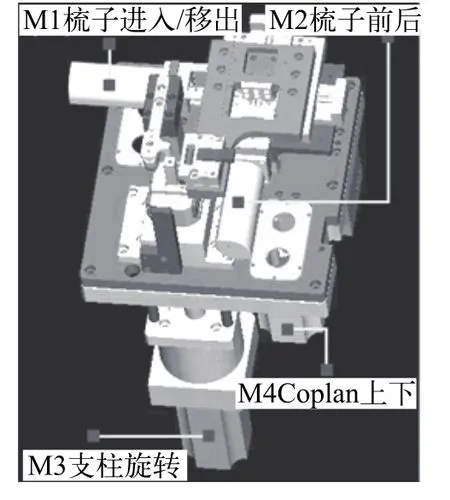

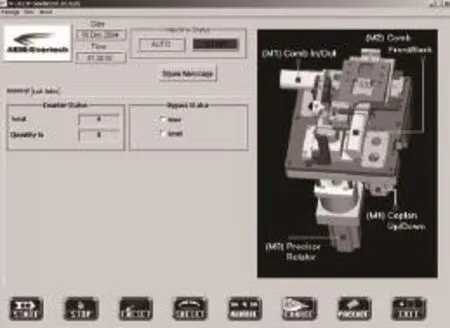

FP-50引脚整形设备整形模块由四个马达控制,图7为FP-50引脚整形设备整形模块。

图7 FP-50引脚整形设备整形模块

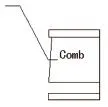

(1)M1为控制梳子进入/移出集成电路引脚的控制马达,其作用为控制梳子插入到引脚间距中,如图8所示,并对引脚终端尺寸进行整形校正;

图8 梳子插入引脚

(2)M2为控制梳子前后动作的控制马达,其作用为对弯曲的引脚及引脚的间距进行整形校正;

(3)M3为控制支柱旋转的控制马达,其作用为控制集成电路各边引脚均进行整形试验;

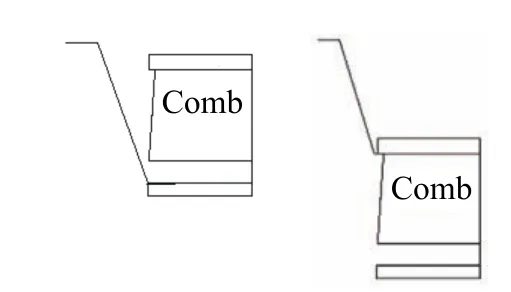

(4)M4为控制Coplan上下动作的控制马达,其作用为对引脚共面性进行整形校正,如图9所示。

图9 Coplan上下动作

5 解决方案实施情况与结论

5.1 解决方案实施情况

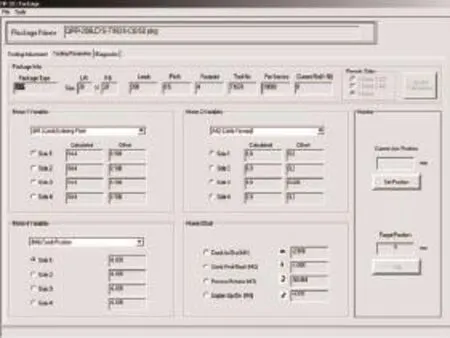

在FP-50引脚整形设备上开发调试A42MX24PQ208M型号集成电路整形程序,图10为程序调校过程。

图10 程序调校过程

程序调校结束后,进入引脚整形界面对该集成电路进行引脚整形,图11为FP-50引脚整形设备整形界面。

图11 FP-50引脚整形设备整形界面

将通过FP-50引脚整形设备整形校正后的集成电路进行外部目检和连通性检查试验,外部目检无明显的引脚歪斜、翘曲情况,图12为整形后外部目检图。

外部目检后对该器件进行连通性检测,测试合格。

将整形后的器件送回该厂再次进行程序编译及写入,编程成功。

5.2 结论

整形后的器件再次进行程序编译及写入时编程成功,证明第一次编程失败的原因是由引脚歪斜、翘曲造成引脚接触不良而引起的,而非器件的失效;FP-50引脚整形设备的整形效果良好;本次分析方案明确,结论准确,达到了预期目的。

The Study of Reforming Pins for Surface Mount Integrated Circuit

YANG Cheng, DENG Yong

(Hubei Aerospace Institute of Measurement and Test Technology,Xiaogan432100,China)

With the rapid development of microelectronics technology, electronic devices and electronic products are becoming more and more miniaturized. Currently, surface mount integrated circuit(SMIC)has become a mainstream form of encapsulation, such packaged integrated circuit are highly integrated with multi-pins and fi ne pitch. This encapsulation form meet the miniaturization development needs for users, but it also brings a lot of problems, such as lead coplanarity issue. In consideration of the problem of coplanarity, there is a study for reforming the pins of SMIC with the purpose of improving the reliability of solderability is needed.

SMIC; coplanarity; reforming

TN305.94

A

1681-1070(2014)09-0005-04

2014-04-11