基于三模冗余结构的自刷新寄存器设计

2014-03-22陈钟鹏邹巧云施斌友万书芹

陈钟鹏,邹巧云,施斌友,万书芹

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于三模冗余结构的自刷新寄存器设计

陈钟鹏,邹巧云,施斌友,万书芹

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

设计了一种带自刷新功能的寄存器,该寄存器采用两级数据锁存结构,在第二级锁存结构中设计了一个选择电路。该选择电路采用三选二机制,用于三模冗余结构中取代常用寄存器,选择数据来自三模冗余结构的三路输出。有两路值相同,输出结果为该值,用于修正寄存器的输出值。在0.13 μm工艺条件下用此结构设计的寄存器,面积为32.4 μm×8.4 μm,动态功耗0.072 μW·MHz-1,建立时间0.1 ns,保持时间0.08 ns。该结构用于三模冗余结构中,可有效防止单粒子翻转效应(Single Event Upset, SEU)的发生。测试结果表明采用该结构的寄存器组成的存储单元三模冗余加固结构,在时钟频率1 GHz时,单粒子翻转错误率小于10-5。

单粒子效应;寄存器;辐照效应;辐照加固

1 引言

随着航天技术的发展,越来越多的电子设备被应用于各种航天系统,进入太空中。由太阳活动、宇宙射线等产生的大量电子、质子和高能粒子组成了复杂的空间辐射环境,这些组成航天系统的电子设备长期处于这种带电粒子的辐射环境中,当空间中的单粒子与电子系统中的半导体器件相互碰撞并发生作用时,就产生了辐射效应。辐射效应可分为两大类:总剂量效应(Total Ionizing Dose, TID)和单粒子效应(Single Event Effect, SEE)。

随着半导体技术的飞速发展,器件的特征尺寸不断减小,栅氧化层的厚度逐渐减小,根据总剂量效应产生的原理,当栅氧化层厚度小于10 nm时,TID效应微乎其微[1]。随着尺寸的减小,工作电压越来越小,临界电荷也越来越小,越易于发生单粒子效应[2]。

SEE根据辐射机理和辐射影响结果的不同,可分为硬错误和软错误。硬错误的研究主要集中在工艺器件级,软错误的研究主要集中在电路设计领域。存储单元是SEE发生频率最高的电路结构。SEE产生的软错误由单粒子翻转(Single-Event Effect, SEU)主导引起。SEU成了影响集成电路可靠性的主要原因之一。

SEE加固技术伴随SEE理论体系的研究和深入,取得了较大的进展,目前有多种能够提高电路抗辐射性能的技术方案,其中应用比较广泛的有电阻加固技术、三模冗余加固技术、基于DICE结构的加固技术、纠错码编码加固技术等[3]。三模冗余(Triple Module Redundancy,TMR)加固技术以其复杂度低、难度低、成熟度高、可实现性高、应用面广等优点得到了更为广泛的应用。很多芯片需要长时间在寄存器中保存初始的配置字,三模冗余是对SEU进行加固的一种有效方法。

传统的TMR加固技术,在时序电路的加固是将一个寄存器复制成三份,采取三选二的表决方式,任意一路寄存器受到重粒子轰击发生翻转,另外两路寄存器输出正常时电路工作正常;但长时间暴露在辐照环境中另外两路寄存器同样存在受到重粒子轰击发生翻转的概率,累积两次翻转即可导致电路失效。本文针对这种情况设计了一种基于三模冗余结构的自刷新寄存器,避免因为累积翻转引起的电路失效。

2 三模冗余结构抗单粒子能力分析

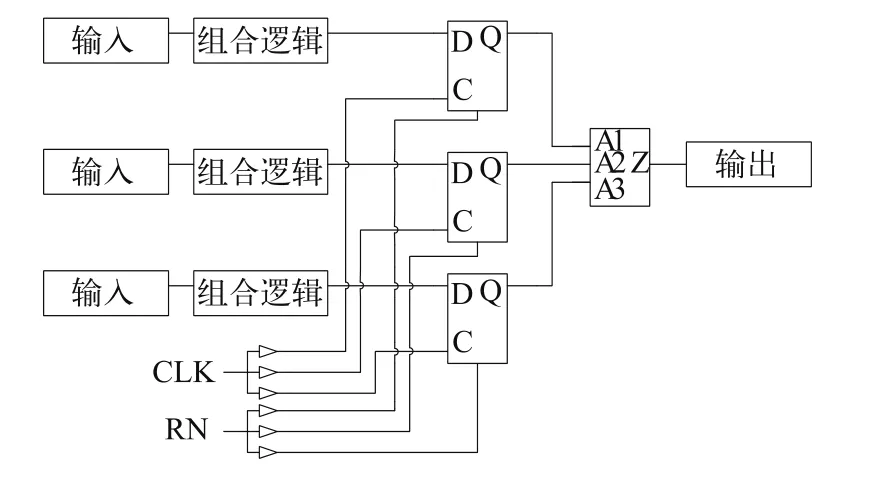

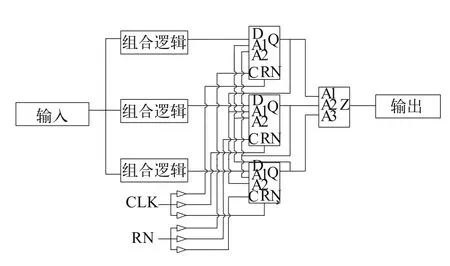

TMR加固技术的原理如图1所示,将一个工作模块复制三份,后面加入表决电路,由三个相同的工作模块中寄存器的值输出时,表决器对三个输出结果进行比较判决,表决器的表决原则是三取二,即输出数据中有两个或两个以上数据相同时,则选择此相同值作为TMR结构的最后输出。

图1 传统TMR加固电路结构

TMR电路加固技术设计思想的前提是任意两个存储单元的同一位不会在同一时间内发生SEU效应。如果其中一个存储单元发生翻转,另两个工作正常的电路可以将错误屏蔽并得到正确的结果,使整体电路工作正常,从而消除单个模块故障。传统的TMR设计将出错概率从一个独立事件转变成两个独立事件同时发生的概率,风险显著降低,提高了电路的抗单粒子特性。

对于长期处于带电粒子辐射环境中的航天系统,有些功能配置需要保持较长时间,因此需要长时间在寄存器中保存初始的配置字。如果其中任意一个寄存器受到重粒子的轰击发生了翻转,根据TMR机制,电路仍可保持正常工作。但长期暴露于辐射环境中,另外两路寄存器的翻转概率为两个独立事件,概率远大于两个独立事件同时发生的概率,一旦其中之一发生了翻转,则三路数据中出现了两组错误的数据,最终输出为错误,其结果可能导致严重的失误。

3 自刷新寄存器设计

本文针对以上情况,克服现有技术中的不足,提出了一种基于三模冗余加固技术具有自刷新功能的寄存器结构,避免长期工作在辐照环境下,由辐射累积导致两路寄存器发生翻转的问题。

3.1 自刷新寄存器结构

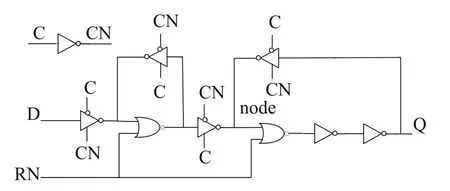

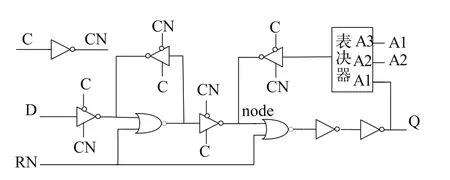

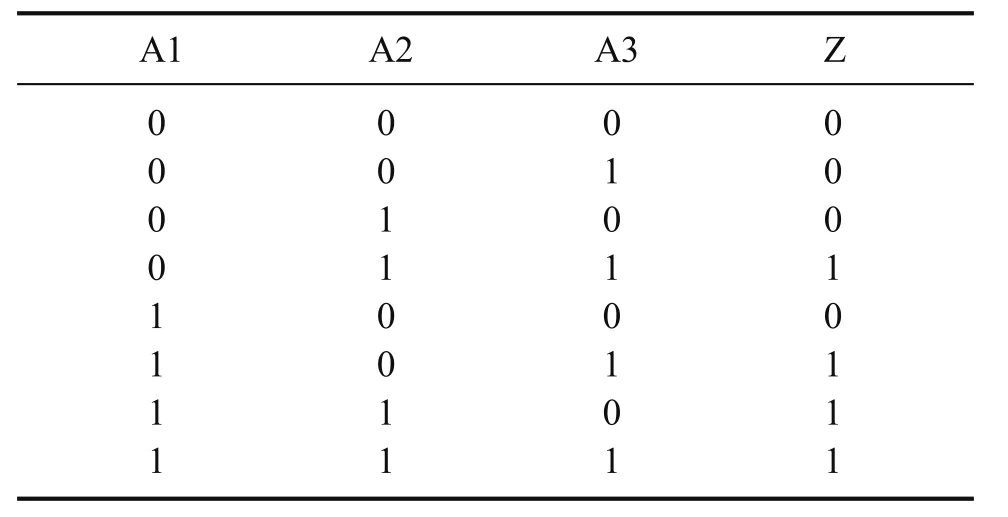

常规寄存器的原理如图2所示,电路结构中分为前后两级锁存电路,前一级锁存电路,当C为低电平时,电路导通,数据D进入锁存状态,此时后级电路关闭;后一级锁存电路,C为高电平时,电路导通,数据D从前一级进入后一级锁存状态,并从Q端输出,此时前级电路关闭。如果节点 node发生了一次翻转,在有新的数据写入之前,电路始终输出的都是一个错误的值。带自刷新功能的寄存器如图3所示,此寄存器结构与图2不同的是,在寄存器的后一级锁存中增加了一路选择器。选择器的工作原理是输入三个值A1、A2、A3,选择器的输出采取三选二的选择方式,即A1=A2!=A3,输出A1;A1=A3!=A2,输出A1;A2=A3!=A1,输出A2;见表1,内部表决器真值表。在该结构中电路的输出值由A1、A2、A3的值来确定。

在版图设计上,采用保护环设计进行总剂量辐射和单粒子闩锁的加固设计,同时采用优化器件尺寸,如增加场氧尺寸等进行组合逻辑单元的单粒子翻转加固设计[4]。图4是自刷新寄存器的版图设计,在0.13 μm工艺下,面积为32.4 μm×8.4 μm,动态功耗为0.072 μW·MHz-1,建立时间0.1 ns,保持时间0.08 ns。

图2 常规寄存器原理图

图3 自刷新寄存器原理图

表1 自刷新寄存器内部表决器真值表

图4 自刷新寄存器版图

3.2 采用自刷新寄存器的TMR

采用自刷新寄存器的TMR如图5所示,A2、A3是三模冗余结构中另两路的输出Q2、Q3。如果节点node翻转,Q1输出错误,由三模冗余加固设计的原理可知,此后电路仍正常工作。同时,由电路中选择器的作用,Q1被纠正。此时三模冗余结构其他两路之一由于重离子撞击,发生翻转,电路中仍有两路输出正确值,则电路工作正常。该结构完全克服了图1示出常用寄存器结构在上述示例中所引起的电路功能失常。在该电路结构中,只有当三模冗余结构中的两路同时发生翻转时才会引起不可纠正的电路软错误。

图5 自刷新寄存器原理图

4 实验结果和分析

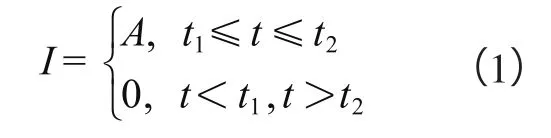

目前抗辐照仿真多采用在某一节点注入电流的方法,通过节点的寄生电容,将电流转化为电压,从而实现节点翻转。本文采用注入电流的方法来实现仿真,目前注入电流的方式主要有两种:脉冲电流法和双指数电流法。脉冲电流法是指给某一节点添加一个在某一段时间内有电流值,而在该段时间之外电流值为0。见式(1)。

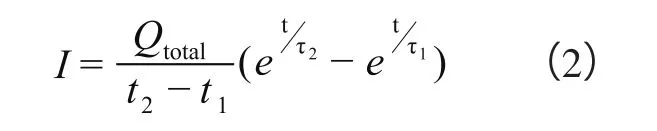

双指数法见式(2),可用verilogA编程设计输出电流给电路节点。

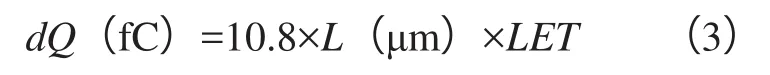

以设计目标抗单子翻转SEU错误率小于10-5/地球同步轨道每器件每天为例,根据航天研究院给出的LET转换结果37 MeV·cm2/mg。然后根据式(3)可计算出单粒子打入Si中注入的等效电荷量为400 fC,其中L为10 μm(10 μm为单粒子打入Si中的注入距离值,是一个经验值)。

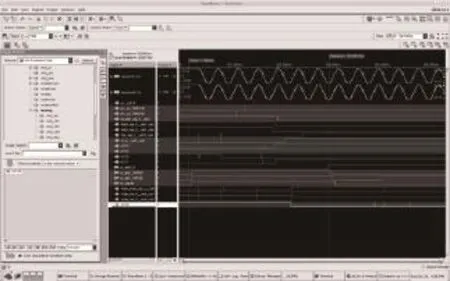

本文采用脉冲电流法进行单粒子实验仿真,根据每个单粒子打入后等效的注入电量值为400 fC,我们将电流脉冲值设定为1 mA,时间为0.4 ns,Hsim仿真结果见图6。图6中,Q值翻转,经过一个时钟周期,输出值被纠正,实验结果证明三模冗余结构中一个自刷新寄存器的输出值Q被打翻,在下一个周期将被纠正,在输入值改变之前不会一直保存错误值。

图6 单粒子翻转实验仿真图

图7 整体电路单粒子实验仿真图

为了验证所设计的基于三模冗余结构的自刷新寄存器的抗单粒子效应的能力,设计了单粒子翻转测试软件,对采用了此结构的整体电路每隔100 ns随机抽取节点1个,强制节点电压翻转,工作频率1 GHz,电路仿真结果如图7所示。可以看出最后的输出除了有些小毛刺外,波形正常。

5 小结

从实验结果可见,采用0.13 μm工艺条件,基于本文设计的自刷新寄存器的三模冗余加固结构,有效弥补了传统三模冗余在消除累积辐射效应方面的不足,可以有效防止SEU效应的发生。

[1] J L Barth. Modeling Space Radiation Environments [C]. IEEE NSREC Short Course, 1997: IV1-58.

[2] 徐静,陈玉蓉,洪根深. 驱动能力对SOI SRAM单元单粒子效应的影响仿真[J]. 电子与封装,2012, 12(7):34-37.

[3] 刘凡宇,刘衡竹,刘必慰,等. 90 nm CMOS工艺下p+深阱掺杂浓度对电荷共享的影响[J]. 物理学报,2011,046106-1-8.

[4] 刘真. 标准单元抗单粒子瞬态效应版图加固技术与验证方法研究[D]. 国防科学技术大学, 2011.

作者简介:

杨玲玲(1987—),女,江苏南通人,硕士研究生,主要从事封装信号完整性方面研究。

Design of Self-ref l esh Flip-f l op Based on Triple Module Redundancy

CHEN Zhongpeng, ZOU Qiaoyun, SHI Binyou, WAN Shuqin

(China electronics Technology Group Corporation No.58Rsearch Institute,Wuxi214035,China)

Designed a self-ref l esh fl ip-f l op which structure has two data latches and a voter circuit is added to the second stage latch. The function of the voter is to output the logic value that corresponds to at least two of its inputs. The new fl ip-f l op can be used to the circuit of triple module redundancy to instead of normal fl ip-f l op. It fabricated in 0.13 μm standard CMOS process occupies a die area of 32.4 μm×8.4 μm, the dynamic power consumption was 0.072 μW·MHz-1, the setup time is 0.1 ns, and the hold time is 0.08 ns. This structure was applied to Triple Module Redundancy can eff i ciently prevent Single Event Upset, and Experiment results show that Single-Event Effect Error rate lower than 10-5.

single event effect; fl ip-f l op; radiation effect; radiation hardened

TN386

A

1681-1070(2014)09-0021-04

陈钟鹏(1988—),男,毕业于山东大学,现主要从事于超大规模集成电路、高速高精度直接数字频率合成器和FPGA开发应用等方向的研究和设计工作。

2014-06-23