工艺阱深对CMOS集成电路抗闩锁性能的影响

2014-02-26韩兆芳虞勇坚

韩兆芳,虞勇坚

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

由于CMOS集成电路具有静态功耗低、温度稳定性好、噪声容限大及可集成度高等优点,在给定的封装内可容纳更多的电路,使CMOS成为数字电路、模拟电路以及同一芯片上构成数字、模拟混合电路的首选技术。虽然CMOS电路具有以上众多优点,但也有一些因自身结构引发的寄生效应限制了其优越性的充分发挥,隐含于体硅CMOS(指在硅衬底上制作的CMOS)结构中的闩锁效应就是一个最典型的例子,并且随着器件尺寸的不断缩小,闩锁效应对电路性能的影响将越来越明显。

2 闩锁效应机理

在CMOS集成电路中,闩锁是一种不可避免的寄生效应,对芯片的可靠性产生了很大的影响。闩锁效应是由存在于衬底和阱中的两个寄生双极型晶体管所引起的,这两个双极管构成一种PNPN寄生可控硅结构,在满足可控硅触发条件下,一旦被触发,会导致电源电压被拉低,同时从电源到地之间会有大电流流过,最终导致电路无法正常工作乃至整个电路芯片烧毁的失效。闩锁效应往往发生在芯片中某一局部区域,通常有两种情况:一种是闩锁只发生在外围与输入输出有关的地方,另一种是闩锁可能发生在芯片的任何地方,在使用中前一种情况遇到的较多。

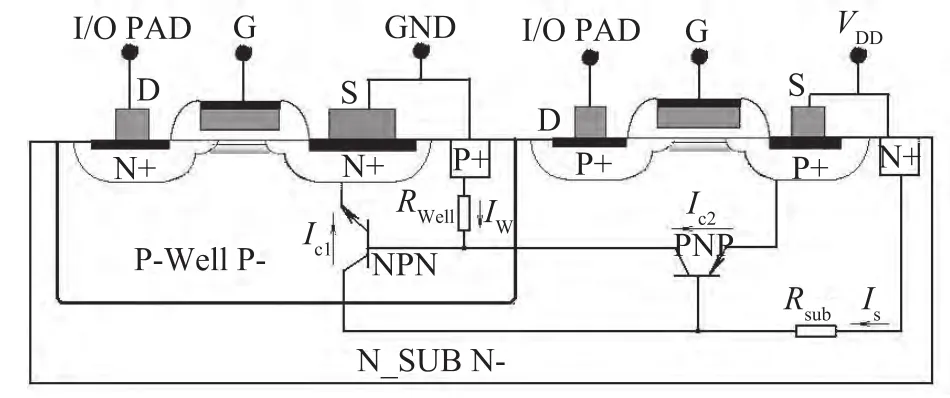

图1给出了带有寄生双极型晶体管的输出驱动P阱CMOS反相器结构截面图。从图中可以看出,在形成CMOS反相器结构的同时,也不可避免地产生了由寄生双极晶体管构成的PNPN器件,即可控硅(SCR),该可控硅器件由一个横向的PNP双极型晶体管和一个纵向的NPN双极型晶体管组成,即P沟道MOSFET的源(漏)极、N型衬底以及P阱分别为横向PNP双极晶体管的发射极、基极和集电极;N沟道MOSFET的漏(源)极、P阱及N型衬底分别为纵向NPN双极晶体管的发射极、基极及集电极。P阱和N衬底分别起两个作用,N衬底既是横向PNP管的基区,又是纵向NPN管的集电区;同样,P阱既是纵向NPN管的基区,又是横向PNP管的集电区。这种寄生的纵向NPN晶体管和横向的PNP晶体管通过P阱和共同的衬底耦合。

图l P阱CMOS反相器剖面图

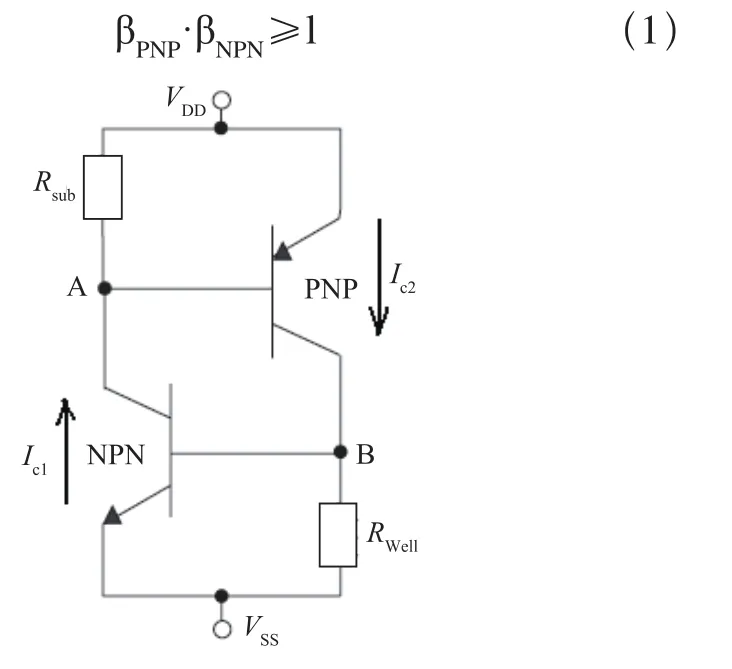

在图1中,Rsub表示从衬底接触到横向PNP管的本征基区的电阻,Rwell表示纵向NPN管的集电区到本征基区的电阻,提取图1中寄生的双极晶体管,得到如图2所示的可控硅简化等效电路图。CMOS反相器在正常工作的情况下,寄生的双极晶体管处在截止状态,器件正常工作。对于可控硅正反馈环路结构,如果有流经Rsub的电流注入,使得PNP管的VBE升高,Ic2增大,使得B点的电位VB升高;VB的升高使得NPN管的VBE增大,结果Ic1增大,结果导致A点的电位VA下降,PNP管的VBE继续增加,如果环路增益大于或等于1,这种状态将持续下去,直到两个晶体管完全导通,在电源与地之间形成低阻抗大电流通路,导致器件闩锁烧毁。

3 P阱深度对闩锁效应的影响

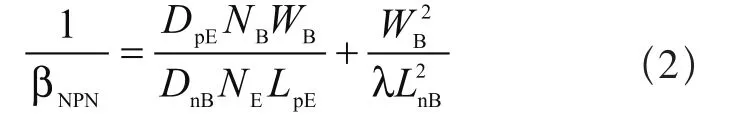

要触发电路寄生的闩锁效应,必须具备闩锁效应的触发条件,比如电源浪涌电压峰值超过器件的击穿电压,或者输出或输入电压高于VDD或低于GND等,除此以外,还必须要有寄生PNPN结构环路的电流增益大于l,即:

图2 可控硅(SCR)结构等效电路图

在寄生的PNPN可控硅器件中,P阱深度相当于纵向NPN管的基区宽度WB,且在一般有源区掺杂浓度高于P阱掺杂浓度2~3个数量级的情况下,共射极直流增益βNPN与器件结构参数的关系可近似表示为:

式中DpE、DnB为发射区、基区中少子扩散系数,LpE、LnB为发射区、基区少子扩散长度,NB、NE为基区、发射区掺杂浓度,WB为基区宽度,λ为与基区杂质分布情况有关的系数。

从式(2)中可以看出,NPN管的增益与基区宽度的平方近似成反比关系,如果将WB即P阱深度加深,可以明显降低NPN管的增益,从而降低βPNP·βNPN的值,在不增加CMOS反相器的PMOS管和NMOS管间距、不明显降低芯片集成度的基础上,增强电路的抗闩锁性能,提高电路的可靠性。

4 试验验证

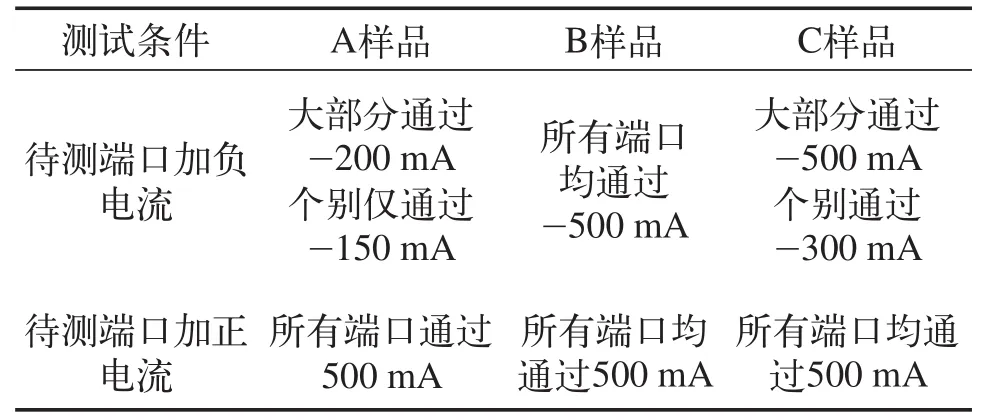

为了验证阱深对抗闩锁性能的影响,选择一款P阱CMOS工艺的高速接口驱动电路,在流片进行推P阱工艺时,A样品只进行一步注入推阱,B样品分两步进行注入推阱,其推阱时间明显长于A样品,并选择结构和功能类似的一款国外电路样品C,根据JEDEC标准《JESD78D IC Latch-Up Test》规定,测试三个样品电路的抗闩锁性能,测试结果如表1。

从测试结果来看,C样品的抗闩锁性能为300 mA左右,A样品抗闩锁性能仅在150 mA左右,而B样品则通过了500 mA的测试,B样品比A样品高2倍左右。

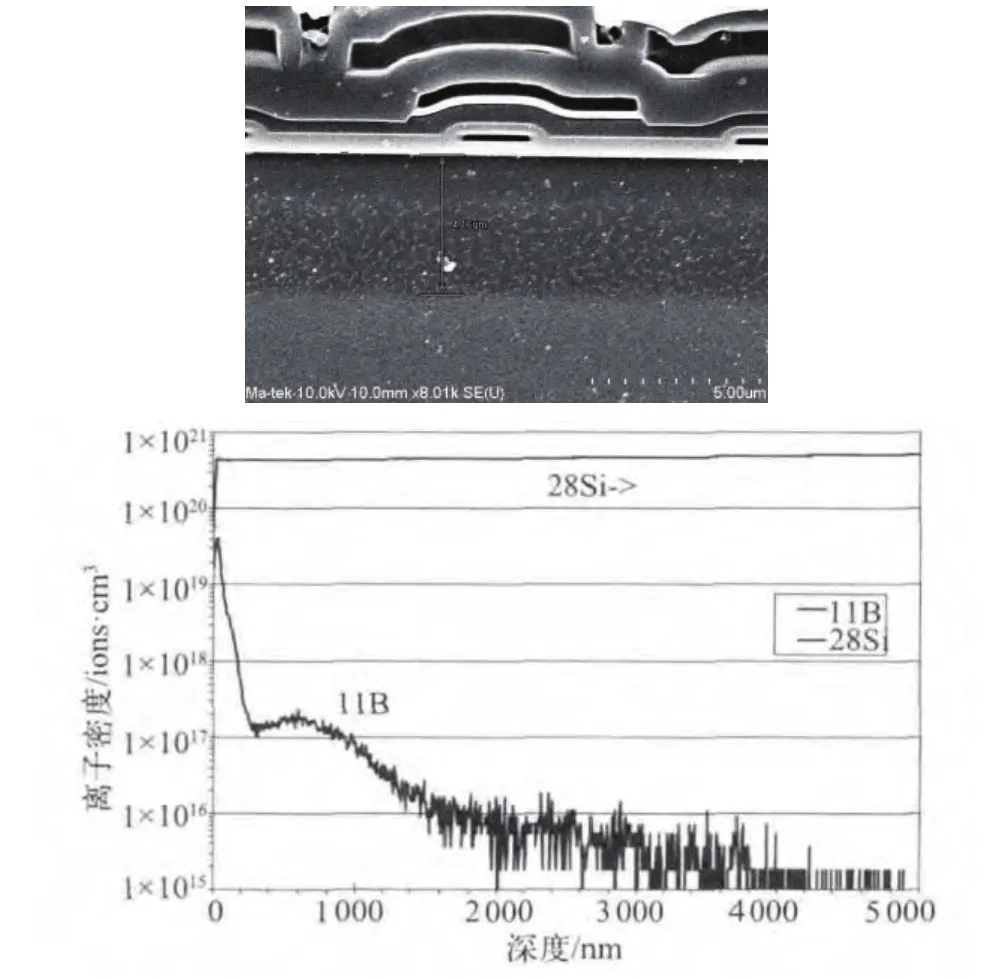

将样品纵向剖面染色后,利用扫描电镜(SEM)测量P阱结深,C样品的阱深为4.1 μm左右。利用二次离子质谱仪(SIMS)测量剖面阱中硼(B11)离子掺杂浓度的纵向分布,在4.1 μm深度后,硼离子浓度由1015/cm2很快降为1013/cm2,与SEM测量阱深结果一致。C样品的阱深SEM测量照片及SIMS测量浓度分布见图3。

表1 样品电路Latch-up测试数据

图3 C样品的阱深及硼离子浓度测量

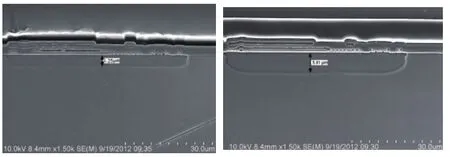

利用SEM测量A、B两种样品的P阱结深,B样品的阱深在5.8 μm以上,A样品的阱深仅为3.2 μm左右,样品阱深的SEM对比照片见图4。根据计算可知,样品的闩锁试验测试值和阱深的平方值近似于线性的正比关系。

P阱结深增加后,在测量阱反向击穿电压时,由于阱最底部的杂质浓度略有下降,阱底部耗尽区宽度相对于阱深增加前有所增大,同时阱边缘区域底部的曲率半径也有所增大,因此阱击穿电压会提高一些。器件的其他参数如寄生电容、寄生电感等均没有明显变化,因此对电路的速度、性能影响不大。

在体硅工艺中除了增加阱深外,还可以采用外延片或者沟槽隔离工艺来提升电路的抗闩锁性能。另外,通过版图设计技术,如增加少子或多子保护环、合理布局阱接触与衬底接触、加大PMOS管和NMOS管之间的间距等来避免电路产生闩锁。如果在电路设计完成后,因抗闩锁性能不足需要改进时,增加阱深只需要增加一块注入推阱光刻版,相对于其他方法更为方便有效。

图4 A样品(左)、B样品(右)的阱深测量

5 结束语

随着CMOS集成电路的飞速发展,电路规模和频率特性不断提高,器件加工的特征尺寸越来越小,电路的闩锁效应还会产生新的问题,闩锁效应的预防问题变得越发重要。因此需要采用工艺、设计、版图等各种技术,尽可能地避免、降低或消除闩锁效应的形成,从而为CMOS电路的广泛应用奠定基础。

[1] 施敏. 半导体器件物理与工艺[M]. 苏州:苏州大学出版社,2002.

[2] 郝跃,贾新章,董刚,等. 微电子概论[M]. 北京:电子工业出版社,2011.

[3] T F Miyahira, A J Johnston. Catastrophic latch-up in CMOS analog-to-digital converters [J].IEEE Trans. Nucl.Sci.,2001,48(6).

[4] Alan hastings. The Art of Analog Layout [M]. 北京:电子工业出版社,2007.

[5] 牛征.CMOS电路中的闩锁效应研究[J]. 电子与封装,2007,7(3).

[6] 唐晨,孙伟锋,陆生礼. CMOS电路中抗Latchup的保护环结构研究[J]. 现代电子技术,2006,(4).

[7] 毕查德·拉扎维. 模拟CM0S集成电路设计[M]. 西安:西安交通大学出版社,2002.