真实FPGA器件下单粒子软错误评估工具设计

2014-02-26周家成

周家成

(同济大学,上海 201804)

1 引言

基于SRAM工艺的现场可编程门阵列(Field Programmable Gate Array,FPGA)具有较高的逻辑密度,且因其灵活通用以及可重复配置的特点而广泛应用于航天电子系统中。然而在空间辐射环境下,SRAM型FPGA内部的配置存储器极易受到高能粒子的撞击而发生逻辑状态的翻转,导致电路结构发生改变而产生软错误。因此,可靠性已经成为FPGA设计最重要的指标之一。

已有研究成果证实,空间环境下由于辐射造成的可靠性问题91%来自于单粒子翻转造成的软错误[10]。软错误是可编程器件的配置发生改变导致电路功能错误的现象。为了缓解和消除软错误对FPGA器件带来的影响,学术界和工业界已经开展了丰富的研究,如文献[1,2]。然而这些研究往往基于通用的FPGA结构模型,而无法评估真实器件对单粒子软错误的反应;另一方面,采用对真实FPGA芯片进行高能粒子轰击的办法不仅价格昂贵,而且也无法在芯片的设计开发阶段开展软错误的评估,使得成品的软错误性能很难得到保证。

为了能够在FPGA芯片的设计开发阶段就对FPGA器件原型结构、布局布线(P&R)算法的软错误性能进行评估,保证芯片的可靠性,本文选择了已经广泛应用的Xilinx公司Virtex系列FPGA芯片[3]作为研究对象,设计并开发一款面向实际FPGA器件的单粒子软错误评估工具。Virtex系列FPGA芯片因其结构精简而具有代表性,至今在国内尤其是航空航天领域仍有广泛的应用空间。

本文在深入研究了目标FPGA器件底层结构的基础上,提取了SEU敏感单元的最小结构模型,并进一步通过实现FPGA配置文件的读入设计接口,实现了面向目标FPGA软错误的软件评估平台的建立。与目标硬件软错误效应的比对验证表明,本文提出的软错误评估工具可以准确地评估目标FPGA芯片的软错误特性。

2 相关工作

FPGA软错误效应的评估需要基于FPGA器件模型展开。本节将对国内外研究在这两方面的成果进行简要介绍。

2.1 通用VPR模型

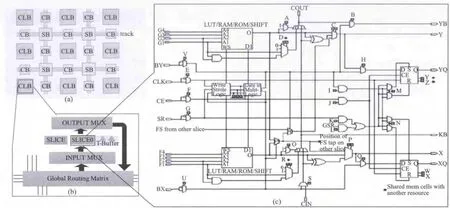

VPR是基于岛式结构的布局布线工具。由于其开源的布局布线算法在学术界和工业界得到广泛使用[4]。VPR将可编程逻辑器件按照功能逻辑划分为不同的组成模块,如图1(a)所示。

(1)可编程逻辑块(CLB),实现电路设计的逻辑功能;

(2)可编程I/O块(IOB),连接芯片引脚于内部信号;

(3)布线资源,即水平与竖直两个方向的布线通道;

(4)可编程连接模块,包括两种开关矩阵Switch Box和Connection Box,分别用于连接两个不同方向上的布线通道和连接CLB与布线通道。

VPR结构模型具有对称性,通过对每个不同模块进行建模描述之后,就得到了整个FPGA器件的结构。VPR采用的建模方法比CGE、SEGA更加精确[5],也给出了完整的P&R解决方案。但是VPR模型是基于实际器件的抽象,并不能精确对应实际器件的物理结构,因而不能为真实FPGA器件提供准确的故障模型。

2.2 Virtex FPGA器件模型

Virtex器件包含可配置逻辑块(CLBs)、输入输出块(IOBs)、RAM块(Block RAMs)、时钟资源、可编程布线以及配置接口电路。这些资源由配置码流文件(.bit)进行配置,通过配置接口完成一系列的配置指令以及配置数据的读写。

Virtex器件由多个重复的Tiles构成,包括CLB Tile、IOB Tile、DLL Tile等。其中CLB Tiles构成了Virtex器件的主体,如图1(b)所示。CLB Tile中除了预布线资源外,还包含了多种可配置资源,如两个逻辑功能单元(Slice)、两个三态总线驱动单元(T-Buffer)、输入输出模块(I/OMUX)以及全局布线资源(Global Routing Matrix,GRM)。其中,Slice内部可配置单元的详细结构由图1(c)进一步给出,它包含了逻辑生成器(LUT)、快速算数逻辑以及触发器来实现多种逻辑功能。同时,OMUX将Slice的输出接入全局布线资源,IMUX将信号从全局布线资源接入Slice和T-Buffer。可以看到,这些可配置资源的功能完全受控于预定的配置单元,并通过码流文件的配置完成预期的功能。然而一旦配置单元因为SEU而发生软错误,电路的功能或结构就会发生改变,影响整个FPGA器件的功能。

3 FPGA软错误评估平台的设计实现

为了评估Virtex器件的软错误效应,首先需要根据器件特点建立敏感资源的结构模型;同时通过对配置码流文件进行解析获取敏感资源的设计信息,实现FPGA功能网表的提取。在此基础上进一步利用故障注入技术和本文设计的软错误仿真软件分析软错误在器件中的传播,研究器件软错误效应的特性。实现上,本文利用Virtex器件结构化的描述工具RapidSmith[6],并对其进行结构和仿真功能的扩展,来满足本文提出的软错误效应评估工具的需求。

3.1 Virtex FPGA器件的配置组织

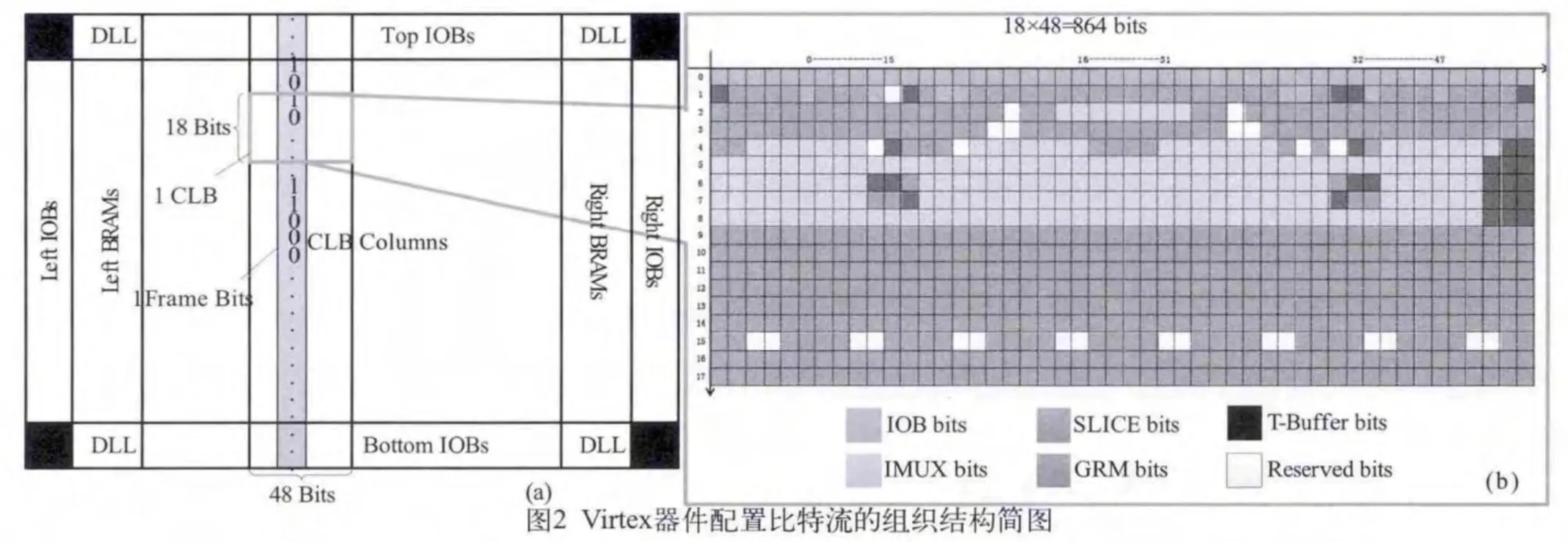

FPGA中可配置资源结构发生SEU的概率与该资源所占配置数直接相关[7]。由于CLB在Virtex器件中占全器件配置位的85%以上(如XCV300)[8],并且该比例随器件规模的加大而增加,因此本文主要针对CLB配置位进行SEU软错误效应的评估。

解决了这小小的不愉快,史黛西小姐带着大家继续参观。望着橱窗里那些珍宝,步凡瞪大了眼睛,赞叹的声音从他的嘴里溢出。就在他随着队伍边走边看边赞叹的时候,他的目光突然停驻在了展馆的角落——在那个展柜里,静静地躺着一本摊开的书,虽然书页已经泛黄,页面的边缘也显得残破而参差不齐,但让人疑惑的是,书上的字符不是工工整整的印刷体,而是龙飞凤舞的手写体!

图1 通用VPR结构模型和Virtex系列FPGA结构

如图2(a)所示,Virtex器件中配置码流的存储可以表征为比特矩阵的形式,其中包含了CLB中各种可配置资源的配置信息(含冗余比特)[9]。如果已知一个CLB配置位在其所属矩阵中的相对坐标,以及该CLB在整个器件中的空间位置编号,就可以计算出该比特在整个配置流中的绝对位置;反之亦然。

因此,本文首先通过对配置码流文件组织结构的分析获得了CLB配置矩阵与Virtex物理结构之间准确的对应关系,如图2(b)所示。根据这个对应关系,就可以建立配置码流文件中具体的一个配置位与Virtex器件中某个配置单元和可配置资源的联系,从而为软错误效应的准确分析打下基础。

3.2 软件平台的建立

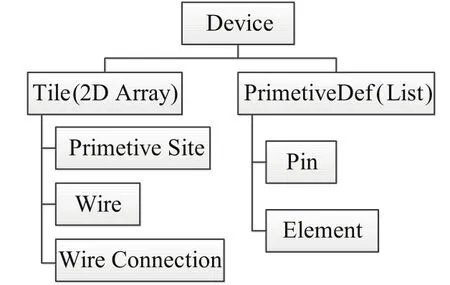

本文提出的软错误评估工具需要对器件的资源结构以及各种可配置资源之间的逻辑连接关系进行描述。为此,我们利用如图3所示的Device类来层次化地记录器件的结构和连接信息。Device类包含一个由Tile对象组成的二维阵列,以及一个Primitive Def类来对Primitive Site对象的结构进行形式化的定义。Tile对象专门用于保存各种资源间的连接关系。它包含三个类成员:Wire、WireConnection和Primitive Site。其中Wire描述了Tile中所有的硬线资源。每一个Wire有数个WireConnection对象与之对应,描述了这条硬线在器件中所有的连接关系,WireConnection的实例构成了器件中全部可供设计使用的连线资源。Primitive Site声明了Tile中存在的逻辑单元,如Slice、T Buffer,但并不描述其详细结构。

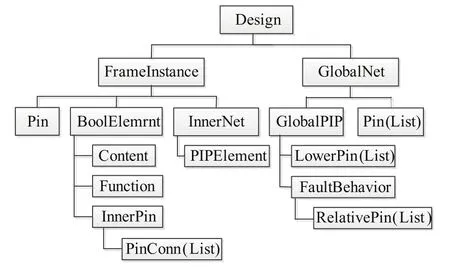

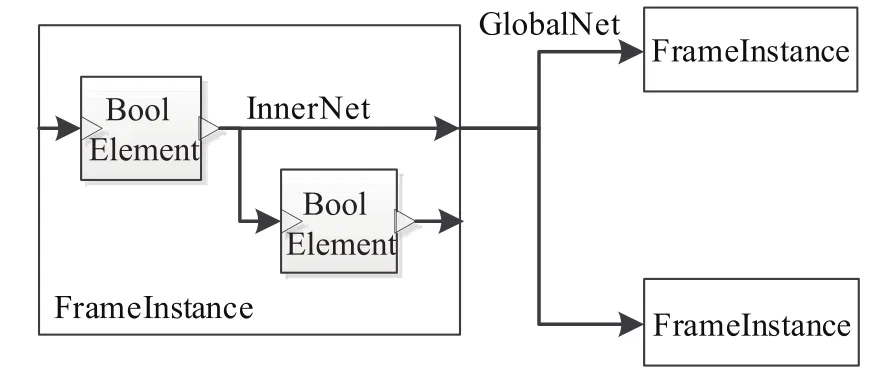

为了获得器件设计实例的功能网表,需要描述器件中逻辑电路的设计结构,即具体电路设计使用到的资源和连接情况。为此,我们利用如图4所示的Design类来层次化地描述FPGA所实现的逻辑网络。器件的逻辑网络包含两类:首先Frame Instance表示在设计中被实例化的Primitive Site,是顶层的逻辑结构;Global Net表示全局互联线网,连接各个Frame Instance形成顶层电路网络。

图3 FPGA器件资源模型结构

图4 FPGA设计结构模型

进一步,在Frame Instance内部,同样建立逻辑与互联资源的网络结构:Bool Element和Inner Net。Bool Element扩展自Primitive Def下的Element,描述了具有逻辑功能的Element,如LUT或逻辑门。它具备Runnable接口,能够被仿真内核调用实现功能函数的仿真。Inner Net在功能上类似于Global Net,它连接了Bool Element。

图5 功能仿真模型网络结构示意图

在完成器件资源的建模和电路结构的定义之后,读入ISE标准设计流程生成的.bit文件,以生成可仿真的链路网络模型。读入的过程首先将读入的配置文件的比特流按照其组织方式还原成配置矩阵,找出变化的配置位,再通过配置位的相对坐标找到其对应的可配置结构。接下来,得到了这些散列的可配置结构之后,建立两类线网对象,即Global Net和Inner Net实现可配置结构的互连。于是将FPGA电路建立了如图5所示的层次化网络结构,用于仿真软错误的注入、传播。

3.3 软错误故障注入、传播和显现

本文采用故障注入技术来模拟软错误对器件配置字造成的翻转情况。简单来讲,通过在码流文件中随即注入,通过配置位的索引查找到器件中该配置位对应的可编程单元,赋予其特定故障;再利用功能网表对电路进行仿真以模拟软错误在器件中的传播和显现过程,并最终将输出与真实电路的输出进行比较。

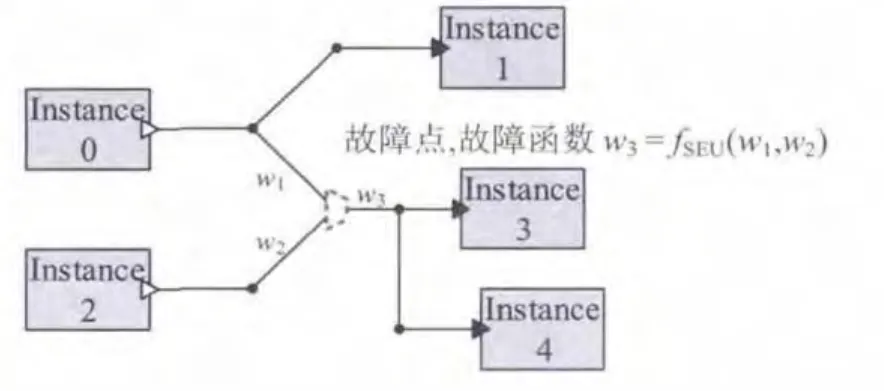

可配置单元的故障模型根据故障点发生的位置可以分为两种情况:当故障点位于Bool Element时,需要利用发生SEU后新的功能函数来替代原有功能函数进行故障单元的仿真;当故障点位于PIP时,如图6所示,需要根据故障敏感单元的故障模型计算故障点的行为函数,并将计算得到的故障电平值传播到每一个下游输入引脚。故障点的行为函数可能涉及多个Wire的电平值,比如在等效MUX结构随机发生SEU的情况下,这些输入Wire都有可能会被错误地输出,影响电路中信号的正确传播。

图6 PIP故障点的故障传播

4 实验结果与分析

为验证本文提出的软错误软件评估平台的准确性,我们以两个示例电路——8位的全加器和8位的乘法器来对软错误效应进行验证。具体来讲,通过软件平台对码流文件进行解析和仿真,读入到软件平台,并同时将相同的码流文件下载到硬件实验板,利用相同的输入向量比较软件的仿真输出与硬件输出的匹配度。

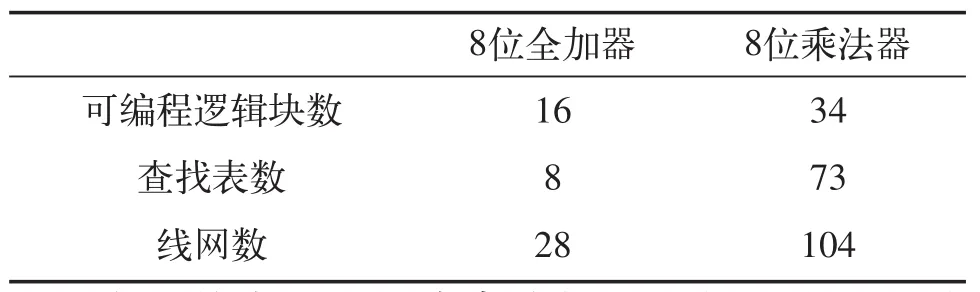

表1给出了两个示例设计完成ISE综合、布局布线、码流生成后在目标FPGA器件中资源的使用情况。虽然采用的示例电路没有占用全部的FPGA资源,但考虑到FPGA可配置资源具有高度重复和对称的结构,软错误在同类型资源上的效应也具有高度一致性的特点,因此采用的示例电路一定程度上可以较为准确地反映出本文提出的软件评估平台对软错误仿真的准确程度。

表1 实验电路在目标器件上资源的占用情况

实验首先对无故障电路模型进行测试,测试输入向量共256对。经验证,无故障电路仿真结果的匹配度为100%,即所提出的软件评估平台在无故障的条件下可以给出与实际器件完全相同的结果,这表明本文所提出的软件评估平台在功能上是正确的。

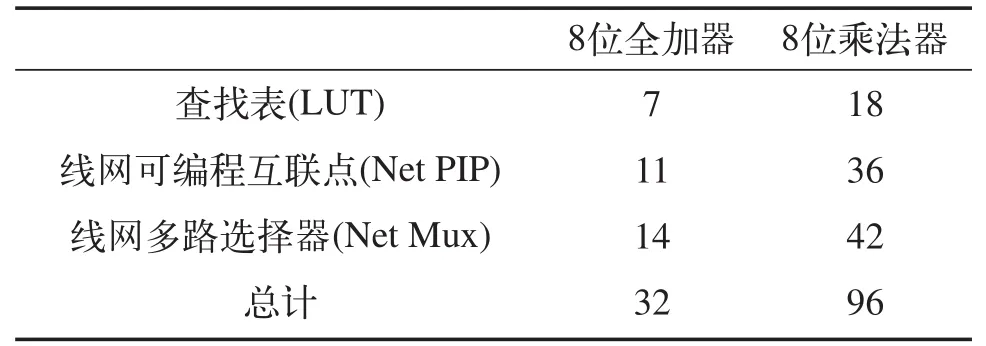

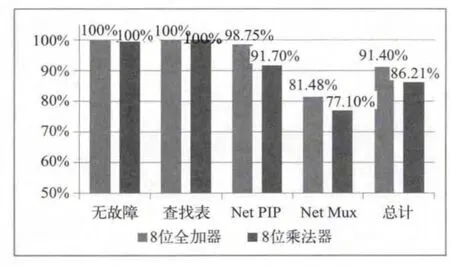

接下来随机对电路注入SEU故障并对故障电路进行重新仿真。同时将故障码流下载到FPGA器件上以比对两个平台的输出。表2给出了随机注入故障的总数和所在资源的分布情况,图7给出了软件仿真平台与实际FPGA器件在电路发生软错误下结果的匹配度。

表2 实验电路故障点所在资源的分布情况

图7 故障注入后软件仿真和实际器件的匹配度结果

实验结果表明,对于LUT和PIP中的软错误,本文提出的软错误仿真软件可以给出很好的仿真精度,匹配度达到90%以上;对于MUX来说,匹配度也达到75%以上。不同资源类型故障匹配度的差异,说明电路中实际结构的故障模型准确性是影响故障仿真结果的重要因素。总体来讲,利用本文提出的软错误评估平台在故障注入实验下与真实硬件的平均匹配度达到了理想的预测效果。这表明本工具对目标FPGA器件的软错误效应有很好的评估能力,也表明本文提出的软错误软件评估方法具有良好的应用价值。

5 结论与展望

本文设计并提出了一款面向真实FPGA器件SEU效应的软件评估平台。实验结果表明,本文提出的方法和平台可以准确地对目标器件的SEU效应进行评估,从而为FPGA结构设计和应用开发提供先于硬件实现的软件验证环境。通过对电路模型和软错误分析的改进,我们可以进一步提高对软错误效应的评估精度,为高可靠性FPGA芯片的研究、开发和设计提供更准确的参考。

[1] L Sterpone, M Violante. A New Reliability-Oriented Place and Route Algorithm for SRAM-based FPGAs[J]. IEEE Transactions on Computers, 2006, 55(6): 732-744.

[2] 李兴政,杨海钢,等. VPR在FPGA结构设计中的应用[J]. 电子器件,2007, (10):1874-1877.

[3] 基于Scrubbing的空间SRAM型FPGA抗SEU系统设计[J].

[4] 刘攀,周强,等. 基于VPR的层次是FPGA结构描述方法研究[J]. 微电子学,2009, (2):105-110.

[5] Vaughn Betz, Jonathan Rose. Automatic Generation of FPGA Routing Architectures from High-Level Descriptions[A]. In: FPGA. 2000.

[6] Christopher Lavin, Marc Padilla, etc. A Library for Lowlevel Manipulation of Partially Placed-and-Routed FPGA Designs[EB/OL]. rapidsmith.sourceforge.net/docs.html

[7] 周永彬,杨俊. SRAM型FPGA单粒子翻转失效率自动测试系统设计与实现[J].计算机测量与控制,2010,18(10): 2272-2274.

[8] Xilinx. Virtex Series Configuration Architecture User Guide[OL]. www.xilinx.com

[9] WANG ZhongMing, YAO ZhiBin, etc. Bitstream decoding and SEU-induced failure analysis in SRAM-based FPGAs[J]. SCIENCE CHINA-Information Sciences, 2012,(4): 971-982.

[10] P Graham, M Caffrey, J Zimmerman, D E Johnson, P Sundararajan, C Patterson. Consequences and Categories of SRAM FPGA Configuration SEUs. Militaryand Aerospace Applications of Programmable LogicDevices (MAPLD) ,2003.