SOI基横向SiGe HBT高频功率性能改善技术

2022-12-17金冬月张万荣那伟聪杨绍萌贾晓雪刘圆圆杨滢齐

金冬月, 吴 玲, 张万荣, 那伟聪, 杨绍萌, 贾晓雪, 刘圆圆, 杨滢齐

(北京工业大学信息学部, 北京 100124)

基于绝缘层上硅(silicon-on-insulator,SOI)技术的横向硅锗(SiGe)异质结双极晶体管(heterojunction bipolar transistor,HBT)具有寄生电容小、功耗低、抗辐照能力强、信号串扰低等优势[1-2],并与成熟的互补金属氧化物半导体(complementary metal-oxide-semiconductor,CMOS)工艺相兼容且电流驱动能力远高于CMOS器件[3-4],将在微波通信和高速混合信号应用中扮演越来越重要的角色[5-7].

与传统的纵向SiGe HBT相比,SOI基横向SiGe HBT具有对称的高掺杂发射区和高掺杂集电区结构,可有效避免基区扩展效应的影响[8-10],同时,通过不断缩小和优化器件尺寸,特征频率fT可高达THz[11]. 此时,如何使得器件在较高的工作频率和较宽的偏置电流范围内保持较大的电流增益β,对于改善SOI基横向SiGe HBT高频功率性能变得十分重要. 特别是横向器件特征尺寸缩小至nm量级以及高掺杂集电区的引入,都将降低击穿电压及器件在电路中的功率性能[12]. 因此,本文重点对SOI基横向SiGe HBT的高频功率性能改善技术展开研究,通过优化基区Ge的摩尔分数x(Ge)的梯形分布和复合衬底偏压结构,最终设计出兼具高频、大电流增益和高击穿电压的SOI基横向SiGe HBT.

1 器件建模

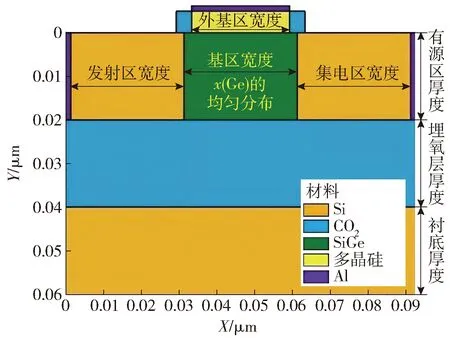

本文利用商业半导体仿真工具SILVACO TCAD的二维器件仿真器ATLAS建立了SOI基横向SiGe HBT器件模型,如图1所示. 该模型发射区宽度WE、基区宽度WB和集电区宽度WC均为30 nm,有源区厚度TSi、埋氧层厚度TBox和衬底厚度TSub均为20 nm. 基区掺杂原子浓度为1×1019/cm3,基区x(Ge)为20%,集电区和发射区掺杂原子浓度为 2×1020/cm3,外基区掺杂原子浓度为5×1019/cm3,详细的结构参数如表1所示.

图1 SOI基横向SiGe HBT器件模型Fig.1 Device model of the SOI-based lateral SiGe HBT

表1 SOI基横向SiGe HBT的结构参数

进一步利用二维器件仿真器ATLAS对器件的特性进行仿真,其中加入了迁移率受杂质影响模型、迁移率受电场影响模型、与温度有关的迁移率模型、禁带变窄模型[13]和俄歇复合模型,同时还加入了碰撞电离模型[14].

本文通过模拟得到了SOI基Si同质结横向双极晶体管的输出特性曲线,并与文献[15]中的实测数据进行了对比分析,如图2所示. 图中:IC为集电极电流;IB为基极电流;VCE为集电极- 发射极电压. 从图中可以看出,仿真数据与实测数据具有较好的一致性,从而验证了SILVACO TCAD仿真过程中所使用物理模型的正确性.

图2 SOI基横向双极晶体管输出特性实测结果和 模拟结果的对比Fig.2 Comparison of measured and simulated results of output characteristics of SOI-based lateral bipolar transistor

2 性能改善技术研究

基于上述器件模型,分别从β和击穿电压VCBO、VCEO方面研究基区x(Ge)的梯形分布设计和衬底偏压结构优化设计对SOI基横向SiGe HBT高频功率性能的影响.

2.1 基区x(Ge)的梯形分布设计

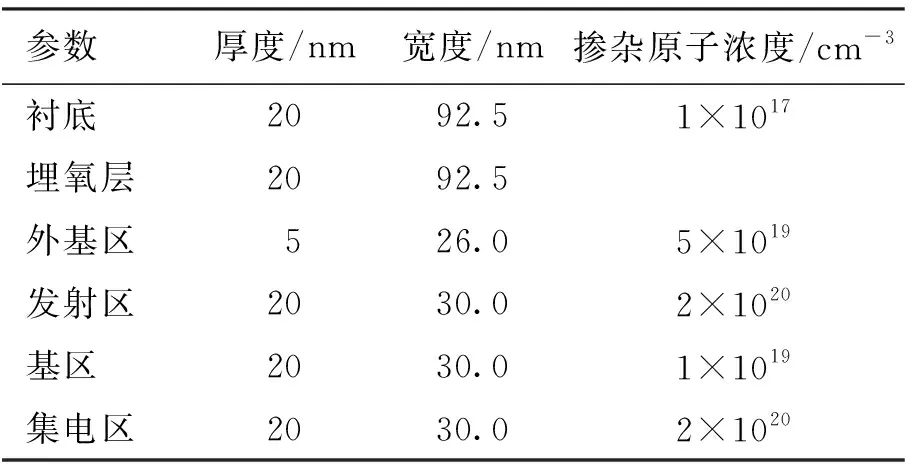

与基区x(Ge)的均匀分布相比,基区x(Ge)的梯形分布设计[11]可以引入漂移加速场,帮助少数载流子快速通过基区,增加电子向基区的注入,从而提高器件的fT. 图3所示为具有不同拐点位置的基区x(Ge)梯形分布设计,其中基区x(Ge)=20%. 当基区Ge的物质的量一定时,梯形拐点位置与集电结一侧x(Ge)的关系为

(1)

式中:yi代表梯形拐点的位置;xi代表集电结一侧的x(Ge);i=1,2,3.

图3 具有不同拐点位置的基区x(Ge)梯形分布设计Fig.3 Trapezoidal distribution design of x(Ge) in base region with different kink points

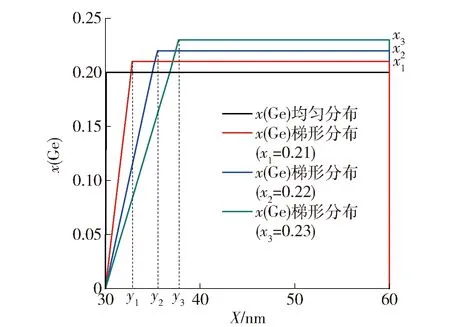

图4给出了不同基区x(Ge)梯形分布对器件fT的影响. 从图中可以看出,与基区x(Ge)均匀分布的器件相比,基区x(Ge)梯形分布时器件的fT得到显著提高. 当xi从0.21增加到0.23时,器件的峰值特征频率fTm从277.24 GHz增加到337.37 GHz,提高了21.69%. 这主要是由于基区x(Ge)梯形分布在基区产生一个电子加速漂移场,帮助载流子快速通过基区,随着梯形拐点位置向集电结一侧靠近,加速漂移场也逐渐向右延伸并增大,有效基区宽度减小,从而缩短基区渡越时间,因此,器件的fT得到显著改善.

图4 不同基区x(Ge)分布下器件fT随IC的变化Fig.4 fT versus IC of the devices with different x(Ge) profiles in base region

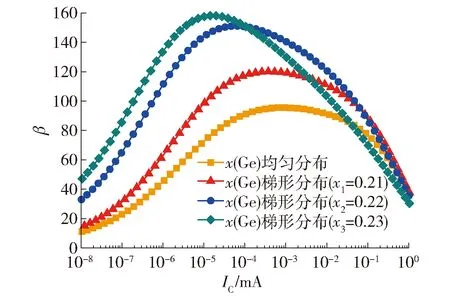

图5所示为不同基区x(Ge)分布对器件IC-β曲线的影响.可以看出,当xi从0.21增加到0.23时,峰值电流增益βm从119.92增加到158.07.这主要是由于随着xi的增加,yi由发射结一侧向集电结一侧转移,基区电子加速场增大,有效基区宽度减小,有助于电子在基区的传输,减少基区内载流子的复合,进而提高基区输运系数,因此,改善了器件的β.

然而,对于x3=0.23的器件,当IC>10-4mA时,器件的β迅速下降,限制了器件的电流处理能力.

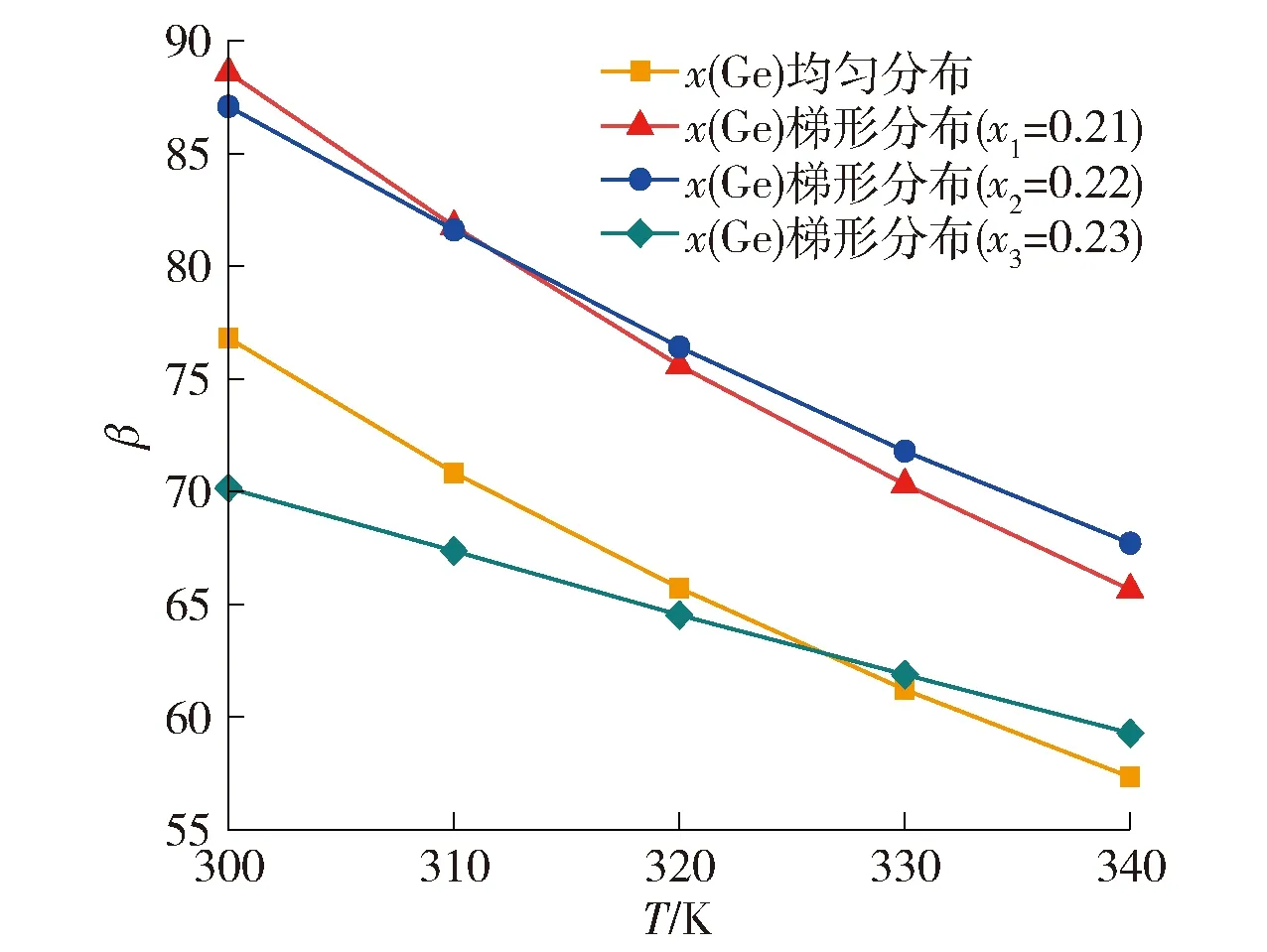

进一步给出了不同基区x(Ge)分布对器件β-T曲线的影响,如图6所示,其中,VCE=1.8 V,IC=0.1 mA.

图5 不同基区x(Ge)分布下器件β随IC的变化Fig.5 β versus IC of the devices with different x(Ge) profiles in base region

从图6中可以看出,当T从300 K增加到340 K时,基区x(Ge)均匀分布的常规器件和x2=0.22的器件β分别下降了25.37%和22.03%.与常规器件相比,x2=0.22的器件β的温度敏感性得到削弱,改善了器件电学特性的热稳定性.

图6 不同基区x(Ge)分布对器件β-T曲线的影响Fig.6 Effect of different x(Ge) profiles in base region on β-T curves of the devices

由文献[16]可知,对于基区x(Ge)梯形分布的器件,其β表达式为

(2)

式中:c=688 meV;k为玻尔兹曼常数;γ=Nc,SiGeNv,SiGe/(Nc,SiNv,Si),Nc,SiGe、Nc,Si为导带的有效态密度,Nv,SiGe、Nv,Si为价带的有效态密度;η=Dn,SiGe/Dn,Si,Dn,SiGe、Dn,Si为电子扩散系数.

不难看出,β是关于T的函数.下面具体分析比较2种器件(x2=0.22和x3=0.23)的β在温度特性上的差异.将它们的β分别对T求偏导并相减可得

(3)

(4)

不难看出,式(4)永远大于0,即与x2=0.22的器件相比,x3=0.23器件的β随T变化趋势更为平缓,采用基区x(Ge)梯形分布设计可有效削弱β对T的依赖关系.同时,与x2=0.22的器件相比,x3=0.23的器件的β有所下降.这是因为在Ge总量一定的情况下,x3=0.23的器件中性基区靠近发射结侧的x(Ge)较低,形成的空穴势垒较低,抑制空穴从基区向发射区注入的能力变弱,从而降低了发射结注入效率,导致β的下降.因此,在兼顾β及其温度敏感性的情况下,本文选用x2=0.22的器件进行进一步的研究.

2.2 衬底偏压结构优化设计

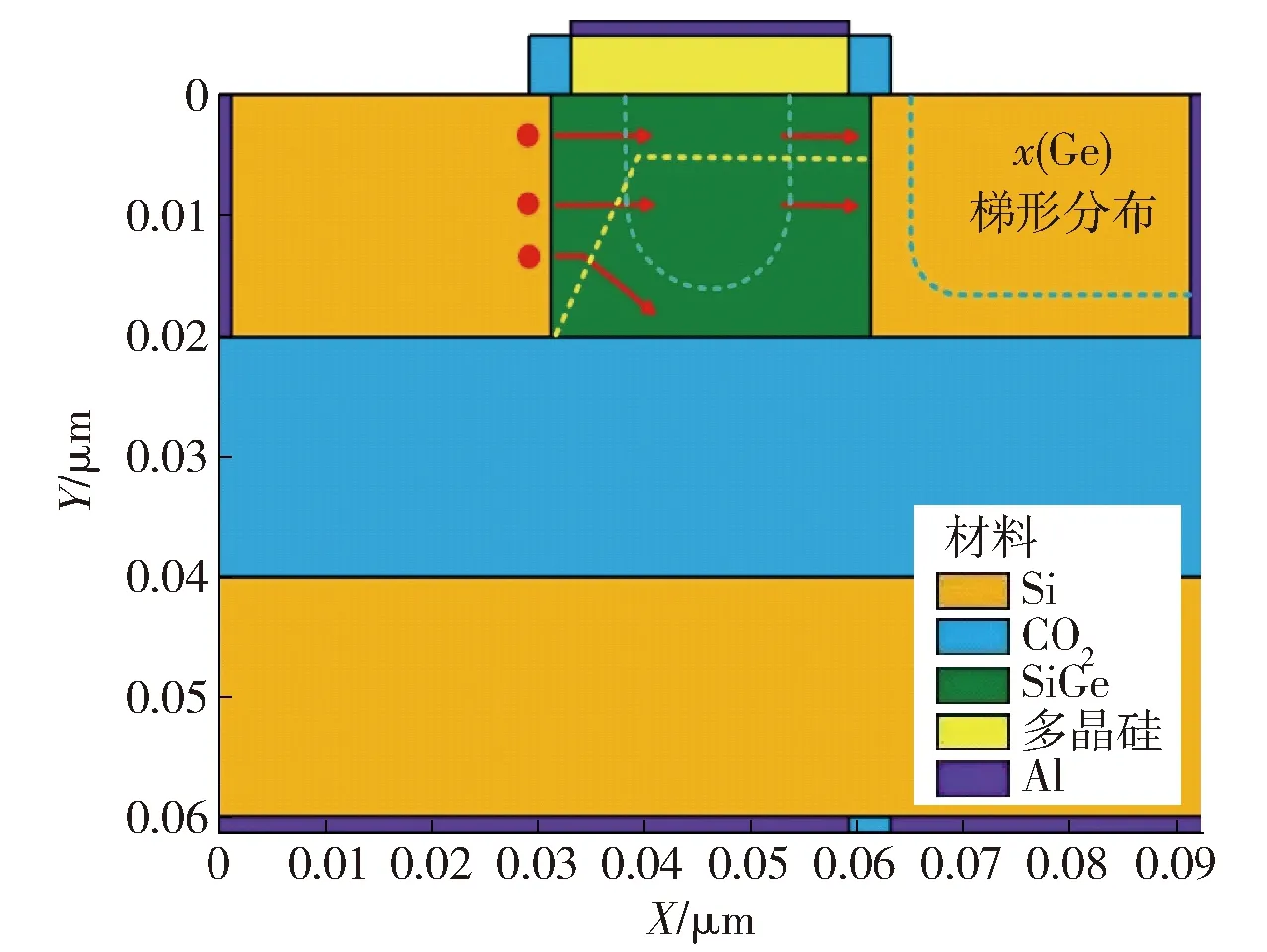

由于SOI基横向SiGe HBT结构上的特殊性,可以通过在衬底上施加正偏置电压(即衬底偏压结构)来调制载流子浓度和IC[17-19]. 本文首先给出了具有正衬底偏压结构的SOI基横向SiGe HBT的器件模型,如图7所示.

图7 具有正衬底偏压结构的SOI基横向SiGe HBT 器件模型Fig.7 Device model of the SOI-based lateral SiGe HBT with positive substrate voltage structure

当衬底偏压VS>0时,将在靠近埋氧层上方的基区内积累一层电子,此时基区内空穴部分耗尽,中性基区变小,形成的薄空穴耗尽层有利于电子从发射区输运到集电区. 此时的IC将由两部分构成:一部分电流为电子从发射区经由中性基区注入到集电区;另一部分电流为电子从发射区经由薄空穴耗尽层直接注入到集电区. 由于正衬底偏压产生的薄空穴耗尽层有效降低了电子从发射区注入到基区的势垒,从而增加了IC,有利于器件β的改善.

进一步研究了正偏压对器件IC-β曲线的影响,如图8所示. 与基区x(Ge)梯形分布(x2=0.22,x3=0.23)的器件相比,当VS=1.8 V且x2=0.22时,器件βm可以达到180.39,峰值集电极电流ICm为0.11 mA. 这主要是因为,正衬底偏压的引入使得埋氧层上方的发射区和基区形成了非常薄的电子积累层,导致埋氧层附近的基区被耗尽,基区空穴浓度下降,发射结注入效率提高,因此,器件的β得到显著提高. 同时,图9进一步给出了正衬底偏压结构对器件IC-fT曲线的影响. 从图中可以看出,正衬底偏置对器件fT的影响较小.

图8 正衬底偏压下器件β随IC的变化Fig.8 β versus IC of devices with positive substrate bias structure

图9 正衬底偏压下器件fT随IC的变化Fig.9 fT versus IC of devices with positive substrate bias structure

考虑到正衬底偏压的存在也会在靠近埋氧层上方的集电区内积累电子,进而使得集电区内电子浓度提高,将不利于器件的击穿特性. 因此,本文进一步提出了一种在发射区和基区下方施加正衬底偏压VS1,而在集电区下方施加负衬底偏压VS2的复合衬底偏压结构SOI基横向SiGe HBT,如图10所示. 其中,VS1和VS2之间使用SiO2侧墙进行电学隔离.

图10 兼具基区x(Ge)梯形分布和复合衬底偏压 结构的SOI基横向SiGe HBT器件模型Fig.10 Device model of the SOI-based lateral SiGe HBT with trapezoidal x(Ge) profile in base region and composite substrate voltage structure

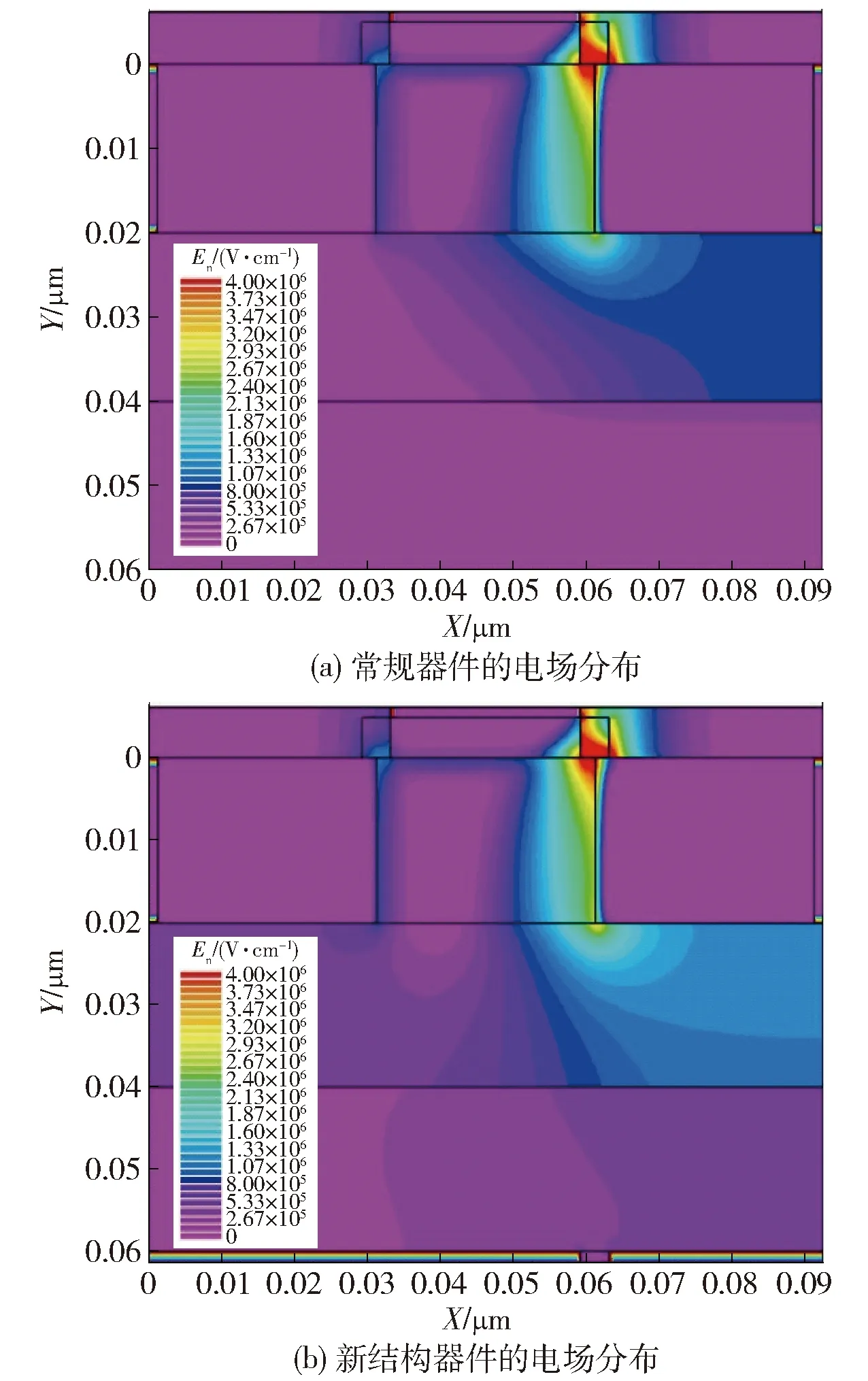

常规器件和兼具基区x(Ge)梯形分布和复合衬底偏压结构的SOI基横向SiGe HBT的电场对比如图11所示. 可以看出,与常规器件相比,具有复合衬底偏压结构的器件,由于集电区下方的负衬底偏压使得靠近埋氧层上方的集电区内积累一层空穴,集电区被部分耗尽,集电区电子浓度降低,集电结附近二维电场分布区域增大,从而有利于提高器件的击穿电压VCBO.

图11 新结构优化设计对器件电场分布的影响Fig.11 Effect of electric field distribution of the device by optimized design of the new structure

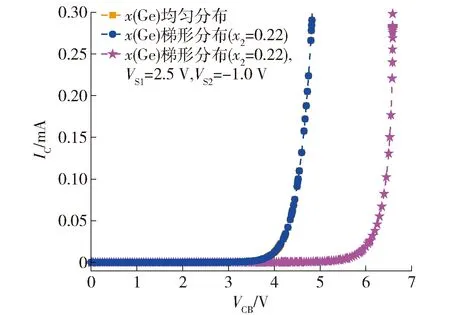

图12给出了新结构优化设计对器件击穿电压VCBO的改善. 图中VCB为集电极- 基极电压. 从图中可以看出,与基区x(Ge)均匀分布的器件相比,当正衬底偏压VS1=2.5 V,负衬底偏压VS2=-1.0 V时,击穿电压VCBO从4.6 V增加到6.5 V,改善了41.3%.

图12 新结构优化设计对器件VCBO的改善Fig.12 Improvement of VCBO of the device by optimized design of the new structure

根据能量平衡传输模型,电子的碰撞电离率αn[20]可以表示为

(5)

式中:a、b为拟合参数;En为与电子温度Tn相关的电场强度[20],可以表示为

(6)

式中C表示电子饱和速度与其能量驰豫时间的乘积.可以看出,αn与Tn呈指数关系,可以通过降低Tn来减小电子碰撞的概率,进而改善器件的击穿特性.

相同偏置条件下常规器件与兼具基区x(Ge)梯形分布和复合衬底偏压结构的SOI基横向SiGe HBT的Tn对比如图13所示. 从图中可以看出,与常规器件相比,新结构器件的Tn的峰值从7 081.37 K减小为7 040.92 K,即复合衬底偏压的引入使得器件Tn降低.

图13 新结构优化设计对器件电子温度分布的影响Fig.13 Effect of electron temperature distribution of the device by optimized design of the new structure

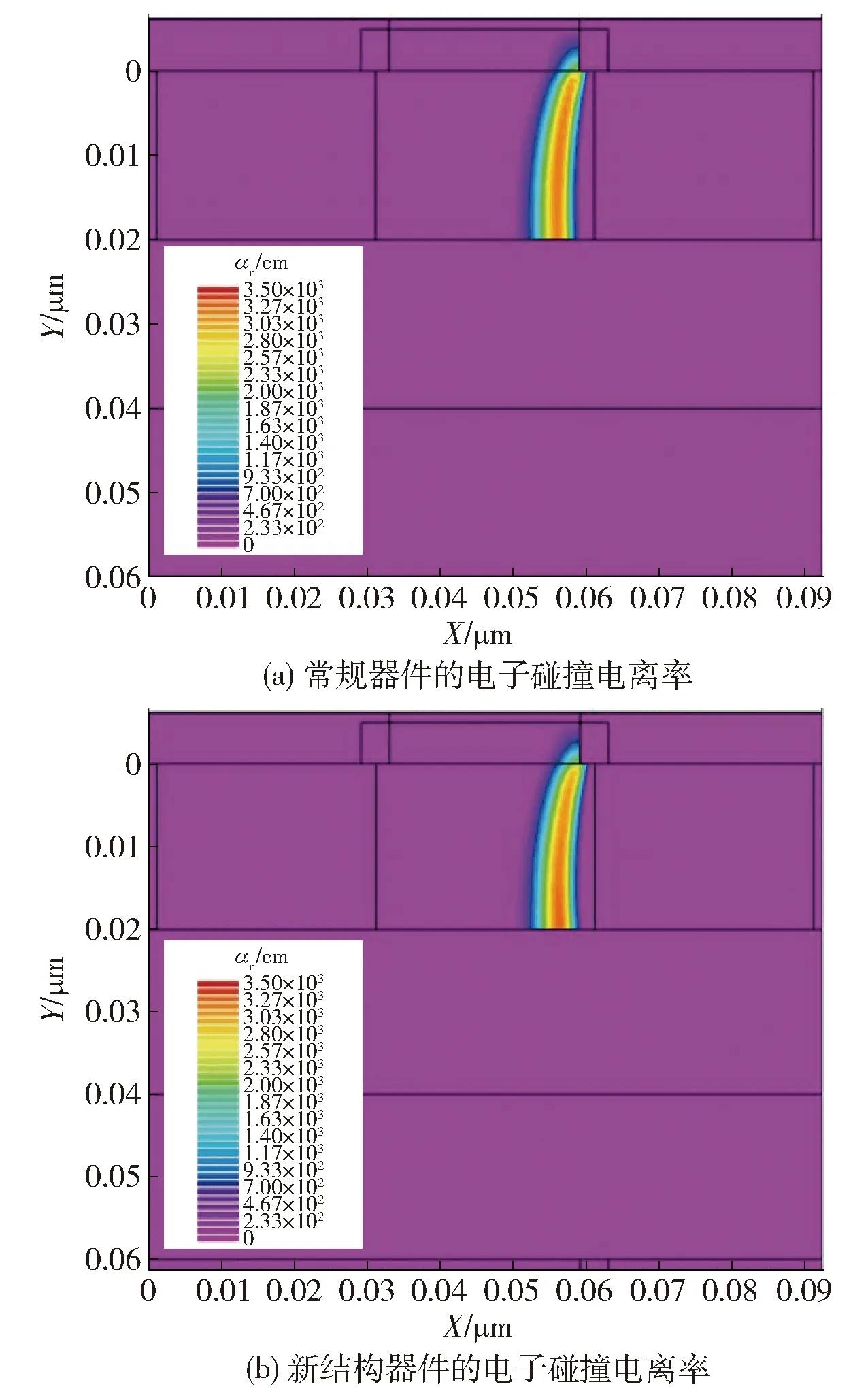

相应地,从图14所示的常规器件与具有复合衬底偏压结构的SOI基横向SiGe HBT的αn的对比图可以看出,与常规器件相比,新结构器件的αn峰值从3 241.4 cm-1减小为3 142.7 cm-1. 集电区下方负衬底偏压的引入也使得器件的αn降低,即有效减小了因碰撞而产生的载流子数量,从而有利于提高器件的击穿电压VCEO.

图14 新结构优化设计对器件电子碰撞电离率的影响Fig.14 Effect of electron impact ionization rate of the device by optimized design of the new structure

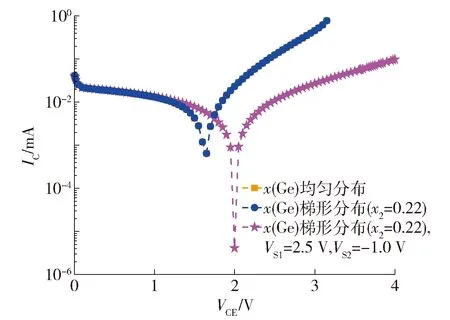

图15进一步给出了新结构优化设计对器件VCEO的改善. 从图中可以看出,与常规器件相比,新结构器件的VCEO提高到2 V,改善了21.2%.

图15 新结构优化设计对器件VCEO的改善Fig.15 Improvement of VCEO of the devices by optimized design of the new structure

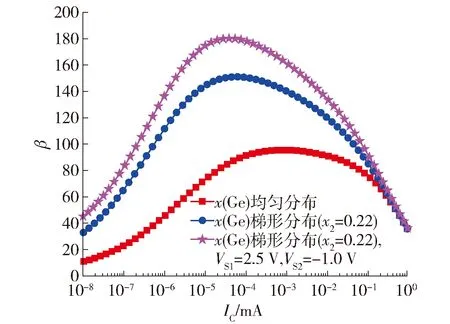

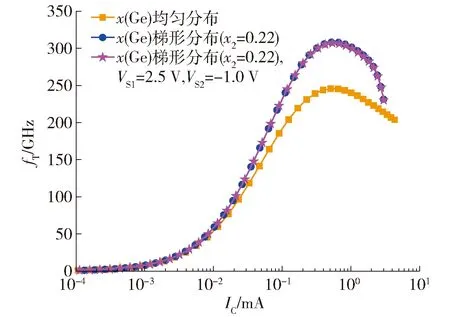

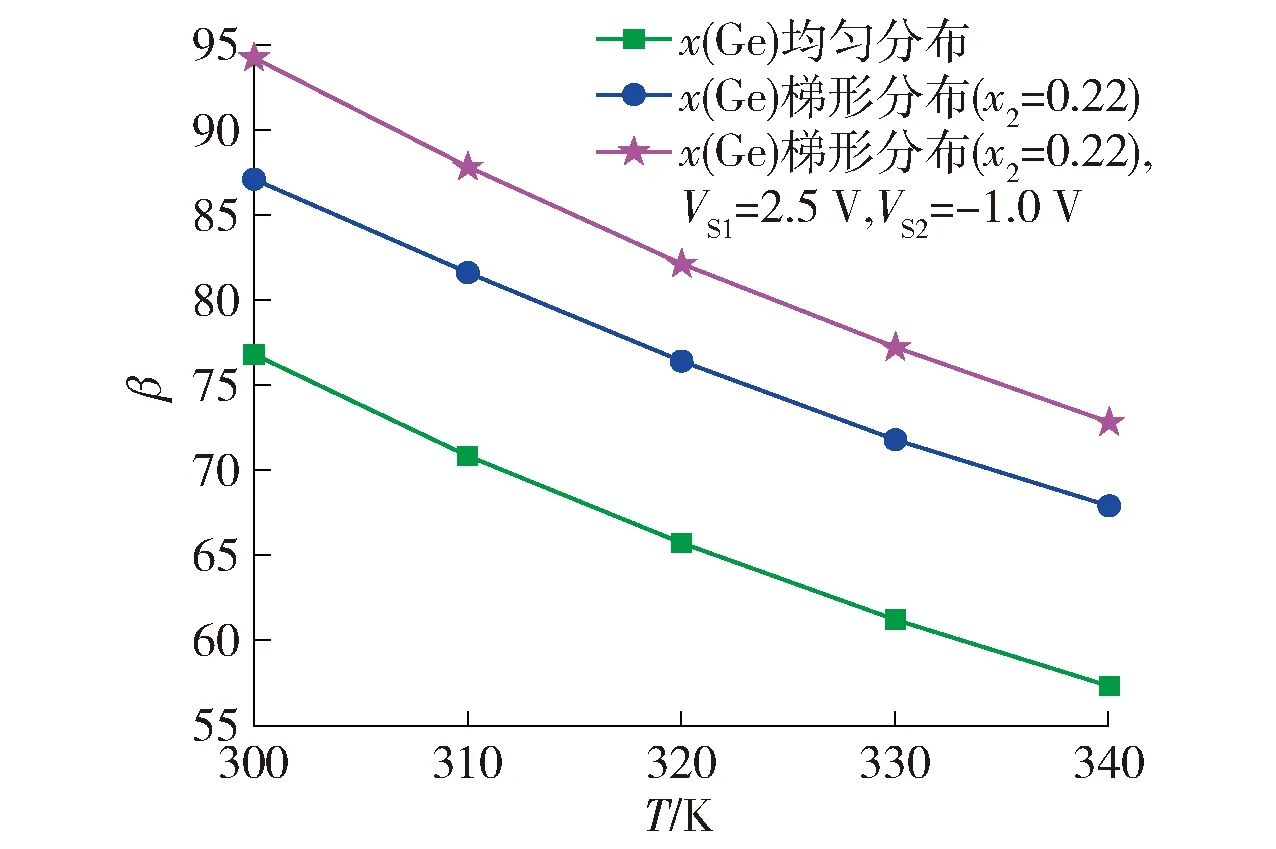

同时,图16和图17分别给出了新结构优化设计对器件β和fT的改善. 从图中可以看出,与基区x(Ge)均匀分布的常规器件相比,在大电流范围内,新结构器件的β和fT得到显著提高.

图16 新结构优化设计对器件β的改善Fig.16 Improvement of β of the devices by optimized design of the new structure

图17 新结构优化设计对器件fT的改善Fig.17 Improvement of fT of the devices by optimized design of the new structure

图18所示为不同衬底偏压下的β随T的变化曲线,其中VCE=1.8 V,IC=0.1 mA. 从图中可以看出,β随T升高呈下降趋势,与基区x(Ge)均匀分布的常规器件相比,当T从300 K增加到340 K时,具有复合衬底偏压结构且x2=0.22的器件的β下降了22.7%,β温度敏感性减弱,从而保证了器件电学特性的热稳定性,使器件可以在较宽温度范围内工作.

图18 新结构优化设计对器件β-T曲线的改善Fig.18 Improvement of β-T curves of the devices by optimized design of the new structure

3 结论

1) 为改善SOI基横向SiGe HBT的高频功率性能,本文设计出兼具基区x(Ge)梯形分布设计和复合衬底偏压结构的SOI基横向SiGe异质结双极晶体管,该器件可以有效提高器件的β、fT和击穿电压.

2) 由于引入基区x(Ge)梯形分布,将在基区产生电子加速场,进而减小有效基区宽度,一方面缩短基区渡越时间,fT得到提高,另一方面提高了基区输运系数,改善了β. 结果表明,当xi从0.21增加到0.23时,器件fTm和βm分别提高了21.68%和31.8%. 但对于x3=0.23的器件,当IC>10-4mA时,β迅速下降,而x2=0.22时,器件不仅在大电流范围具有较高的β,而且β温度敏感性也得到有效削弱.

3) 进一步通过优化衬底偏压结构,设计出兼具基区x(Ge)梯形分布和复合衬底偏压结构的SOI基横向SiGe异质结双极晶体管. 结果表明,与常规器件相比,新器件的fTm高达306.88 GHz,βm提高了84.8,击穿电压VCBO和VCEO分别改善了41.3%和21.2%. 本文工作对设计和制造出具有高频功率性能的SOI基横向SiGe HBT具有一定的理论和现实意义.