快速锁相无源三阶环路滤波器的设计与检测

2012-12-10王东虎

王东虎

(湖北广兴通信科技有限公司,湖北 荆州 434007)

0 引言

在现代的无线通信设备中,锁相环电路是很重要的组成部分。如何设计好高速、稳定的锁相环电路是很多无线通信研发人员面临的一个重要课题。锁相环中的鉴相和分频器均有集成芯片,压控振荡器也可订做,而环路滤波器必须要经过仿真或设计计算。本文将探讨2种快速锁相的三阶无源环路的滤波器的设计和3种环路锁定时间的检测手段。

1 锁相环电路的组成及环路滤波器的作用

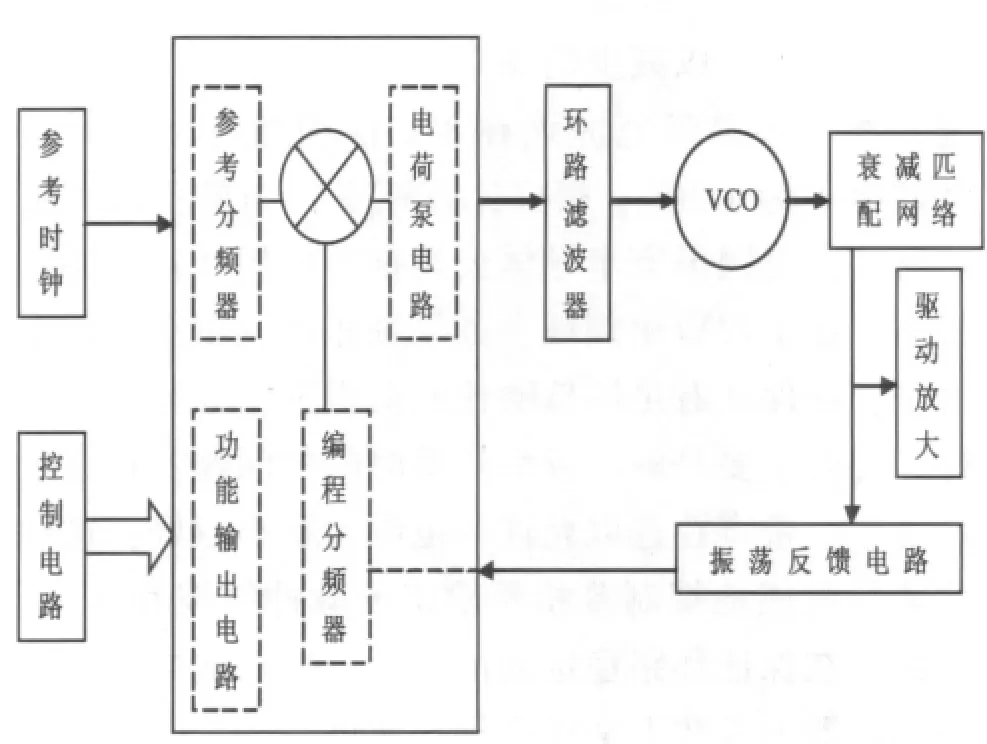

1.1 锁相环电路的组成

图1所示为基本的锁相环电路的组成。由参考时钟、控制电路、集成锁相芯片和环路滤波器、压控振荡器 (简称VCO)、衰减匹配网络、振荡反馈电路和驱动放大电路共同组成。其中环路滤波器的作用在锁相环电路中尤为突出。

图1 基本的锁相环电路的组成

1.2 环路滤波器的作用

环路滤波器可滤除鉴相器输出的误差电压和噪声,它将鉴相器输出的、含有纹波的直流信号平均化,并将此变换为交流成分少的、直流信号的低通滤波器。它除了滤出纹波外,还决定能否稳定地进行锁相环控制的传输特性。三阶环路滤波器比二阶能更好地滤除参考源的边带频率。在三阶无源环路滤波器的基础上,通过增加适当的硬件电路即可修改为快速锁相的环路滤波器。

2 三阶环路滤波的快速锁相设计方法

2.1 三阶环路滤波器设计参数对锁相速度的影响

在实际的现代通信设备的应用中,在频率波道切换时往往需要快速地锁定锁相环,特别是涉及到软件信令的沟通和传送,对锁相时间的要求就特别苛刻。一般在不考虑电源与分布电容和共模噪音对VCO影响的情况下:时间常数越小,相位噪声电平越小,截止频率越高,锁相速度越快,环路对鉴相器输出脉冲的纹波抑制越弱,相位比较频率中的频率变化急剧;时间常数越大,截止频率越小,对纹波抑制越好,相位噪声越大,锁相速度越慢。相位裕量越高,锁相环的稳定性也越高,但锁相时间变慢。相位裕量一般选择45°,就是为了让环路的稳定性和环路响应之间有一个好的折衷。相位比较的频率越高,环路的相位噪声就越小。环路带宽应该尽可能地窄以减少伪噪声,但是这会降低开关速度。通常环路带宽应该在1 kHz和20 kHz,但是必须至少为1/20fCOM相位比较频率;如果不在乎锁定时间,美国国家半导体公司推荐使用2 kHz环路带宽。在工程应用领域,如果锁相环应用在跳频系统中,在保证有足够信噪比的前提下,带宽越大越好,此时主要是解决频率转换时间的问题;在定频系统中,带宽在选取允许的范围内越小越好,这样才能尽可能地抑制鉴相器输出的脉冲纹波和噪声。因此,在保证环路稳定的前提下,可从选取设计环路滤波器的参数上来提高锁相速度:

1)环路的带宽尽可能地宽;

2)相位裕量 (也称相位容限)尽可能地低。

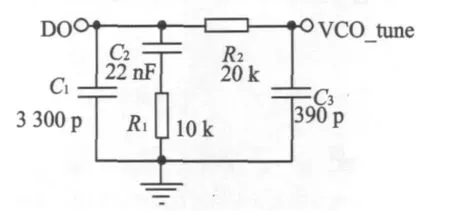

综合上述讨论,我们以中心频率fVCO=465 MHz为例,VCO的增益灵敏度KVCO=2 MHz/V,电荷泵增益 KΦ=1.25 mA/2 π, 比较频率 fCOM=200 kHz, 滤波器的环路带宽fC=2 kHz,相位容限φ=45°,参考时钟频率fREF=12.8 MHz,衰减20 dB,电阻R2=20 kΩ,经计算或仿真得三阶无源环路滤波器的参数,如图2所示。

图2 某三阶无源环路滤波器的参数

2.2 增加三阶环路滤波器硬件电路对锁相速度的影响

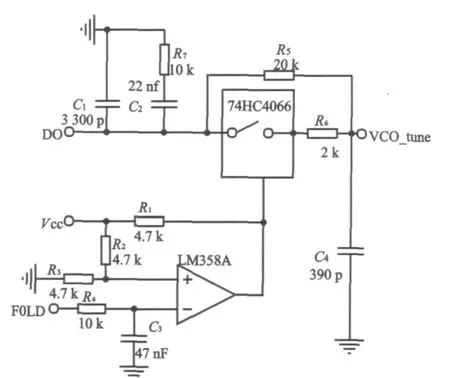

a)方法1:下面在图2电路的基础上,通过增加硬件比较电路和模拟开关,使环路的锁相速度得到进一步的提高,电路改进后如图3所示。

图3 增加了硬件比较电路和模拟开关的改进电路

当锁相环中的参考信号频率和比较频率有相位移状态时,锁相芯片中的F0LD管脚就变为低电平,无相位移时为高电平。将该管脚输出的脉冲平均化,用低电平表示失锁状态,这时,比较器输出高电平,模拟开关74HC4066接通,时间常数变小,锁相速度加快。一旦环路锁定,此时F0LD管脚就会输出高电平,比较器LM358输出低电平,模拟开关断开,对环路滤波的时间常数切换变大,这时又可对相位比较频率成分得到足够大的衰减,输出波形的寄生特性也不会变坏,改善了锁相速度而使其变快。

用同样的方式我们也可以对R7阻值进行模拟切换,若同时也将R5的阻值切换为适当值,则可以期待获得更快的锁相速度。

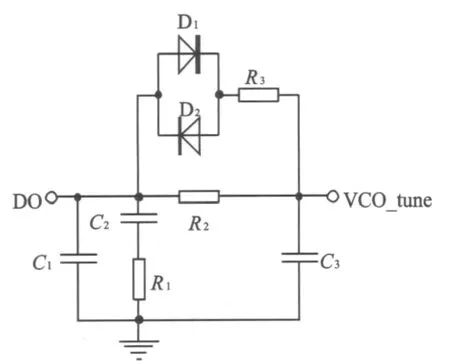

b)方法2:同样可以用增加两只极性相反的二极管并联后再串联一只电阻的方式以最少的元器件来提高锁相的速度。改进后的电路如图4所示。我们假设R3=2 kΩ,R2=20 kΩ。

图4 增加了两只极性相反的二极管的改进电路

根据图4,频率偏离大而失锁时,鉴相器输出大量的脉冲使D1和D2导通,环路滤波器的时间常数变小,环路快速锁定。当锁定时,鉴相器又无输出脉冲。R3两端几乎等电位,D1和D2截止,环路滤波器的时间常数变大,又有利于降低寄生成分和抑制纹波噪声。上述电路可大大提高锁相速度,但锁相后输出频率的寄生成分有一定的恶化。这是由于环路锁定后,为了补偿电容的漏电流与VCO的频率飘移,鉴相器输出窄脉冲,该窄脉冲使D1和D2导通,比较频率成分的衰减量减小的缘故。

结合图3和图4,利用一个50 Ω衰减为3 dB网络,通过订做或自行设计一个中心频率为465 MHz的压控振荡器VCO,加上SPF5043Z管子构成的驱动放大器,共同组成了完整的频率锁相环电路,通过该锁相环电路可检测验证环路的锁定时间。

3 锁定时间的检测验证

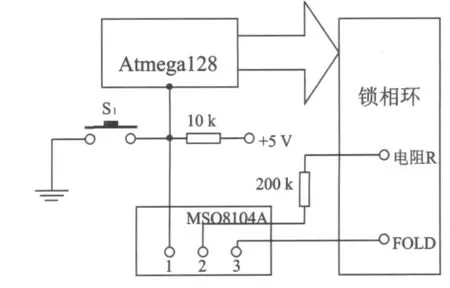

图5所示为测试锁相环电路的简易框图。其中测试按键S1分别连接基于Atmega128单片机为核心的测试夹具的中断管脚上。同时又连接到数字示波器MSO8104A的IN1端口上。IN2端口串接200 kΩ电阻连接到锁相环路滤波器上,具体连接到图4中的R2和C3交叉点上或图3中的R5和C4的交叉点上。IN3端口连接到锁相芯片的锁定管脚FOLD上。

图5 测试锁相环电路的简易框图

方法1:按照上述图5连好线后,所有的设备装置加电,选取IN1和IN2通道有效,MSO8104A设置IN1通道为下降沿触发。当S1的中断按键按下切换波道送频和数据时,该点既是测试锁相环时间触发的起点又是送频和数据的开始点,之所以选择中断按键就是为了让单片机以最小误差的方式实时修改锁相环需要的可编程分频数据。当环路锁定时,此时环路滤波器输出一稳定的直流电平,可从示波器上读出从触发点到稳定电平的时间差,该时间差即为锁定时间。

方法2:按照上述图5连好线后,所有的设备装置加电,选取IN1和IN3通道有效,MSO8104A设置IN1通道为下降沿触发。不同点就在于示波器的IN3端口接锁相环芯片的锁定管脚FOLD上。

a)当ATmega128单片机的初始化程序无频和数据送出,但设置一旦锁定时,FOLD管脚就为高电平。此时上电稳定后环路一直不锁定,但按下中断按键,程序送出频和数据时,环路未锁定时,FOLD输出低电平;一旦锁定,FOLD就输出高电平。同样可通过该按键触发状态的起始点和FOLD输出高电平的时间差来测试锁相环路稳定时的锁相时间。

b)当ATmega128单片机的初始化程序有频率和数据送出,同样设置环路锁定时FOLD管脚为高电平。通过此方法可以以最小误差的方式测试出两个频道切换时锁相环转换时的锁相时间。

方法3:用调制磁畴分析仪的测量仪器(HP53310A)进行测量,同样用外部中断按键S1触发信号测量瞬态响应特性的结果。该仪器是测试锁相环电路时常用的、非常重要的测量仪器。由于在屏幕上显示测量压控振荡器的输出信号的频率,横轴为时间,由于不受测量探头的影响,因此,可以正确地进行高分辨率的测量。

4 结束语

本文在无源三阶环路滤波器的基础上,在锁相环各种指标折衷稳定的前提下,要提高环路的锁相速度,除了适当地增加滤波器中环路带宽和降低相位裕量参数外,还可在三阶环路滤波器的基础上增加硬件电路来改善,并且通过3种技术手段来检测验证具体的锁相时间。

[1]远坂俊昭 [日].锁相环 (PLL)电路设计与应用 [M].第1版.北京:科学出版社出版,2006:1-238.

[2]SAYRE C W[美].无线通信设备与系统设计大全 [M].第1版.北京:人民邮电出版社,2004:204-218.

[3]韩库.浅议频率合成器中环路滤波器的设计 [J].电子元器件应用,2005,7 (1):35-36.

[4]陈冬云.ATmega128单片机原理与开发指导 [M].第1版.北京:机械工业出版社,2005:64-67