HC08芯片JVT测试方法的探究

2013-09-26张磊

张 磊

(天津铁道职业技术学院,天津,300240)

0 引言

HC08芯片是飞思卡尔半导体公司生产的一种工业用八位微控制器,其以结构简单、功能可靠、适用性强而在汽车电子、家用电子等各方面得到了广泛应用。为了保证HC08芯片的质量可靠性,必须要在芯片封装后对其进行参数测试和功能测试,JVT测试就是参数测试的一种,并且一般都作为全部测试的最后一项,为实现HC08安全可信的测试结果提供了重要依据。

1 HC08芯片的JVT测试1.1 JVT测试简介

JVT(Junction Verification Test)是 HC08 芯 片 测 试的一个重要组成部分,它通过测试与芯片管脚内部连接的保护二极管的特性,来检测芯片的各个管脚对电源脚、对接地脚是否能够可靠连接。

JVT测试通常安排在芯片测试的最后,即芯片在完成其它参数和功能测试后,再进行JVT测试,作为芯片质量测试的最后一道关卡,它能够探测出在前期测试过程中由于电压、电流过大而对芯片造成的破坏,保证测试的准确性和安全性。

1.2 HC08芯片的JVT测试原理

HC08芯片通常由CPU、ROM、RAM、SIM等模块构成。芯片中各个模块能否正常运行,都依赖于各个管脚对地和电源的可靠连接。JVT测试就是用来验证各个管脚对电源和地的连接状况的一种参数测试。

图1为HC08芯片一种典型封装形式的管脚示意图,图中Pin4为电源管脚,Pin32为地脚,其余管脚为I/O管脚或晶振、复位等功能管脚。JVT测试就是要验证这些I/O管脚和功能管脚能否对电源和地进行可靠连接。

HC08芯片进行JVT测试所需要的测试条件如下表1所示:

表1 HC08芯片JVT测试条件

JVT测试原理如下,如图2所示,在待测管脚和Vdd(电源管脚)之间加入灌电流,通常为5微安左右,利用J750平台的PPMU(精密测量单元)来测量管脚内部保护二极管的正向压降,对于硅二极管来说,如果压降在0.4V到0.8V之前,则表示保护二极管工作正常,待测管脚与Vdd之间实现了可靠连接,如果压降小于0.4V或大于0.8V, 则表示保护二极管未能正常工作,待测管脚与Vdd之间没有实现可靠连接,一般低于0.4V时表示二极管被击穿,高于0.8V时表示二极管与管脚断开,总之芯片为次品,需要淘汰。

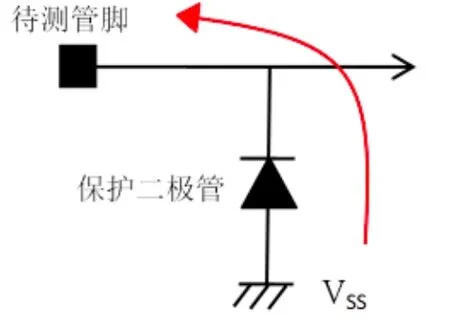

图3 管脚与Vss之间的JVT测试

图2 管脚与Vdd之间的JVT测试

同样还需要测试待测管脚和Vss(接地管脚)之间的连接情况,如图3所示,在Vss和待测管脚之间加正向电流,通常为100微安左右,来测量保护二极管的正向压降,如果压降在0.4V到0.8V之前,则表示保护二极管工作正常,待测管脚与Vss之间实现了可靠连接,否则,表示待测管脚与Vss之间没有实现可靠连接,芯片为次品。

1.3 HC08芯片的JVT测试过程

JVT的测试流程如图4所示,JVT测试需要先将芯片断电,让其它管脚处在悬空状态,再单独对待测管脚进行测试。这样充分避免了各个管脚之间的串扰对测试结果的影响,使测试结果更加精确,有效。

图4 JVT测试流程

如图5所示为J750测试平台,分为测试机、电源柜、计算机三部分,是目前对HC08芯片进行功能测试的主流测试平台。在测试时,先由Handler(机器人手臂)取芯片,之后通过测试电路板与J750测试机相连,然后利用IG-XL软件给出上电、下电、测试等各项指令,并由计算机输出最后的测试结果。

图5 J750测试平台

图6所示,即是用IG-XL软件对HC08芯片进行JVT测试时的参数设置界面,图中测试对象为 Ports(对应图2中的管脚3,5~26,28,31), osc1(对应图2中的管脚1), osc1(对应图2中的管脚1),osc2(对应图2 中的管脚2), cgmxfc(对应图2中的管脚27,29,30)这些管脚和管脚组,系统将依次给每个待测管脚加入5uA电流(其余管脚悬空),测试平台中的PPMU测量管脚对地或电源脚的电压。根据芯片材质、封装工艺及客户的实际需求,确定测试值的上下限,例如把JVT测试的上限值设置为750mv,下限值设置为250mv,将PPMU测出电压值,与上下限值比较,得出芯片pass/fail的结论。

图6 JVT测试的IG-XL软件界面

2 HC08芯片的JVT测试方法的优势

传统的开路/短路测试也是针对与管脚相连的钳位二极管的一种测试,它是通过DPS(Digital Power Supply)给待测管脚加电流,测量管脚与地和电源之前的电压,来判断保护二极管能否正常工作,如果电压过大,表示管脚与地或电源之间是开路状态,如果测得的电压过小,表示管脚与电源或地之间呈现短路状态。只有测量结果在上限与下限之间时,表示钳位二极管能够正常工作,待测管脚与电源和地之间实现了可靠连接。

与传统的开路/短路测试相比,JVT测试方法有效的克服了开路/短路测试对高阻态管脚不敏感的缺点。在进行开路测试时,假设对待测管脚加5uA的电流,测试上限值设为750mV,保护二极管的压降为0.6V,根据欧姆定律,在待测管脚和Vdd之间的允许电阻为(0.75V-0.6V)/5uA = 30KΩ,也就是说,假如由于静电击穿或半导体生产工艺中封装打线问题,造成待测管脚呈现30KΩ左右的高阻态,开路测试将不能有效测出。而JVT测试,通常可以在待测管脚和Vdd之间阻抗大于5KΩ时,即可判断芯片失效,能够有效的筛选出静电击穿的芯片次品。

图1 HC08芯片引脚示意图

3 结论

通过JVT测试法,可实现对HC08芯片所有功能管脚的保护二极管的测试,保证了芯片的正常功能,并能有效甄别出因为前期测试过程中的电压、电流尖峰而对芯片造成的损坏。

[1] MC68HC908JL16 data sheet,- freescale semiconductor, 2005.

[2] Fundamentals of Digital Semiconductor Testing,-freescale semiconductor, July 1999

[3] JVT Evaluation Reference (Rev 0.7) ,-OHT Market Business Group, April 2003

[4] J750 Basic Prog Student Manual(V3.4), -freescale semiconductor, 2003

[5] Visual Basic for Test –Teradyne company, 1999