直接数字频率合成器 (DDS)测试方法研究

2012-12-10蔡志刚王晓晗魏建中

蔡志刚,王晓晗,魏建中

(工业和信息化部电子第五研究所,广东 广州 510610)

0 引言

直接数字频率合成器 (DDS或DDFS:Direct Digital Synthesizer或Direct Digital Frequency Synthesizer)采用了一种从相位概念出发直接合成所需波形的合成原理[1],这种新的合成原理预先将波形各相位与幅值的对应关系储存在高速存储器中,形成一种固化的波形表。理论上可以储存任意形状的波形,常见的波形为正弦波、三角波等,工作时利用高速存储器作查寻表,然后通过集成高速数模转换器 (DAC:Digital Analog Converter)、 低通滤波器输出已经用数字形式存入的波形。近十几年间,随着微电子技术的迅速发展,DDS器件得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。其优点体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号以及多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比,是实现设备全数字化的关键核心器件,是国家重大专项研发器件。

1 概况

DDS器件内部既包含数字部分,也包含模拟部分,属于单片混合信号集成电路。一般而言,内部有模拟锁相环 (PLL:Phase-locked Loop)、输入输出 (I/O)接口、寄存器、频率累加器、相位累加器、高速静态存储器 (SRAM)、数/模转换器(DAC)和超高速比较器等模块,对测试系统的速度、精度要求特别高,测试比较困难。另外,DDS器件的测试参数众多,部分参数属于射频 (RF:Radio Frequency)参数范畴,如无杂散动态范围(SFDR: Spurious Free Dynamic Range)、 相位噪声(PN:Phase Noise),自动化测试难度大、实现成本高。

2 DDS器件测试

2.1 DDS器件对外接口特点分析

DDS器件对外信号接口包括时钟输入接口、控制信号输入接口、SPI协议接口以及DAC与低通滤波器输出接口。另外,器件在工作与测试中还有一些外围电路的支持等。

a)时钟输入接口

DDS器件支持多种系统时钟产生方式,主要有差分/单端直接输入、片内振荡器输出和PLL输出。GM495X器件的不同时钟产生方式主要由外部的CLK_MODE_SEL管脚结合内部寄存器CFR1[4]和CFR2[7:3]联合控制。

b) SPI接口

通常DDS器件与微控制器/微处理器或其它外部设备的接口方式都是以SPI协议接口为甚础,用户可以通过该接口对GM495X内部的所有寄存器进行读写。在读写过程中,可以方便地选择数据最高位在前或者是最低位在前两种不同的操作方式。SDIO接口既可以作为单向输入也可以作为双向的输入输出接口。

c)DAC输出接口

DDS器件内部集成的DAC直接决定了DDS器件输出的波形质量。GM495X内部集成的DAC有两个特点:1)精度高,其内部DAC为14位精度的电流型DAC;2)其输出采用差分形式,这种输出形式有效地降低了输出信号的共模噪声,提高了输出信噪比。

2.2 DDS器件功能测试方法研究

a)时钟配置方法研究

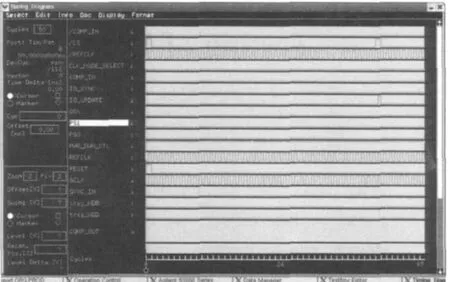

时钟信号采用测试系统模拟输入的办法,可以采用差分输入,也可能采用非差分输入的方法。相应的控制脚为CLK_MODE_SEL,相应的内部控制寄存器为CFR1与CFR2。两个寄存器与控制脚应满足一定的关系。图1是一个测试系统实际配置的输入时钟波形示例,图中CLK_MODE_SEL脚为低,/REFCLK脚为20 MHz的方波,时钟经过内部倍频后 (倍频系数由CFR2[7:3]设定),达到400 MHz,即系统时钟为400 MHz。

图1 测试系统配置的时钟波形图

b)SPI口读写测试验证

在配置的过程中,还可以选择数据输入的最高位优先和最低位优先两种输入形式。通过SPI口对每一个寄存器的配置分为两个阶段:命令传输阶段和数据传输阶段。

下面是测试系统配置内部寄存器的一个例子,如图2所示。

图2 SPI口配置寄存器示意图

图2中,采用二线模式对寄存器进行操作,即SDIO作为输入输出,分时复用。

c)DAC输出波形的功能验证

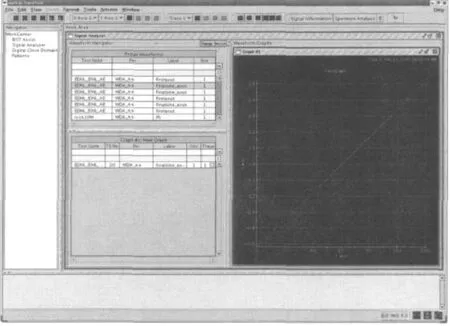

从应用功能上看,DDS器件有多种工作模式和多种省电模式。工作模式最简单的是单频点模式,还有跳频模式和各种扫频模式,如直接转换模式、上斜坡模式、双向斜变模式、连续双向斜变模式和连续循环模式,以及相位调制功能。DDS器件省电模式有软件控制模式、快速唤醒模式、全睡眠模式等。最终的DAC输出是器件是否具有正常功能的关键判断依据。图3是测试系统测试过程中的一个实例图。

图3 ATE机台的实测试输出图

2.3 DDS器件参数测试

DDS的参数分为几类:1)数字电路部分,含输入高低电平测试、输出高低电平测试、输入漏电测试、建立保持时间测试以及输出延时测试、输出上升下降时间等;2)模拟电路部分,含微分非线性度 (DNL:Differential Non-Linearity)、 积分非线性度 (INL:Integral Non-Linearity)以及零点误差(OE: Offset Error)、 增益误差 (GE: Gain Error,)等;3)RF参数部分,含无杂散动态范围 (SFDR:Spurious Free Dynamic Range)、 相位噪声 (PN:Phase Noise)等,还有一些其它参数,如多芯片同步步长、DAC输出电流、输入端电容和功耗等。

2.3.1 SFDR、PN的测试参数的实现方法

对于一个静止、稳定、连续的信号,SFDR、PN可以用专业的仪器进行测试与分析。对于DDS器件,其内部含有多个模块,数模混合,器件需要在特定的时序下才会有正确的输出。整个配置、输出、测试与分析过程是一个高速动态的过程,仅仅用频频分析仪之类的分立仪表无法进行测试。

93000 测试系统的优势在于对数字逻辑信号的处理,但无法象频谱分析仪一样对射频信号进行测试与分析。DDS射频信号的测试需要采用技术手段,将93000测试系统与频谱分析仪融合在一起才能完成测试。

a)硬件联接

首先,为了保证各硬件互相之间能正确地识别,必须给不同的硬件分配唯一的硬件地址。其次,应将各硬件的GPIB接口通过GPIB线联接起来,确保各GPIB设备处于同一网络中。

b)软件编程

GPIB接口软件编程可采用C++语言进行。编程中应注意按以下几点进行:1)搜索指定地址的硬件;2)向指定的地址发送指令,确保指定地址对应的硬件初始化;3)调用GM495X的功能测试向量,通过测试系统加载后,保证DAC有正确的输出;4)向指定的地址发送指令,确保指定地址对应的硬件对DAC输出波形进行采用并处理;5)获取数据处理结果并返回。

2.3.2 DAC静态参数测试

DNL、INL、OE、GE是DAC的静态指标,与速度无关,只能在静态条件下进行测量。

DDS器件一般只通过DAC输出正弦波余弦波,按照现行国家标准与国家军用标准[2],测试DNL、INL、OE、GE时,需要对器件进行比较特殊的配置,使之输出三角波或锯齿波,随后进行相应的软件计算,分析出相应的技术指标数值。

由于有软件程序的运行时间不一致,当完成采样并数字化后,得到的波形可能是一个起始时间不定的波形;从总体上看,可能是不完整的三角波,也可能是大于一个周期的三角波,如图4所示。这种波形不能直接用于数据分析与处理,必须通过软件编程提取单调区间的数据,如图5所示的波形数据,才可能进行后续的参数分析处理。

图4 实测GM495X三角波输出波形

图5 提取的斜波波形

2.3.3 频率响应时间、相位响应时间、幅度响应时间的测试方法

a)参数特点分析

以频率响应时间为例,它是指从 “I/O UPDATE”信号触发开始到DAC输出信号频率发生改变的时间间隔。

b)频域内的测试方法分析

采用频域内的测试方法,当频率发生改变时,比较容易判断,但是从信号输入到测试结果输出,仪器的测试总时间至少都是毫秒级,但DDS器件的更新时间一般在几十个纳秒左右,很显然这种方法对频率的改变判断虽然准确,但反应时间过长,实际测试过程中可实现性差。

c)时域内的测试方法分析

在时域范围内准备判断频率的改变值的确比较困难,但是判断频率的改变却是非常直观,是一种具有可行性的测试方法。图6是寄存器更新到频率改变 (从10 MHz变为160 MHz)的延时时间的实测图。图7是寄存器更新到相位发生改变的延时时间的实测图。

图6 频率更新延时图

图7 相位更新延时图

3 其它

3.1 测试中的注意事项

a)GM495X内部DAC的设计最大输出电流为15 mA,在实际的使用中,为了使输出波形有比较好的无杂散动态范围,一般会配置适当的外围电阻使输出电流为10 mA左右。DAC输出电压范围应为AVDD-0.5~+0.5 V,如果超出了这个范围,会造成DAC的输出失真,甚至还会损坏内部的DAC电路,所以在测试DDS器件时,需要关注其外围电阻。

b)配置到GM495X寄存器的数据信号在内部与SYNC_CLK管脚的时钟信号是同步的,所以用于指示数据更新的I_O_UPDATE脚的输入信号也需要与SYNC_CLK脚的时钟信号同步。而SYNC_CLK脚的时钟信号是通过对系统时钟进行4分频产生的。虽然对I_O_UPDATE脚的输入信号没有占空比的要求,但是要求I_O_UPDATE脚的输入信号其高电平宽度必须大于一个SYNC_CLK脚的时钟信号周期。

c)在读写操作的过程中,CS和IOSYNC两个管脚的信号必须保持为低。还需要注意的是,当进行读操作时,在读入命令传输阶段最后一个比特的时钟周期的下降沿就已经开始输出数据,此时如果使用两线模式,请务必在此时保证外部对SDIO脚的输入呈现高阻态,防止因出现SDIO脚的输出电平与外部电路的输入电平相反的情况而烧毁器件。

d)从现有、已经测试过的DDS产品来看,要注意复位RESET信号与信号之间的时序,否则第一次SPI读写就可能出错。

e)外部联接的频谱仪的反应时间应比较快,这样会节省ATE测试时的整个测试时间。

f)本文只讨论了DDS器件RF参数测试在ATE机台上的实现方法,RF参数测试准确性与测试板的设计和外围电源及信号质量的相关性比较大,在测试过程中应特别关注。

[1]BRANDON D,KORNBLUM J.多通道频率合成器应用得益于精密频率合成技术 [J].中国集成电路,2006,88(9): 76-80.

[2]SJ/T 10818-1996,半导体集成非线性电路数字/模拟转换器和模拟/数字转换器测试方法的基本原理 [S].