FPGA实现RS-422通信的一种改进方法

2012-12-03衡燕,黄勇

衡 燕, 黄 勇

(上海无线电设备研究所,上海200090)

0 引言

FPGA全称Field Programmable Gate Array(现场可编程门阵列),是目前广泛采用的一种可编程器件,它的应用不仅使得数字电路系统的设计非常方便,并且大大缩短了系统研制的周期,缩小了数字电路系统的体积和所用芯片的种类与数量[1]。

RS-422是一种单机发送、多机接收的双向、平衡传输规范,被命名为TIA/EIA-422-A标准,全称是“平衡电压数字接口电路的电气特性”RS-422标准。RS-422由 RS-232发展而来,改进了 RS-232通信距离短、速率低的缺点,RS-422定义了一种平衡通信接口,数据信号采用差分传输方式,传输速率提高到了10 Mb/s,传输距离延长到约1 200 m,并允许在一条平衡总线上连接最多10个接收器,即一个主设备,其余为从设备,从设备之间不能通信,所以RS-422支持点对多的双向通信。

在现代数字信号处理系统中,为了实现RS-422通信,通常采用DSP(数字信号处理器)+FPGA+外围芯片的电路设计。FPGA是DSP的通信枢纽,DSP若要与RS-422总线上的主设备实现通信,则FPGA将作为DSP与主设备的数据“中转站”,实现RS-422通信数据缓存。

1 传统实现方法

传统的FPGA实现RS-422通信方法采用FPGA+可编程通用异步收发器+差分线路驱动器的硬件电路。FPGA通过软件编程接收可编程通用异步收发器的并行数据或发送并行数据到可编程通用异步收发器。可编程通用异步收发器用于将串行数据转化为并行数据或将并行数据转化成串行数据。差分线路驱动器分两种:一种用于发送,负责接收TTL或COMS输入电平将其转换成差分电平发送给RS-422总线;另一种用于接收,将接收到的RS-422总线的差分电平转换成TTL或COMS输出电平。

本文中以实例来说明传统方法及改进后方法的硬件和软件实现。在实例中,FPGA采用xilinx公司的virtex系列XQR300,逻辑门数为30万门;可编程通用异步收发器采用intersil公司的82C52,差分线路驱动器采用intersil公司的DS26c31和DS26c32。

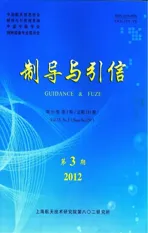

传统实现方法硬件采用XQR300+82C52+DS26c31+DS26c32,其硬件电路实现如图1所示。

图1 传统方法的硬件电路实现图

图1中,XQR300要与82C52的管脚相连,控制82C52的读写、复位、片选与地址译码。82C52的串行数据输入管脚SDI与DS26C32的输出管脚相连,串行数据输出管脚SDO与DS26C31的输入管脚相连,清除发送管脚CTS与DS26C32的输出管脚相连。82C52的时钟来自外部,通过内部的波特率发生器产生和RS-422通信所采用的波特率同步的时钟,这样才能按照RS-422时序要求进行数据的收发。RXD+、RXD-为总线上主设备发来的数据,CTS+、CTS-为总线上主设备发来的清除发送指令,TXD+、TXD-为FPGA发送到主设备的数据。

采用图1的硬件电路实现RS422通信时,在XQR300软件编程时需要用XQR300控制82C52的复位、读写与地址译码。

XQR300的软件接口图,如图2所示。

图2 传统方法的软件接口图

图2中,dsp_rd、dsp_wr为 DSP的读写信号,data_from_dsp为来自DSP的8位并行数据,data_to_dsp为发送到DSP的8位并行数据,rs_sel为 RS-422通信模块片选信号。rs422_rd、rs422_wr为FPGA输出到82C52的读写信号,rs_set为FPGA输出到82C52的复位信号,rs422_cso为FPGA输出到82C52的片选信号,DR为82C52输出到FPGA的数据准备好信号,TBRE为82C52输出到FPGA的发送缓存器为空信号,RS_DATA_IN为82C52发送到FPGA的8位并行数据,RS_DATA_OUT为FPGA发送到82C52的8位并行数据。FPGA在内部开辟了一个发送FIFO和一个接收FIFO,FIFO1为接收FIFO,接收82C52的并行数据,FIFO2为发送FIFO,通过82C52发送数据到主设备。

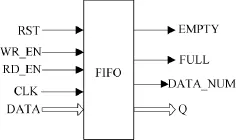

FIFO(First In First Out)可以储存、缓冲两个异步时钟之间的数据传输,是一种先进先出存储器,具有两套数据线而无地址线,可在其一端写操作而在另一端进行读操作,数据在其中顺序移动,从而达到较高的传输速度和效率[3]。FIFO模块图如图3所示,RD_EN、WR_EN为读写使能信号,CLK为时钟,DATA为8位并行数据输入,Q为8位并行数据输出,EMPTY为FIFO空标志,FULL为FIFO满标志,DATA_NUM为内部数据数,RST为复位信号。

图3 FIFO模块图

FPGA首先完成82C52的初始化,然后自主地查询82C52的状态,在它接收Buffer有数据时将数据读入并存储到对应的接收FIFO中;查询FPGA内部发送FIFO的状态,若发送FIFO有数据且82C52的发送Buffer为空,将发送FIFO的数据读出写入发送Buffer。在DSP选通FPGA的RS-422通信模块时,将FIFO中的数据送入DSP或将DSP的数据写入FIFO。

2 改进实现方法

传统的实现方法中,可编程通用异步收发器一般引脚较多,内含许多辅助模块和一些辅助功能,在实际使用时往往用不到这些功能,基本的通信只需要接收和发送两条信号线,因此若采用专用芯片,将会使电路变得复杂,面积增大,从而导致成本增加,系统的稳定性和可靠性降低。

由于FPGA的功能日益强大,开发周期短,可重复编程等优点也越来越明显,因此可以在芯片上集成可编程通用异步收发器的功能,从而简化了电路,提高了可靠性、稳定性和灵活性。因此,改进后的方法仅采用FPGA+差分线路驱动器的硬件电路。FPGA直接与差分线路驱动器实现数据交换。

因此,硬件仅采用XQR300+DS26c31+DS26c32,其硬件电路实现图如图4所示。

图4 改进方法的硬件电路实现图

从图4可以看出,FPGA只需用两个IO管脚接收发送数据,SDI与DS26C32的输出管脚相连,接收主设备的422串行通信数据,SDO与DS26C31的输入管脚相连,发送串行通信数据到主设备。

采用如上硬件电路实现RS-422通信时,在XQR300软件编程时需在XQR300芯片上集成异步收发功能模块,即要在XQR300内部实现数据串并转换和并串转换,并在XQR300上实现波特率发生器的功能。

改进的实现方法的软件接口图,如图5所示。

图5 改进方法的软件接口图

图中,have_data为接收FIFO的空标志,dsp_rd、dsp_wr为 DSP的读写信号,data_from_dsp为来自DSP的8位并行数据,data_to_dsp为发送到DSP的8位并行数据。rxd为主设备送入的RS-422串行数据,txd为发送到主设备的串行数据。

FPGA在内部开辟了一个发送FIFO和一个接收FIFO,FIFO的结构与图3相同,接收FIFO用于接收主设备的数据,发送FIFO用于发送数据到主设备。发数时DSP先将要发送的8位并行数据写入发送FIFO,然后在内部时序控制下,FPGA将FIFO中的8位并行数据一位一位的发送出去。当rxd为0,表示数据起始位到达,FIFO准备接收主设备RS-422的数据,采用1个8 bit的寄存器来缓存主设备起始位后的8位数据,若奇偶校验位正确且停止位正确,则将此数送到接收FIFO中。

DSP周期性查询接收FIFO的非空标志have_data,空标志为“1”即有数据时,DSP将接收FIFO中的数据读出;当DSP需要发送数据到主设备时,DSP将数据写入对应的发送FIFO,然后在时钟的控制下把数据发送出去。

3 结论

改进方法与传统方法相比,硬件设计上不需要使用可编程通用异步收发器,直接通过FPGA的软件编程实现可编程通用异步收发器的功能,减少了芯片的使用种类,减小了印制板的面积,节约了开发成本;软件设计上软件接口简单,控制信号减少,降低了软件编程复杂度和难度[2]。

[1] 贾豫东,封吉平.用FPGA实现任意波形发生器的两种方法[J].计算机测量与控制,2004,(12):895-897.

[2] 葛纫龙,韩宇龙.嵌入式应用系统设计[M].北京:高等教育出版社,2008.

[3] 张 雪,徐晓苏,张国龙.基于DSP和FPGA的高速串行通信系统设计[J].舰船电子工程,2009,(5):66-69.