一种异步FIFO的Read/Write Data Flow Through功能测试方法∗

2019-05-07张晓羽

张晓羽

(航天科工防御技术研究试验中心 北京 100854)

1 引言

目前可编程逻辑器件[1~2]越来越广泛,种类也越 来 越 多 ,基 于 SRAM[3~4](Static Random Access Memory)工艺和基于 FIFO[5~6](First Input First Out⁃put)工艺都有广泛的应用。前期已经对SRAM和FIFO做了大量的技术研究和测试程序攻关工作。

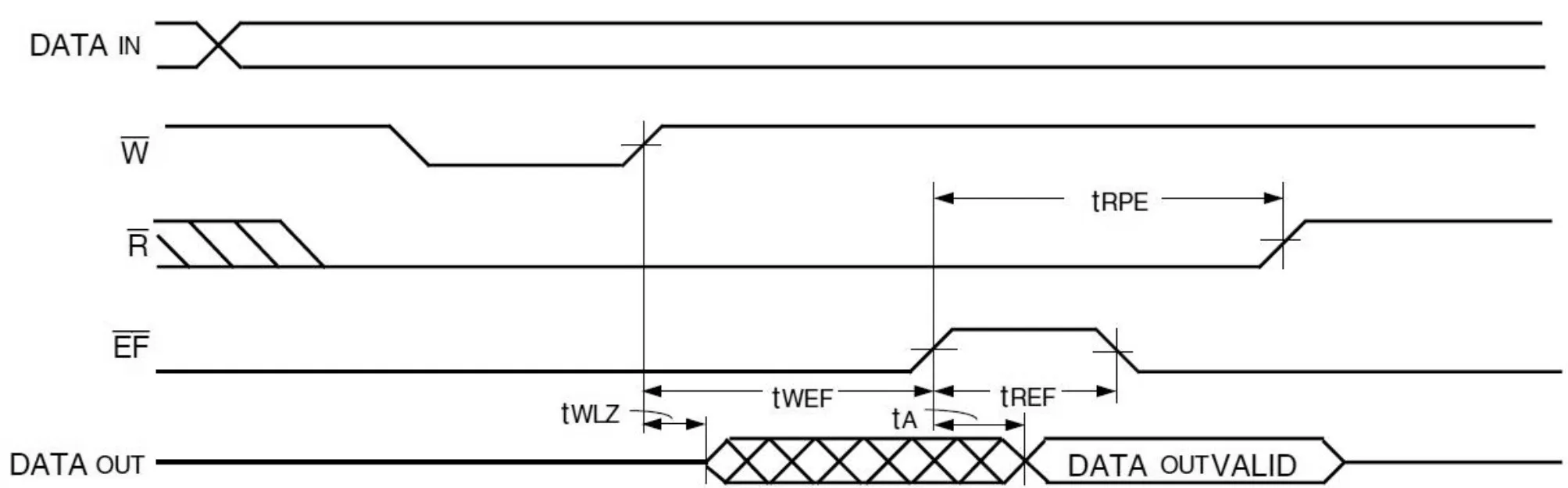

某些异步FIFO具有Read Data Flow Through功能和Write Data Flow Through功能。对于Read Da⁃ta Flow Through模式,在向空存储器写入一个数据后允许立刻将该数据读出,在此期间,----EF管脚信号会有一个脉冲。对于Write Data Flow Through模式,在从满的存储器中读出一个数据后允许立刻写入一个数据,在此期间----FF管脚信号也会有一个脉冲。

目前对Read Data Flow Through功能测试及Write Data Flow Through功能测试关注甚少,因此需要对Read Data Flow Through功能测试以及Write Data Flow Through功能测试进行一定的深入研究。有鉴于此,本文提出了一种异步FIFO特殊功能测试方法,用以完成对于异步芯片的Read Da⁃ta Flow Through功能和Write Data Flow Through功能的测试。

2 测试原理

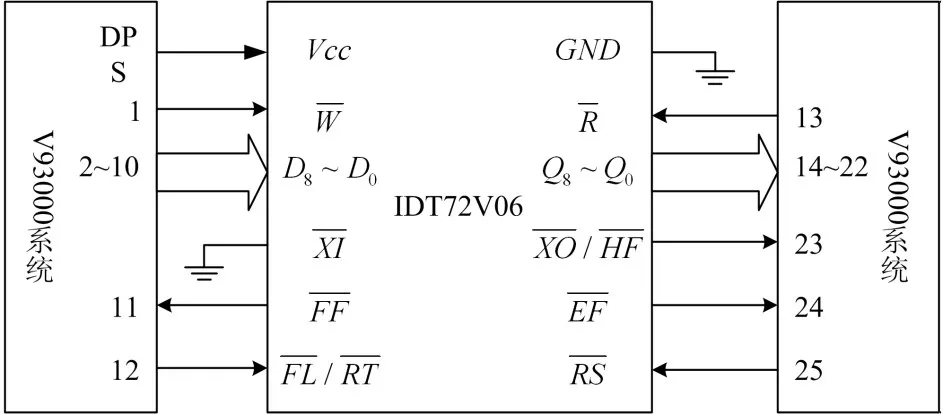

本文以具有Read Data Flow Through功能与Write Data Flow Through功能的异步FIFO芯片IDT72V06为例,采用V93000测试系统[7~9]对其进行测试。图1为用于特殊功能测试的测试平台连接图。DPS为V93000系统的电源通道,管脚1~25为V93000系统的数字通道。V93000系统的DPS给芯片IDT72V06的Vcc管脚提供电源电压,V93000系统的数字通道给芯片IDT72V06的Wˉ、D8~D0、管脚提供输入信号,芯片IDT72V06的管脚输出信号到V9300-0---系统的数字通道以供其采样,芯片IDT72V06的XI和GND管脚接地。需要注意的是,本文采用了V93000测试系统进行说明,但并不限于V93000测试系统,采用其他测试系统也可实现该测试方法,并且该测试方法可应用于其他类似芯片。

图1 用于异步FIFO特殊功能测试的测试平台连接图

在具体的调试过程中发现Read Data Fl--o-w-Through模式与Write Data Flow Through模式下EF管脚和管脚的脉冲宽度很窄,导致在较短时间内即需要重新调整参数重新测试,使测试时间延长,测试效率降低,不便于通用性测试。故本文通过功能测试与交流参数测试相结合的方式完成以上两种功 能的测试:在功能测试[10~12]中,测试 管脚和 管脚在脉冲之后的低电平部分;在交流测试[13~15]中,测试 管脚和 管脚脉冲的高电平部分。

测试管脚和管脚在脉冲之后的低电平部分的测试原理为:对于Read Data Flow Through模式,向空存储器写入一个数据后立刻将该数据读出,此时看到Q8~Q0管脚在的上升沿之后的(t+t)ns有数据输出,且管脚信号有一个脉WEFA冲,即先由低电平变为高电平再由高电平变为低电平;对于Write Data Flow Through模式,从满的存储器中读出一个数据后立刻写入一个数据,在Wˉ的上升沿时刻,新数据经由D8~D0管脚被写入FIFO中,此时也有一个脉冲,即先由低电平变为高电平再由高电平变为低电平。将管脚与管脚的采样时 刻选择在脉冲之后,此时采集到的管脚与管脚信号为低电平。

图2 Read Data Flow Through功能时序图

图3 Write Data Flow Through功能时序图

3 测试方法实现

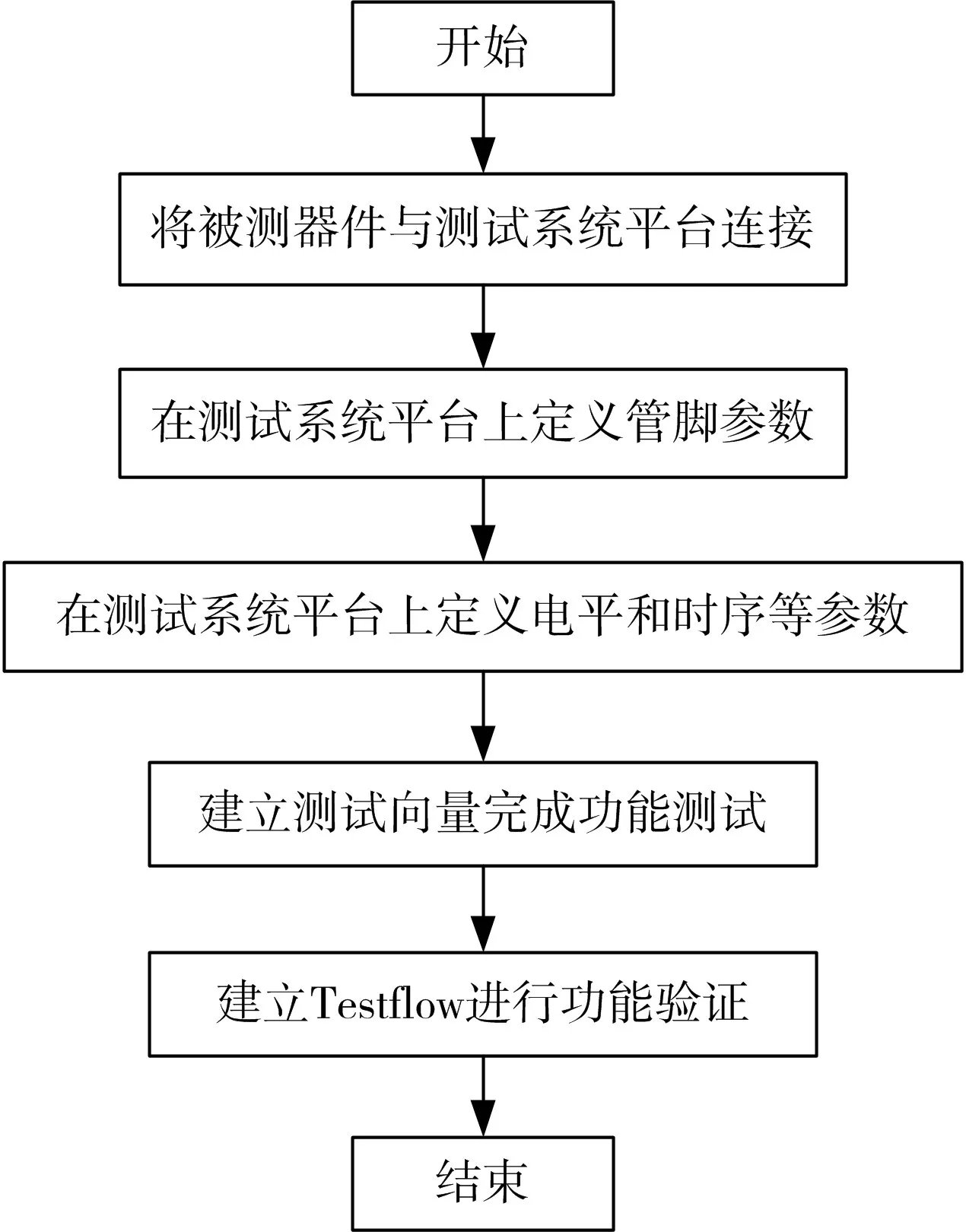

基于上述测试原理,本文提出了一种异步FIFO的Read Data Flow Through和Write Data Flow Through功能测试方法。图4所示为异步FIFO的Read/Write Data Flow Through功能测试方法的流程图,其包括以下步骤:

Step1:将被测器件包括电源信号管脚、输入信号管脚、输出信号管脚在内的所有管脚与测试系统连接。

Step2:在测试系统平台上为被测器件定义相关管脚参数,包括在数字引脚设置中定义除电源管脚外的所有管脚的相关参数,以及在DPS管脚设置中定义电源管脚相关参数。其具体方法为:在Pin Settings中的Digital Pins中定义除电源管脚外的所有管脚的包含Name、No、Type及 Tester Channel在内的所有相关参数,在DPS Pins中定义电源管脚的包含Name、Polarity及Tester Channel在内的所有相关参数,并选择相应的DPS Channel Mode。

Step3:在测试系统平台上定义能满足功能测试与交流参数测试的包括电源电平、输入脉冲电平在内的相关电平参数以及包括访问时间、采样时刻在内的相关时序参数,并为相关参数赋值。其中电平参数的定义与赋值的方法包括:在Level中的Equation 中建立 EQNSET 1“Functional”,在 EQN⁃SET 1“Functional”中定义 SPECS和 LEVELSET 1“With_load”;在SpecTool中建立多个Levels Specifi⁃cation,包含 VCCnorm、VCCmin、VCCmax以及 ACt⁃est,并给相应的Levels Specification赋值,其赋值需满足芯片功能测试要求与交流参数测试要求。在功能测试中时序参数的定义与赋值的方法包括:在Timing中的 Equation中建立 EQNSET 1“timing equation set”,在 EQNSET 1“timing equation set”中定义SPECS和TIMINGSET 1“Functional”;在Wave Tables中 建 立 WAVETBL“wave table name”;在SpecTool中建立Timing Specification(分别名为Read Flow Through和Write Flow Through),并给相应的Timing Specification赋值,参数定义与赋值需满足对被测器件进行功能测试的要求。在交流参数测试中时序参数定义与赋值的方法包括:在EQNSET 1“timing equation set”中定义 TIMINGSET 2“tA”,令管脚的采样时刻等于Wˉ管脚上升沿时刻加上t,令管脚的采样时刻等于Rˉ管脚WEF上升沿时刻加上tRFF;在SpecTool中建立Timing Specification,参数设置需满足交流参数测试要求。

Step4:建立Read Data Flow Through模式和Write Data Flow Through模式的测试向量,在功能测试中测试 管脚和 管脚在脉冲之后 的低电平部分;在交流测试中测试----管脚和----管脚脉冲的高电平部分。测试EF管脚和FF管脚在脉冲之后的低电平部分的具体方法为:建立测试向量,对Read Data Flow Through模式与Write Data Flow Through模式下的功能进行模拟,并将两种模式下 管脚与 管脚的采样时刻设置在脉冲之后,测试管脚与管脚在脉冲之后的低电平部分。本文采用Spec Search方法测试交流参数tWEF和 tRFF,从而验证 Read Data FlowThrough 和Write Data Flow Through两种模式下和两个管脚信号脉冲的高电平部分。Spec Search方法按照给定的交流测试电平、时序及向量,扫描被测交流参数的不同值得到使相应的向量由PASS到FAIL或者由FAIL到PASS的临界值,临界值即为交流参数tWEF和tRFF的值。Spec Search的扫描方法为线性方法,步长为0.1 ns。

Step5:建立测试流程(Testflow),对Read Data Flow Through模式与Write Data Flow Through模式进行功能验证。其中功能测试分别在最小电源电压、典型电源电压、最大电源电压下进行,其测试方法为 ac_tml.AcTest.Functional Test;对 Read Data Flow Through模式下交流参数tWEF与Write Data Flow Through模式下交流参数tRFF的测试,其测试方法为ac_tml.AcTest.Spec Search。

图4 Read/Write Data Flow Through功能测试方法的流程图

4 结语

本文提供的测试方法实现了对异步FIFO芯片的Read Data Flow Through功能测试及Write Data Flow Through功能测试,并验证了Read Data Flow Through和Write Data Flow Through两种模式下和两个管脚的相关功能,提高了测试覆盖率,为具备该功能的异步FIFO测试开发奠定技术基础。同时在测试过程中减少了测试时间,提高了测试效率和测试通用性。