猝发式直扩系统伪码同步技术的FPGA实现

2012-11-26张福洪朱小辉吴铭宇易志强

张福洪,朱小辉,吴铭宇,易志强

(杭州电子科技大学通信工程学院,浙江杭州310018)

0 引言

在扩频通信系统中,由于收发端时钟漂移,电波传输时延,多径效应,多普勒效应等因素的影响,使接收机不能确定接收扩频序列的相位[1]。根据扩频序列的相关特性,相位误差的存在会造成系统处理增益的损失,从而限制了扩频系统最大限度地发挥其应有的抗干扰能力[2]。在短时猝发式扩频通信系统中,为提高扩频增益,猝发信号被高速长扩频序列扩频调制后,在极短时间内以猝发形式被高速发送,对序列同步提出了更高的要求。本文根据猝发信号体制的特殊性,基于扫频、数字匹配滤波器和数字延迟锁定跟踪环,提出了一种适用于长扩频码、大频偏情况的直扩接收机伪码同步方案,能够在低信噪比条件下,实现扩频序列同步。

1 伪码同步方案分析

伪码同步流程图如图1所示。伪码同步包括伪码捕获和伪码跟踪。由于多普勒效应对相关峰检测的影响,伪码捕获必须伴随频率捕获的完成而实现扩频序列的粗同步;伪码捕获完成后,码跟踪则自动调整本地序列相位,使本地伪码和接收信号的伪码相位保持精确同步。

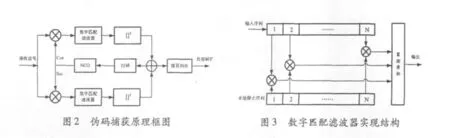

1.1 伪码捕获

高动态环境下,由于载波多普勒效应的存在,实现伪码捕获需要在一个时域和频域构成的二维平面同时进行搜索。对多普勒效应的搜索可以将频率捕获范围分成多个区间串行或并行搜索完成;对码相位的搜索可以利用伪码的相关性通过相关运算完成码元搜索。伪码捕获原理框图如图2所示,I路伪码对I、Q两路数据进行滑动相关解扩,匹配滤波器输出的相关峰值为[2]:

图1 伪码同步流程图

式中,Tc为码片间隔,R(τ)为伪码相关函数,Δf为频差,N为扩频码长度。

为实现非相关解扩,本地伪码与接收信号的码相位必须小于一个码片宽度,使相关峰检测量高于码捕获判定阈值,以实现伪码捕获。由式1可知,相关峰检测量对载波多普勒效应敏感,当频偏增大时,相关峰值迅速减小;而当频偏值等于Rs/2(符号率)时,相关峰值仅下降3dB。由此可见,多普勒效应在Rs/2以内时[3]。可以满足伪码粗同步要求。对于频偏的修正,主要通过扫频加复FFT来完成[4]。扫频完成后将频偏限制在Rs/2以内,然后启动解扩,将I,Q路解扩数剧进行一次复FFT,完成将频偏减小至几百Hz。本方案中伪码捕获采用扫频和数字匹配滤波器相结合的实现结构[5]。扫频在±30kHz的频率捕获范围内,采用第一轮粗扫,第二轮细扫的方法,取相关峰值最大时的频点作为捕获频点,从而将频差缩小到[-Rs/4,+Rs/4]范围内以完成频率粗捕;后者则以静止的本地伪码作为匹配滤波器系数,接收信号依次滑过本地伪码,每个时刻都产生一个相关值,当两个序列相位对齐时,相关值达到最大。若某时刻相关峰值大于预设捕获门限,则表明此时伪码捕获成功,并记录此时码位置,开始解扩数据。匹配滤波器结构如图3所示。

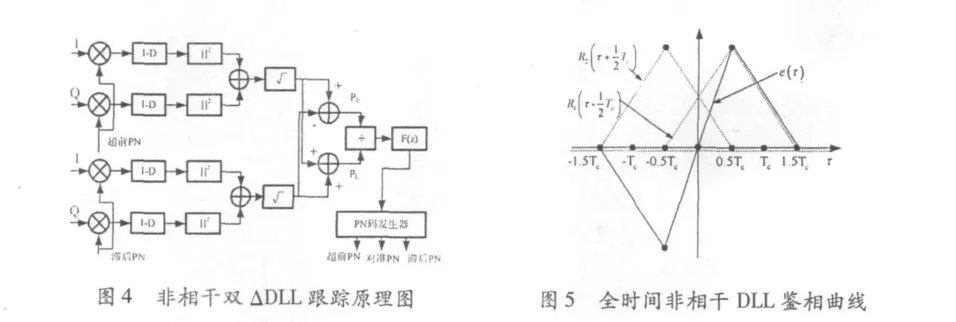

1.2 伪码跟踪

伪码捕获完成后,本地伪码和接收伪码相位并未完全对齐而存在残余相差,而且已同步伪码也会因为噪声污染、信道变化而出现相位抖动偏差。因此,扩频系统为了确保伪码同步保持,必须对伪码锁相跟踪。本方案中伪码跟踪采用非相干双ΔDLL跟踪算法,伪码跟踪原理图如图4所示。在Costas环路中,数字下变频器所产生的同相I、正交Q两支路信号被送入DLL环路,分别和本地超前伪码和滞后伪码进行相关运算和数据累加。分别将两路相关累加值进行平方和运算后再取其平方根运算,并得到超前累计值PE和滞后累计值PL。根据伪码自相关特性,将超前PE、滞后PL两支路相关特性相减,得到鉴相特性曲线如图5所示,在-0.5~+0.5Tc之间鉴相特性具有较好的线性关系。实际信号接收中,为保证输入功率变化时,误差不受影响,采用L+E除L-E使其归一化,使该归一化值作为伪码相位误差信号输入延迟锁定环的鉴相器,并经过环路滤波后控制本地伪码时钟,从而完成伪码的精确跟踪[6]。

非相干双ΔDLL跟踪算法鉴相函数为:

式中,IE,QE为接收信号与超前伪码相关累加值,IL,QL为接收信号与滞后伪码相关累加值,PE为超前累计值,PL为滞后累计值。

2 伪码同步方案实现

系统采用DQPSK调制方式,频率捕获范围为±30kHz,数据采用3帧间发方式,每帧长度为300个符号。硬件实现基于FPGA平台,采用ALTERA公司StratixⅡ系列中的EP2S90F78014芯片,使用QuartusⅡ软件设计实现,并通过EDA软件SignalTap II工具实时捕获和显示实际信号,完成算法验证。

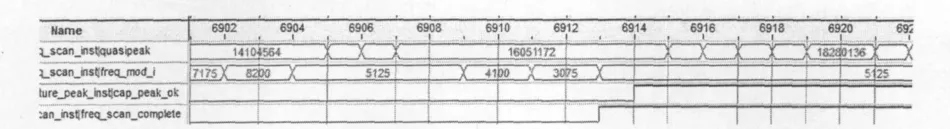

如图6所示,当伪码相关值较之前增大时,其值由quasipeak寄存。当没有信号进入时,quasipeak输出值较小。未能达到次轮细扫的阈值要求,因此频率控制字freq_mod_i修改本地NCO的频率,以固定的频率步进,不断来回扫描首轮5个频点。

图6 扫频过程

如图7所示,当有信号进入接收机时,quasipeak增大且达到次轮扫频阀值,则进入次轮细扫。次轮扫频完成后,freq_scan_complete置位,freq_mod_i此时保持5 125不变,以锁定捕获频点,此时相关峰值quasipeak较前明显增大。当实时相关值达到伪码捕获阈值,即自相关最大值的0.75时,表明伪码捕获完成,同时捕获标志cap_peak_ok置位,并记录此时伪码相位,开始解扩数据。

图7 伪码捕获过程

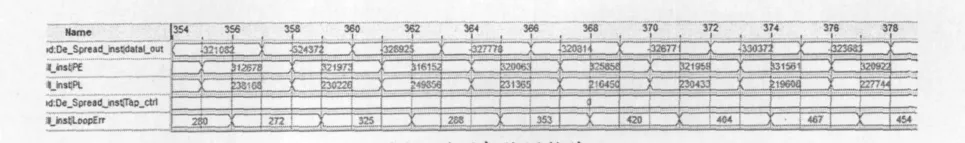

码相位即使刚开始时是对齐的,但是随着时间的推移,相位会逐渐产生偏差。如图8所示,环路滤波器输出的相位误差值LoopErr呈现增大趋势,表明接收信号和本地伪码相位已经产生了偏差。方案设定LoopErr大于阈值15 400时,Tap_ctrl置2,调整本地伪码提前一个时钟;当LoopErr小于阈值-15 400时,Tap_ctrl置1,调整本地伪码时钟延迟一个时钟。在LoopErr没有达到相位调整的阈值前,Tap_ctrl一直为零,不进行码相位调整。

图8 伪码相位调整前

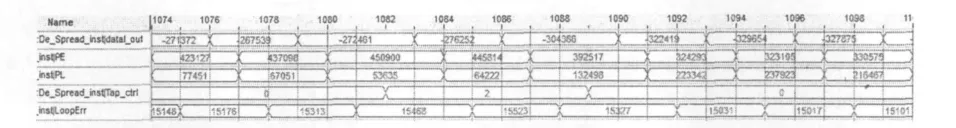

在解扩模块中,由于I,Q两路信号中每个扩频码片被采样了8次,所以本地产生的伪码需要保持8个时钟。可以通过调整本地伪码的保持时钟数,来达到调整码相位的作用。当Tap_ctrl为2时,使本地伪码保持计数器counter由正常的加1,变为2来达到本地伪码提前一个时钟的作用。当Tap_ctrl为1时,使本地伪码保持计数器counter由正常的加1,变为保持当前计数值来达到本地伪码延时一个时钟的作用[7]。如图9所示,由于伪码相差不断增大,数据解扩值dataI_out下降到270 000左右。当伪码相位误差LoopErr达到阈值15 400时,Tap_ctrl置2,调整本地伪码提前一个时钟。相位调整后发现,超前累计值PE变小,滞后累计值PL变大,值的变化趋势与理论上一致,并且dataI_out增大到320 000左右,证明伪码跟踪环有效工作。对于LoopErr的阈值,需要结合实际情况进行设定,不同信道下,随着时间的推移,相位偏差的快慢程度不一样。

图9 伪码相位调整后

经伪码跟踪后的I路解扩数据输出如图10所示。通过若干次伪码相位调整,相位误差始终在阈值上下抖动,并且3帧间发数据中导频符号和有效数据在图10中清晰可见,表明伪码跟踪正常,有效证明了伪码同步方案的可靠性和可行性。

图10 码跟踪全过程

3 结束语

本文结合猝发式直扩系统项目要求,利用扫频、数字匹配滤波器和数字延迟锁定环实现了大频偏下伪码的精确同步,捕获时间较短。通过Verilog编程下载和利用EDA软件SignalTap II工具实时捕获和校验数据,验证了本文提出的伪码同步算法方案的可行性。

[1] 常娥.猝发性扩频信号的同步技术研究[D].大连:大连理工大学,2003.

[2] 陈亮.便携RAKE接收技术的研究及FPGA实现[D].西安:西安电子科技大学,2006.

[3] 夏荥.高动态直扩信号载波同步技术[D].成都:电子科技大学,2008.

[4] 王颖.数字通信系统中频偏估计技术的研究[D].南京:南京理工大学,2011.

[5] Yen Nan-Yang,Su Szu-Lin.Robust Matched-Filter Acquisition for Direct-Sequence Ultra wideb and Systems[J].IEEE Transactions On Vehicular Techology,2009.58(8):4 419 -4 425.

[6] 张欣.扩频通信数字基带信号处理及VLSI实现[M].北京:科学出版社,2004:216-224.

[7] 孟明,许家栋,韦高.直扩系统伪码捕获和跟踪的FPGA实现[J].现代电子技术,2001.34(17):119-121.