基于FPGA的平方根升余弦滤波器设计

2012-10-20张松轶

张松轶

(河北远东哈里斯通信有限公司,河北石家庄 050200)

0 引言

TETRA是欧洲电信标准协会ETSI指定的数字无线电集群通信标准。TETRA系统可以提供集群、非集群通讯,支持话音、电路数据、短信息和分组数据等业务的直接模式通信,同时还支持多种附加业务。该系统以频谱资源利用率高、保密性好、覆盖范围广以及语音质量高等特性,在全球得到了广泛的应用。

在数字通信系统中需要在信号发射前对频谱较宽的基带信号进行成形处理,改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率。

1 总体设计

在现代数字通信系统中,由于基带信号的频谱范围较宽,为了让信号在带限信道中传输,需要在发送端把信号进行带宽限制,由此引入码间干扰(ISI)。为了使传输误码率足够小,必须最大限度地减小码间干扰。消除码间干扰可以通过要求传输信号在特定时刻的波形幅值无失真来实现,而不必要求整个波形无失真。

TETRA数字集群通信系统中,为了消除码间干扰,采用了滚降系数 α=0.35的平方根升余弦(SRRC)滤波器作为发射成形滤波器[1,2]。

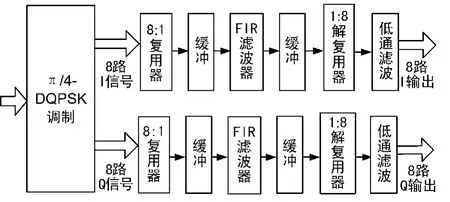

在FPGA实际设计中,在一片FPGA内完成8个载波的成形滤波,所以需要实现16个8倍内插的SRRC成形滤波器,其中,每个载波需要2个滤波器,分别用于同相/正交(I/Q)支路。为了节省FPGA内部资源,将I/Q支路滤波器分别实现成一个8路复用的FIR滤波器,相应的滤波器处理主时钟需要18 kHz×8×8=1152 kHz。此外,为了满足TETRA系统对调制邻道发射功率的要求,还需要经过严格按照TETRA协议对调制邻道发射功率的要求的内插低通滤波器,实现框图如图1所示。

图1 TETRA SRRC滤波器设计框图

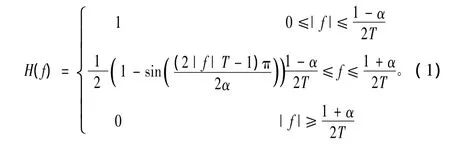

根据奈奎斯特第一准则,若信道传输函数H(f)=HT(f)·HC(f)·HR(f)的幅频特性满足滚降系数为α的升余弦(RRC)滤波器特征时,可以实现无码间串扰传输,从而降低对接收侧采样时钟精度的要求。RRC滤波器的传输函数如下所示:

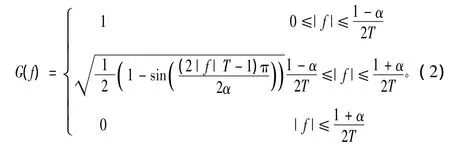

当信道噪声可忽略时,取HC(f)≈1。按照匹配滤波器的输出信噪比最大准则,可以将上述RRC滤波器分为2个SRRC滤波器来实现:一个在发射端用于发射成形滤波,频率响应为HT(f),另一个在接收端用于匹配滤波,频率响应为HR(f),则有H(f)≈HT(f)·HR(f),其中:HT(f)=HR(f)=G(f)。

归一化的SRRC滤波器的系统函数如下所示:

在式(2)中,α为滚降系数,定义为 α=fα/f0。由上式可知0≤α≤1,α越大,频谱在截止频率处越光滑,而频带利用率越低。T=1/Rs为符号周期,滤波器的绝对带宽B为:

按照TETRA协议的规定,TETRA系统中使用的成形滤波器滚降系数α=0.35,系统传输符号速率为 Rs=18 kHz,相应的滤波器绝对带宽为24.3kHz。

2 需解决的问题

2.1 窄带调制频带限制

TETRA数字集群通信系统属于窄带数字通信提供,系统信道带宽只有25 kHz,而系统数据传输速率为36 kbps。TETRA数字集群通信系统采用π/4偏移差分相移键控(π/4-DQPSK)调制方式,从图2所示的π/4-DQPSK调制相位转换图中可以看出,调制相位的转换是瞬间完成的,而这种相位的瞬间跳变,必然会导致基带信号频谱的大幅度扩展。宽频基带信号在窄带信道中进行传输,会引入严重的码间干扰。

图2 π/4-DQPSK调制相位转换图

2.2 TETRA邻道干扰要求

TETRA标准对于TETRA系统中发射机的对相邻道的干扰(ACI)指标要求很高:在第1邻道(载频的±25 kHz偏移)处,要求调制邻道功率不得高于-55 dBc;在第2邻道(载频的±50 kHz偏移)处,要求调制邻道功率不得高于-65 dBc。

为了满足TETRA系统关于邻道干扰的要求,除了保证调制器矢量调制精度符合要求,射频前端使用线性化功率放大器,还要求对基带信号进行精确的滤波。

2.3 滤波器阶数和数据定点化

符合要求的SRRC成形滤波器的时域表达式如式4所示,可以看出SRRC滤波器是一个无穷阶数、系数对称的FIR滤波器。

在实际应用中,不能采用上述理论上的无穷阶数FIR滤波器,必须要根据实现方式和资源占用情况,截取滤波器的一部分阶数使用,成型滤波器的截取阶数对滤波器的性能有很大影响[3]。

由于FPGA实现时必须采用定点信号处理算法,所以对于滤波器系数计算必须要合理量化为有限长二进制小数。需要考虑量化误差对频率响应的影响,在满足频谱要求的前提下尽可能减少量化比特数[4]。

3 关键技术

3.1 SRRC参数设计

SRRC滤波器性能参数的设计对调制器性能是否满足频谱要求影响很大(包括频带内的平坦度和带外的抑制)。在实际SRRC滤波器的设计中,具体考虑因素有:滤波器的阶数、滚降系数、加权窗和相关码元个数等。

SRRC滤波器阶数可以用N=L×K表示,其中L表示每个符号的取样点数,K表示相关码元个数,是考虑最佳采样点处受影响的码元个数。相关码元个数越多,成型滤波器的性能越好,最佳采样点处的码间干扰越小,同时滤波器旁瓣抑制越好,而且过渡带越陡,输出信号的功率谱特性越好[5]。

在实现中,对限定阶数的SRRC滤波器的实现是在理论的时域表达式上加窗。为了获得较大的阻带衰减,要求窗函数最大的旁瓣相对于主瓣应该尽可能小。实际要求成形后信号频谱在第1旁瓣一般应该衰减在40dB以上,通常选用汉明(Hamming)窗。

按照TETRA协议的要求,经过仿真优化,设计的平方根升余弦滤波器采用滚降系数α=0.35,滤波器阶数为49阶,数据符号速率为18 kHz,数据采样速率为144 kHz,相关码元个数为6个码元。

此SRRC滤波器的冲激响应如图3所示。

图3 TETRA系统中SRRC滤波器的冲激响应

经过上述成型滤波器的发射信号,为了满足TETRA系统对调制邻道发射功率的要求,还需要经过严格按照TETRA协议对调制邻道发射功率的要求的低通滤波器,由于系统的信息速率为36 kbps,所以采用截止频率为10.5 kHz左右。数字低通滤波器的阶数决定了其边带信号的抑制度,同时还需要考虑对实现的算法复杂度进行折中选择,在基带信号中得到良好的带外抑制效果。

3.2 基于FPGA的FIR滤波器设计实现

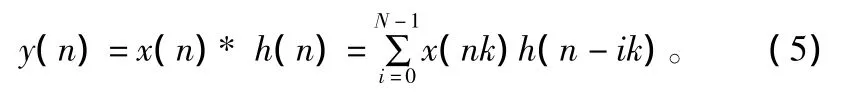

N阶FIR滤波器输出对应于输入时间序列x(n)的关系由有限卷积数量的形式给出:

式中,N为滤波器的阶数,h(n)为滤波器的系数。采用直接型8倍升采样FIR成型滤波器FPGA实现原理框图如图4所示。

图4 升采样FIR滤波器原理

在实际FPGA设计中FIR滤波器采用脉动阵列架构。由于SRRC滤波器系数是对称的,对称部分的系数可以进行合并。为了防止溢出的产生,对于运算产生的结果采用截取高位的方法来完成[6]。

在FPGA的实际实现中,使用了赛灵思(Xilinx)公司的工具软件System Generator,采用此工具可以在Simulink软件环境中建立模型并进行仿真,还可以根据建立的模型产生对应的VHDL文件或NGC网表文件。将生成的网表文件导入ISE软件中进行布局布线,生成Bit文件,写入Spartan-3A DSP系列XC3SD1800ADSP FPGA,完成设计实现。

4 仿真结果分析

使用Simulink软件对设计的SRRC滤波器进行仿真分析,仿真得到的TETRA标准π/4-DQPSK基带信号经过平方根升余弦滤波器后的相位转换图如图5所示。

图5 信号经过SRRC滤波器后的相位转换图

由图5可知,相位转换已经不存在瞬间转换的情况,同时在最佳采样点处,相邻码元不存在码间串扰。

自行编写测试向量对System Generator软件生成的网表文件经过布局布线后在Modelsim软件中进行仿真,滤波器的冲激响应结果时域波形如图6中数据输出信号所示。

图6 SRRC滤波器Modelsim仿真图

5 结束语

基于FPGA按照该方法设计的SRRC滤波器,具有运算速度快、结构简单和资源占用少的优点,完全可以满足TETRA标准要求的成形滤波功能要求,具有较强的先进性和实用性。目前该设计已经应用于TETRA数字集群基站设备中。在目前国外TETRA设备完全占领中国市场的情况下,为国内TETRA技术的发展,起到了重要的作用。随着国产TETRA市场份额的壮大,必将得到更为广泛的应用。

[1]ETSI EN 300 392 -2 TerrestrialTrunked Radio(TETRA);Voice plus Data(V+D);Part 2:Air Interface(AI)[S].

[2]郑祖辉,陆锦华,丁锐,等.数字集群移动通信系统[M].北京:电子工业出版社,2008:375-382.

[3]张维良,郭兴波,潘长勇.平方根升余弦滚降FIR数字滤波器的设计[J].电讯技术,2002(6):51-55.

[4]陈东华.升余弦滚降基带成形内插滤波器的FPGA实现[J].华侨大学学报:自然科学版,2006,27(3):310-312.

[5]常疆.数字集群系统无线传输链路关键技术的研究[D].黑龙江:哈尔滨工业大学,2005.

[6]张建伟,展雪梅.FIR数字滤波器的设计与实现[J].无线电工程,2010,40(6):54-56.