一种新颖的逻辑分析仪设计方法

2012-10-09贾进滢安鹤男

贾进滢,安鹤男

(深圳大学电子科学与技术学院,广东深圳518000)

本系统采用FPGA的软硬件知识,在一块FPGA芯片里完成了时钟产生模块、频率测量模块、频率显示模块、采样触发控制模块、双口RAM存储模块、波形显示模块、VGA显示驱动模块、采样频率控制模块以及键盘显示控制模块的设计.

具有集成度高、抗干扰能力强、数据通道多、存储容量大等优点[1-5].本系统最大的亮点在于除了能对数字信号进行分析外还可以同时测量被分析数字信号的频率,采用等精度测频技术,大大提高了被分析数字信号频率的测量精度.同时由于FPGA芯片中存在锁相环(PLL)模块,通过倍频技术,可以提高对数字信号频率的测量范围.

传统的设计方案采用单片机与CPLD为核心,这样做的缺点在于由于模块与模块之间的连接会引入干扰信号,这些干扰信号可能会导致系统对被测信号造成错误的分析.为了避免这些问题,提出了一种新的设计方法.将所有模块集成在一块FPGA芯片中,这样解决了外界对被测信号的影响[6-7].

1 系统总体设计

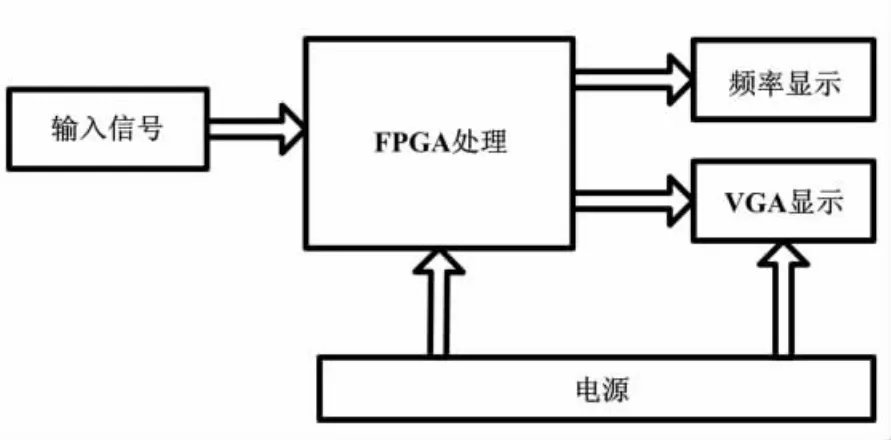

系统主要包括时钟产生模块、测频模块、频率显示模块、采样触发控制模块、双口RAM存储模块、波形显示模块、VGA显示驱动模块、采样频率控制模块以及键盘显示控制模,共9个模块.按功能可划分为三个部分,即信号采样部分、波形显示部分和键盘控制部分.当触发条件满足时,信号采样部分会对输入信号进行采样并存储;波形显示部分只管从双口RAM读出数据并往VGA接口显示;键盘显示部分主要是控制更改触发条件、采样频率及数码显示等操作.基于FPGA的简易逻辑分析仪系统设计如图1所示.

图1 简易逻辑分析仪总体结构框图Fig.1 The overall block diagram of the simple logic analyzer

2 系统硬件设计

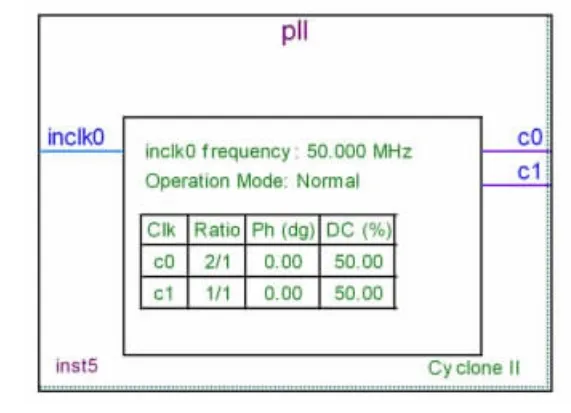

2.1 时钟电路产生模块

外部晶振产生时钟信号,经过FPGA内部的锁相环(PLL)模块对信号进行处后提供给其它模块,锁相环(PLL)模块的设计如图2所示.

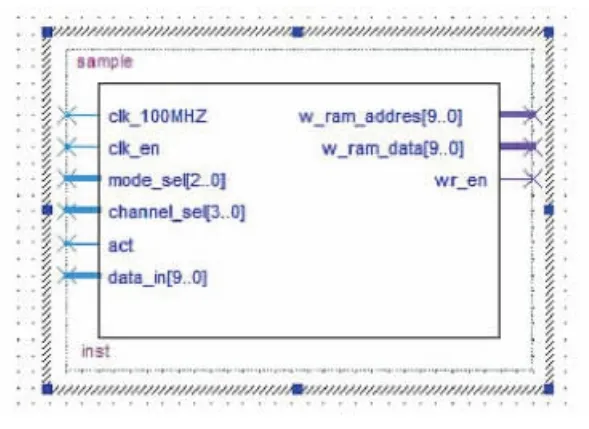

2.2 采样触发控制模块

本设计的逻辑分析仪的双口RAM的存储深度只有1 KB,在工作时只能存储部分数据,当逻辑分析仪需要观察大量数据时,就需要设置观察的起点、终点或者是与被分析数据有一些关系的点作为一个参考点.当特定的数据出现时,逻辑分析仪开始触发,将这些有关的数据流存入存储器.采样触发控制模块设计如图3所示.

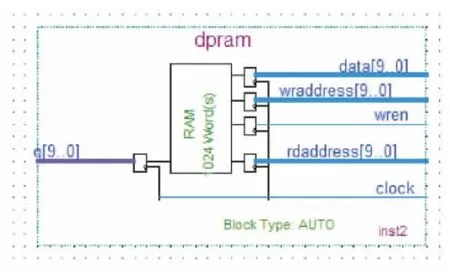

2.3 双口RAM存储模块

双口RAM存储器可实现不同传输方式的双路高速数据流的无损传输.本次设计采用ALTERA公司Quartus II 9.0(32-Bit)自带的SRAM存储器进行配置,使其容量是1024位(1 KB),设计模块如图4所示.

图2 锁相环(PLL)Fig.2 Phase-locked loop

图3 采样触发控制模块Fig.3 The sampling trigger control module

图4 双口SRAM存储模块Fig.4 Dual-port SRAM memory module

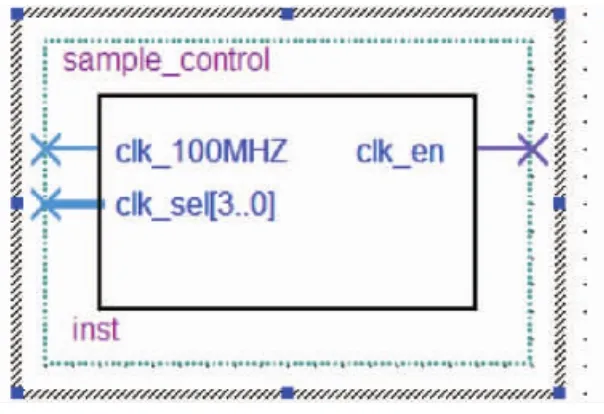

2.4 采样频率控制模块

本模块为信号采样频率控制模块,根据键盘控制模块发送过来的指令选择采样频率,并输出采样频率时钟使能信号.采样频率控制模块设计如图5所示.

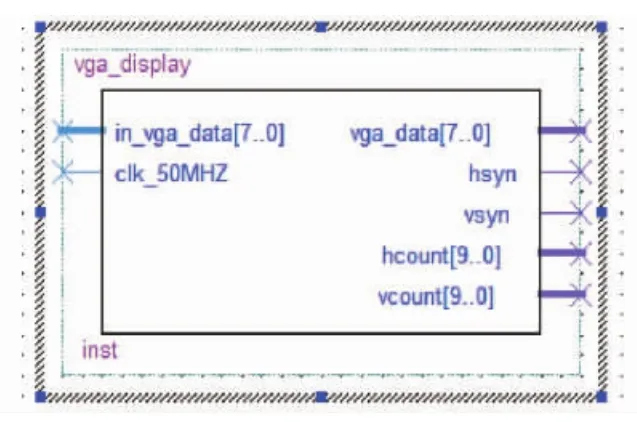

2.5 VGA显示驱动模块

该模块的作用是产生行、列同步信号,驱动VGA显示器显示由disp_controller模块送过来的波形数据,同时将行、列扫描技数器的值反馈到disp_controller模块.VGA显示驱动模块设计如图6所示.

2.6 波形显示模块

该模块的作用是读取波形存储器(双口RAM,DPRAM)的波形数据,并计算每个通道的波形在VGA显示器上对应的显示位置,同时计算并显示网络栅格线和时间基准线,最后将数据送至VGA显示驱动模块.波形显示模块设计如图7所示.

图5 采样频率控制模块Fig.5 Sampling frequency control module

图6 VGA显示驱动模块Fig.6 VGA display driver module

图7 键盘显示控制模块Fig.7 The keyboard display control module

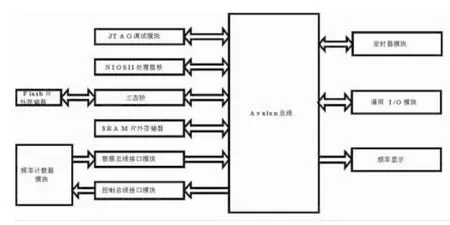

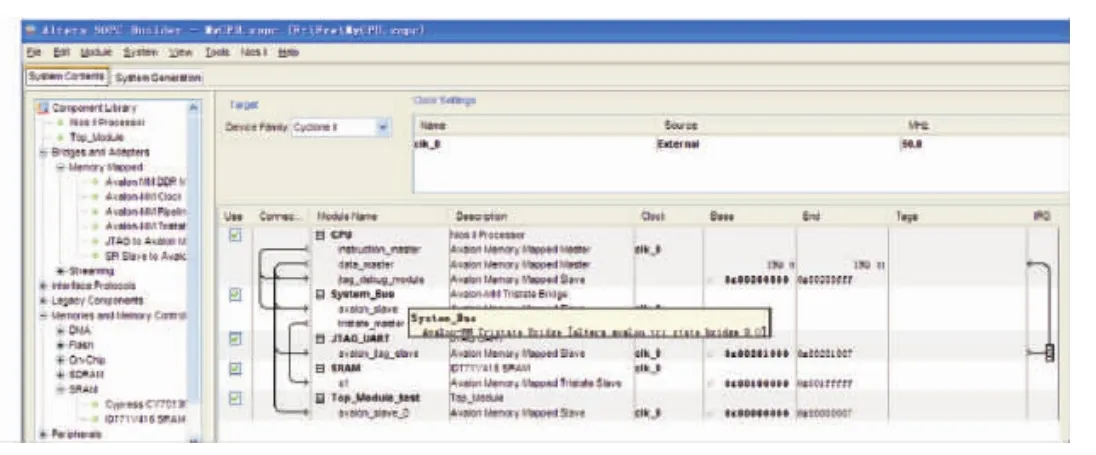

2.7 频率测量及显示模块设计

本模块根据等精度测频原理,采用SOPC技术来实现对信号频率的设计.首先,采用VerilogHDL语言设计一个IP核,然后在FPGA中嵌入Nios II软核,应用硬件和软件相结合的方式来测出待测信号的频率.频率直接在PC机上显示出来,频率测量及显示模块的总体设计如图8所示.CPU组件如图9所示.频率测量及显示模块如图10所示.

图8 频率测量及显示模块总体设计Fig.8 Overall design of frequency measurement and display module

图9 CPU组件Fig.9 CPU component

图10 频率测量及显示模块Fig.10 Frequency measurement and display module

图11 软件流程图Fig.11 Software flow diagram

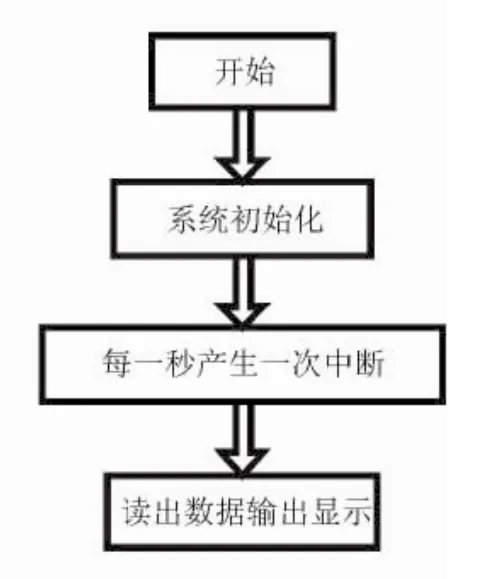

3 系统软件设计

系统的频率测量部分采用C语言进行软件设计,其软件流程图如图11所示.

4 系统测试结果与数据分析

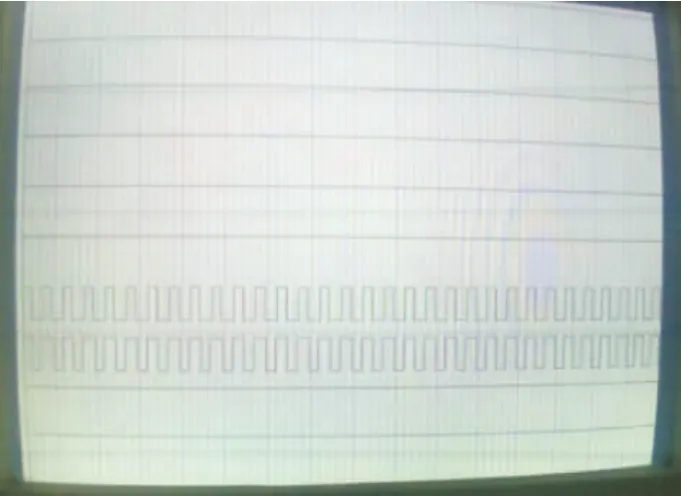

系统各模块设计完成后,对系统进行测试.在测试的整个过程中,进行了采样模式、触发模式、频率检测,对被测信号进行逻辑分析,所有的测试结果都表明电路的设计符合要求.

由于设计只能对数字信号进行检测,所以此逻辑分析仪只能用在数字电路的检测中.其测试效果如图12所示.

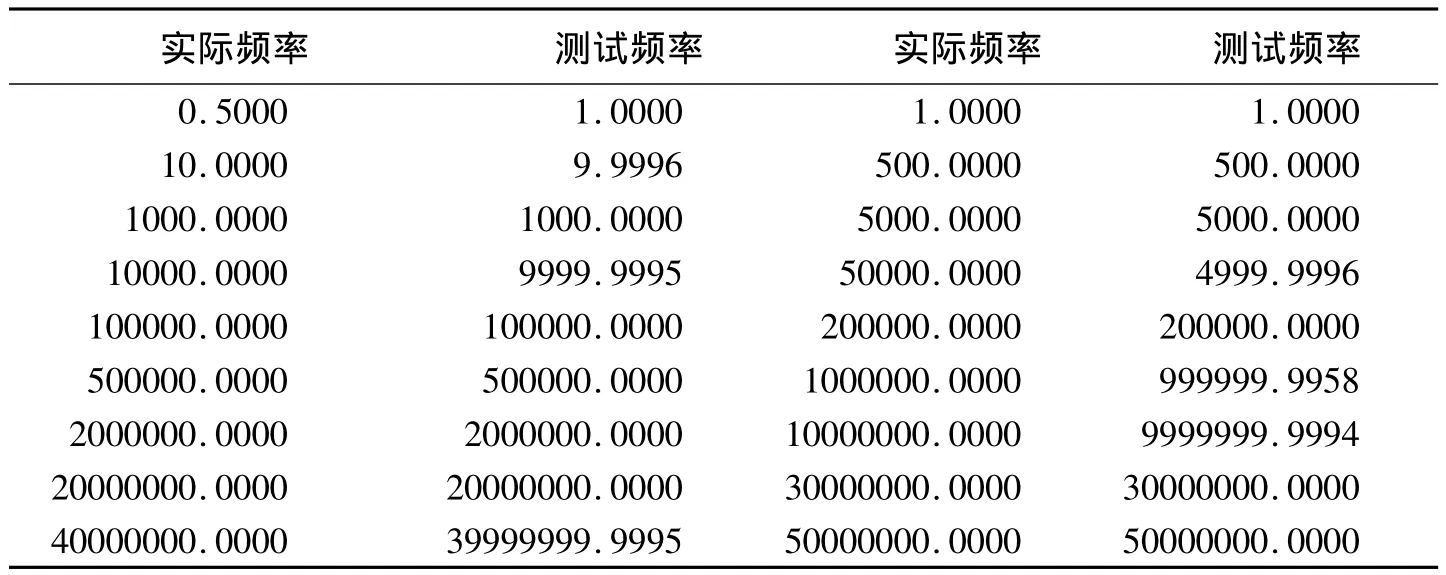

为了检测测频模块的可靠性及测量结果的准确性,测试18组数据(如表1).测试结果表明:系统测量频率时存在误差,并没有达到100%的准确率.

图12 系统测试结果Fig.12 Result of system test

表1 系统测试数据/HzTab.1 System test data/Hz

通过对数据的分析,发现等精度测频的测量精度较高,在低频段,频率测量误差较大,但当测试频率逐渐提高时,系统测频精度也随之提高.其误差在频率变大后可以忽略,故系统测频模块的设计达到了预期目标.

综合系统总的测试情况来看,系统在测频模块的指标上已经达到或是超过了同类系统的水平,虽然系统还存在不足之处,但也能对数字信号的检测和分析提供一定的帮助.

5 结束语

本系统实现了对数字信号的逻辑分析以及对数字信号频率的测量,并为系统性能进一步提高留有扩展接口,由于系统设计的集成度较高,所以系统本身对被分析信号的影响几乎为零,系统的成本较低,能够对一些数字信号进行基本的分析,而且可以当作一个频率计使用,具有很高的使用价值.

[1] 吴林平.基于虚拟仪器技术的逻辑分析仪的研究[D].南京:东南大学,2004:30-55.

[2] 周立功.EDA实验与实践[M].北京:北京航空航天大学出版社,2007.

[3] 张压平,贺占庄.基于FPGA的VGA显示模块设计[J].计算机技术与发展,2007,17(6):4-6.

[4] 左超,周金刚,崔长生.基于FPGA的简易逻辑分析仪[J].电子工程师,2008(12):5-9.

[5] 张晓健.基于NiosII的嵌入式逻辑分析仪硬件系统设计[D].西安:西安电子科技大学,2007:7-8.

[6] Wang Jiyong,Lin Tao,Li Chuanpeng.Embedded Mobile Computing Platform:Webit Agent System Model[J].Journal of Northeastern University,2002,23(5):421-424.

[7] LIU Shah-zhong,SUN Long-he.The Research Actuality of Control Theory and Its Application[J].Electronics Optics &Control,2007,14(3):87-91.