基于Hyper Lynx的高速PCB板级仿真

2012-01-19李秀娟朱剑锋黄长兵

李秀娟,朱剑锋,苏 鑫,黄长兵

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

基于Hyper Lynx的高速PCB板级仿真

李秀娟,朱剑锋,苏 鑫,黄长兵

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

随着系统时钟频率大幅攀升,保证高速电路的正常工作成为设计的首要任务。PCB板作为信号载体,高速数字信号的完整传输是其设计的重要指标。文中从电磁场理论出发,分析串扰的成因和解决方案,并利用Hyperlynx软件对某型PCB进行全局和串扰仿真验证。通过不同端接方案仿真对比,选择最佳方案将串扰减小到合理范围。

信号完整性;串扰;Hyperlynx;全局仿真

随着半导体工艺和电子技术的飞速发展,高速数字电路成为设计的主流。电路体积的减小导致PCB布局密度加大、层数增多、线迹互连和板层特性对系统性能的影响日益突出。信号完整性已成为工程师面临的重要问题。高速电路的信号完整性是指信号在电路中以正确的时序和电压做出响应的能力。常见的表现形式有反射、串扰、过冲、振铃等。

1 串扰和反射基本理论

串扰指当信号在传输线上传播时,因电磁耦合对相邻传输线产生的噪声干扰,这种干扰是由传输线之间的互感和互容引起的[1]。在高速数字电路中,信号在传输线上以电磁波的形式传输。由麦克斯韦方程可知,时变场会在周围的传输线产生电压和电流。对受到干扰的传输线而言,这个电压和电流就是由于串扰造成的。通常把噪声源所在传输线称为攻击线,受噪声污染的传输线称为受害线。

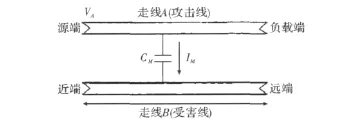

互容和互感是串扰产生的因素,根据特征分为两种。电场耦合又称容性耦合是由于攻击线上的电压变化在受害线上引起感应电流从而导致的电磁干扰。容性耦合产生串扰的示意图如下,当两条走线相靠较近时,走线A上电压VA将通过耦合电容CM产生感应电流IM,感应电流在受害线B上向近端和源端传输,产生容性串扰。感应电流大小由式(1)计算。

图1 容性耦合产生串扰的示意图

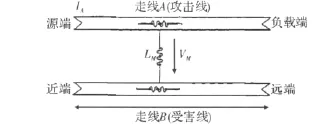

另一个耦合源是磁场耦合,又称感性耦合。感性耦合产生串扰的示意图如下,当PCB的两条走线相靠较近时,走线A上电流IA将通过耦合电感LM产生感应电压VM,感应电压在受害线B上向近端和源端传输,产生感性串扰。感应电压大小由式(2)计算

图2 感性耦合产生串扰的示意图

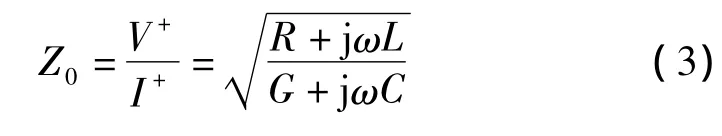

如传输线上的瞬态阻抗与线的特性阻抗相等,此时阻抗恒定,没有反射现象发生。如瞬态阻抗发生了变化或传输线上的阻抗不连续,则会使信号沿从阻抗不连续点沿传输线返回,即回波现象。特性阻抗Z0,定义为传输线上行波电压与行波电流之比

在高频范围内,R、G对阻抗影响较小,特性阻抗变化较小,视为恒定,可采用式(4)计算

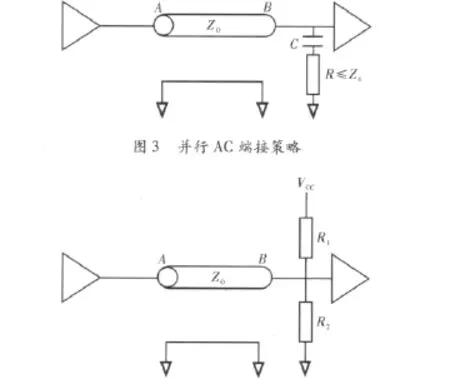

反射的消除通常采用源端串联端接和接收端并联端接两种方式,通过消除反射可达到抑制串扰的目的。其中,并联有简单并联、并行AC网络和戴维南端接等形式[2]。并行RC网络指R、C元件构成串联网络并联在接收端;戴维南端接又称为分压器端接,其端接电阻由上拉电阻R1和下拉电阻R2并联构成。

串扰与很多因素有关,受PCB板层参数、信号线间距、源端和负载端的电气特性以及端接方式影响较大。因此,减小串扰的策略较多,文中通过不同端接技术的对比来衡量串扰的抑制效果,并最终将串扰值降低到门限值以下。

2 某型PCB全局仿真

高速通信接收机电路板以FPGA为核心,FPGA处理芯片采用Altera公司CycloneⅢ 系列的EP3C25F324,完成中央控制功能和高速串行数据收发等数据处理功能。FPGA与模拟输入之间通过ADC完成转换,并通过LVDS电平实现高速数据传输,速率高达1.25 Gbit·s-1。系统中,32 MB DDR SDRAM 实现高速数据缓存,32 MB Flash作为外存储器,保存软件程序。

接收机电路板PCB的叠层设计采用12层板,其中,8层分配给信号层,2层分配给电源层,2层分配给地层。介电常数设为4.3,电路板总的厚度78.5 mil(1 mil=0.025 4 mm)。叠层分配如图5所示。

图5 振荡器比较电路

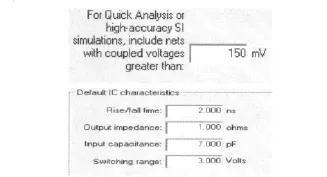

运行Hyperlynx软件 Board Wizard中的batchmode对全板进行全局扫描,找出信号完整性问题严重的网络[3]。串扰阈值设置为150 mV,约束条件设置如图6所示。

图6 串扰阈值及约束条件设置

得到如下的仿真报告:

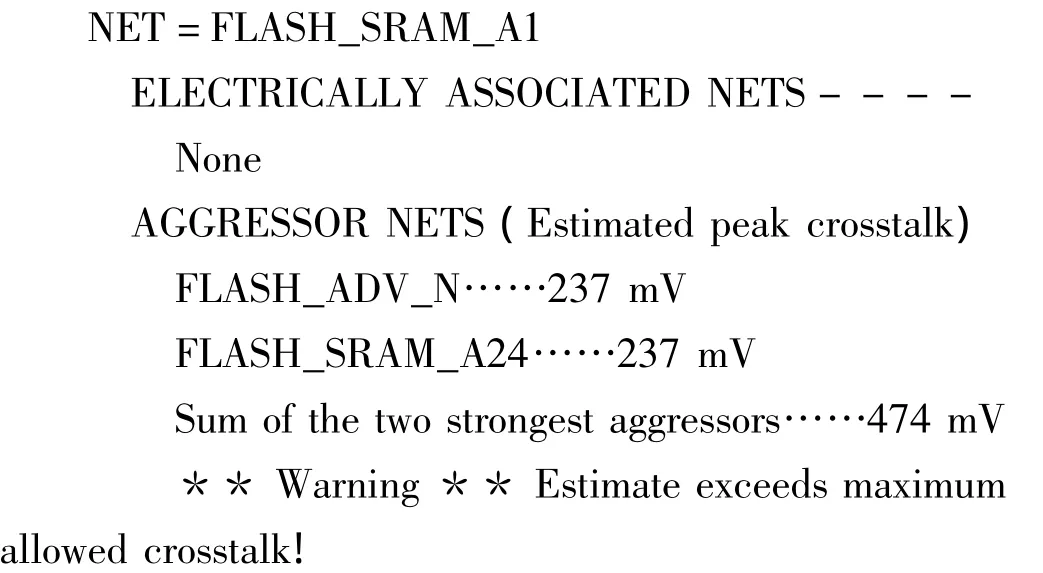

由于网络数多,仿真报告的内容较多,文中只列出其中一个,并针对串扰严重的网络进行分析和仿真。FLASH_SRAM_A1是Flash的地址线,与FPGA直接相连,是具有代表性的关键网络。由于串扰幅度高于设置门限150 mV,因此有必要对其仿真验证,并减小串扰。

3 网络仿真

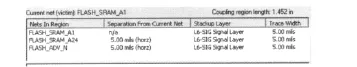

在 .hyp 文件导入后的界面选择“Net”[4],选中“FLASH_SRAM_A1”网络,如图7所示。3个网络均位于L6信号层,其中U6.A1和U1.E12为该网络的驱动端和接收端,其余为干扰网络的驱动端和接收端。网络全长3.111 in(1 in=25.4 mm),途径两个过孔。

图7 FLASH_SRAM_A1网络示意图

查看耦合区域如下,耦合长度为1.452 in。

图8 耦合区域示意图

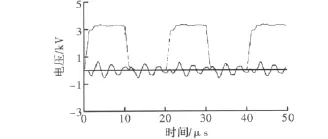

将FLASH_SRAM_A1网络的驱动端设置成“stuck low”,并为各驱动端、接收端分配模型,运行“interactive simulation”。为受害网络的接收端U1.E12和攻击网络FLASH_SRAM_A24的驱动端U6.H8添加探针,并将振荡频率设为“50 MHz”,垂直标度设为“1 V/div”水平标度设为“5 ns/div”,仿真波形如图9所示。

图9 受害网络FLASH_SRAM_A1串扰仿真波形

图中,细实线为攻击网络FLASH_SRAM_A24的驱动端波形,粗实线为受害线接收端波形,无端接时,有峰-峰值为1.22 V的串扰信号,需采取措施抑制。

4 优化路径后的仿真波形

对受害网络FLASH_SRAM_A1,在配置模型窗口中对U1.E12采取相应的端接措施[5],采用源端端接,串联60 Ω电阻时,波形如图10所示;采用并行AC端接,电容取100 pF时,波形如图11所示。并联30 Ω电阻时,波形如图12所示。戴维南端接,R1取30 Ω,R2取330 Ω时,仿真波形如图13所示。

对以上4图的仿真结果如表1所示。

表1 不同端接策略的串扰值

通过以上4图的波形和表1对比可知,采用戴维南端接仿真效果较好。继续修正端接时的电阻值,当R1取 30 Ω,R2也取 30 Ω 时,串扰值为 229.3 mV;R1、R2同取20 Ω 时,串扰值为187.5 mV;R1、R2同取15 Ω时,串扰值为162.1 mV。此时,已比较接近门限值。限于篇幅,列表如下。将R1、R2同取10 Ω时,串扰值降为89.31 mV,如图14所示,此时的串扰已远小于串扰门限值。

表2 戴维南端接不同电阻时的串扰对比

图14 R1、R2同取10 Ω时的仿真波形

综上所述,采取戴维南端接抑制串扰的效果较好;在戴维南端接策略中,调整R1、R2的取值,当R1=R2且取值较小时效果较好。

5 结束语

从串扰的成因看,减小串扰的措施较多,其中,端接技术是一种较为简单且有效的策略。降低信号频率和增大线宽同样可以减小串扰,为保证实际应用需求,文中没有采取这两种策略。串扰是常见的信号完整性问题,不采取相应措施抑制将对系统性能造成影响。因此,对串扰进行分析和处理是系统正常工作的重要保证。

[1]ERIC B.信号完整性分析[M].李玉山,李丽平,译.北京:电子工业出版社,2005.

[2]张木水,李玉山.信号完整性分析与设计[M].北京:电子工业出版社,2010.

[3]周润景,景晓松.Mentor高速电路板设计与仿真[M].北京:电子工业出版社,2008.

[4]张海风.Hyperlynx仿真与PCB设计[M].北京:机械工业出版社,2005.

[5]王昕,汪至中.高速电路设计中的终端匹配技术[J].北方交通大学学报,2002,26(4):92 -96.

[6]钟伟全,邓继忠,贺夫昌,等.一种PCB板元器件图像的分割方法[J].电子科技,2010,23(3):44 -46.

[7]郭霞,杨涛,张浩.高速数据采集系统的信号完整性分析[J].电子科技,2008,21(1):35 -37.

[8]曲利新.空间电子设备电路板可靠性测试性设计检查[J].现代电子技术,2011,35(19):151 -154.

[9]张燕燕.PCB级的电磁兼容性设计研究[J].西安邮电学院学报,2007,6(3):92-96.

Simulation of a High-speed PCB Board Based on Hyperlynx

LI Xiujuan,ZHU Jianfeng,SU Xin,HUANG Changbing

(School of Electronic Engineering and Automation,Guilin University of Electronic Science and Technology,Guilin 541004,China)

With the development of electronic technology,the first priority for designers is to ensure normal working of high speed circuits.As a signal transmission carrier,the integral transmission of high speed digital signal on PCB board becomes a important indicator of the design.This paper analyzes the reason for and solution of crosstalk by the electromagnetic theory and tests the theory via global and crosstalk simulation of a PCB board.A comparison is made of different termination techniques and the best scheme is selected to decrease crosstalk to a reasonable degree.

signal integrity;crosstalk;hyperlynx;global simulation

TN431.2

A

1007-7820(2012)08-121-04

2012-03-19

李秀娟(1982—),女,硕士研究生。研究方向:信号处理与信息系统集成。