高速电路中的信号完整性分析

2011-03-28顾菘

顾菘

(电子科技大学中山学院,广东中山528402)

高速数字系统中,由于反射、串扰、辐射和电磁干扰等问题导致逻辑信号的失真,对系统性能造成很严重的影响,对高速数字电路的信号完整性考虑是必不可少的。目前,国内外有关信号完整性工程和研究还是一门尚未成熟的学科,其分析方法和实践都没有很好地完善,还处于不断的探索阶段。但如何建立PCB板级的信号完整性模型,并能够通过模型在电路设计之初发现相关问题是本课题的关键所在。在本文设计的系统中,SDRAM等器件的工作频率已经达到了100 MHz,信号噪声和传输延时可能已经不能再被忽略,这些延时极有可能导致信号时序发生混乱,以致于整个系统的失败。

1 信号完整性的起因

信号完整性指的是在信号线上的信号质量。信号完整性问题是由于不断减小的信号上升与下降时间引起的。众所周知,PCB板上的每根导线都存在电容、电感和与频率相关的电阻。在低频电路设计中,这些都可以忽略,但当频率足够高时,这些寄生参数产生的瞬间阻抗会引起信号波形的失真、干扰等,使系统性能下降。从理论上说,当传输信号的信号线的长度大于该信号上升时间的1/6时,信号在信号线上的延迟时间大于信号的跳变时间,这条信号线就转变为具有高频效应的传输线。对于高速电路有一个比较流行的定义:当数字逻辑电路的频率达到或超过45 MHz且工作在这个频率之上的电路占整个电路的1/3以上时就称为高速电路。但在当今的高速电路设计中,即使是一些工作在20MHz频率的产品,仍然有可能会碰到一些相类似的问题[1]。由于此时的导线已经成为一种被耦合到其周围所有事物的元素,所传输的信号并不被完全地包含在其自身的导线中,而是被其周围所有局部电磁场作用,围绕在导线表面。一根没有合理匹配的传输线会导致信号波形的失真,严重的会造成定时错误,系统误工作,甚至引起系统崩溃。

2 信号完整性的分类

信号完整性问题主要包括反射(reflection)和串扰(crosstalk)等。反射是由于信号源端和负载端阻抗不匹配而引起的;而串扰就是信号线之间的耦合问题,信号线之间的互感互容导致了传输线上的噪声。本文着重分析反射对信号完整性的影响。

3 反射的理论分析

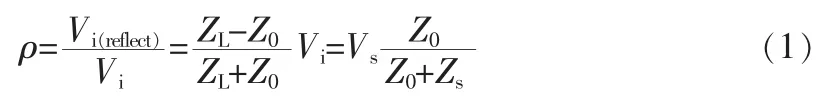

信号Vi从源端经传输线传输至负载端。源端输出阻抗为Zs,传输线特征阻抗为Z0,负载端阻抗为ZL。如图1所示。由于源端和负载端阻抗不匹配,信号的一部分由负载端反射至源端。其中反射系数决定了被反射回去的信号大小。

反射系数:

由上可以看出,当传输线终端连接一个正好等于其特征阻抗的值时(即ZL=Z0时),反射系数为0,信号无反射的终接到地;当负载开路或短路时(即ZL=0或ZL为无穷大时),反射系数为1或-1,信号将无损地从负载端反射到源端。同理,当信号被反射至源端后,若源端阻抗与传输线特征阻抗也不匹配,信号就会产生二次反射。以此类推,信号将在源端和负载端来回反射,直到最后形成直流稳态。

网格图是用于解决带线性负载传输线上多次反射的方法。如果在系统中存在非线性负载或源时,Bergeron图将能够更准确的表达反射的过程。以下通过一个基于DSP的指纹识别系统的电路设计实例,讲述Bergeron图的应用和反射对信号完整性的影响。

4 反射的实例应用

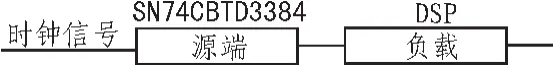

本例所采用的DSP芯片为TI公司的TMS320C6711,时钟频率为150 MHz。其中时钟信号的质量对整个系统起了决定性的作用。晶振由倍频器产生150 MHz时钟信号后,利用TI公司的SN74CBTD3384芯片进行电平转换,输入至DSP中,如图2所示。

图2 电路模型Fig.2 Circuit model

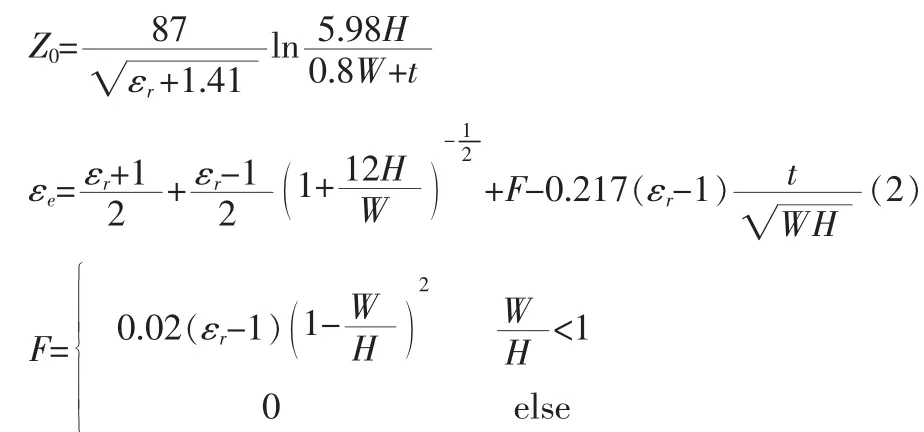

以下是计算所需的公式:

TD=为光速

假设PCB板的介电系数εr=4.8,PCB板布线线宽为W=5mil,厚度为t=1 mil,板层第一层高H=12.6 mil,时钟信号由微带线传输,传输线长度x=4 000 mil。由公式(2)中可计算得传输线特征阻抗为95 Ω。从芯片资料中可以查出SN74CBTD3384输出阻抗ZS=35 Ω,DSP的CLKIN输入阻抗远大于传输线特征阻抗。由公式(1)可得源端反射系数为-0.46,负载端反射系数为1。再由公式(2)中计算得传输线延迟时间TD=602 ps。由于系统存在非线性负载,此处用Bergeron图计算每次反射的大小。由TI公司提供的IBIS模型(I/O BufferInformation Specification)中可知DSP的CLKIN引脚的输入I/V曲线[2],画出Bergeron图和非线性负载反射图,如图3所示。当传输线阻抗大于源端阻抗时的传输线称为过载传输线;而当传输线阻抗小于源端阻抗时的传输线称为欠载传输线。从图中可以看出,过载传输线的多次反射会产生振铃效应。

图3 Bergeron图和非线性负载反射图Fig.3 Bergeron diagram and non-liner load reflection map

5 消除反射的方法

反射对高速数字系统的性能有重要的负面影响。为了尽量消除反射对系统的负面影响,通常采用3种方法。

1)降低系统的频率,使信号在传输线上的反射在下一个信号到达之前达到稳态。这种方法一般采用在对系统速度要求不高的电路设计中。

2)缩短PCB板的走线长度,使反射达到稳态的时间更短。这点固然是每个设计人员在布线时所必须考虑的因素,但这样会增加PCB板的层数,从而增加设计成本。另外,在某些特定情况下,缩短走线长度几乎是不可能的。

3)在传输线上端接无源元件,实现传输线与负载或源端间的阻抗匹配,使源端或负载端的反射系数为0或走近于0,从而在源端或负载端消除反射。这种方法无论在理论上或是实践中,都是消除反射的首选方案。

6 PCB板设计过程中的仿真分析

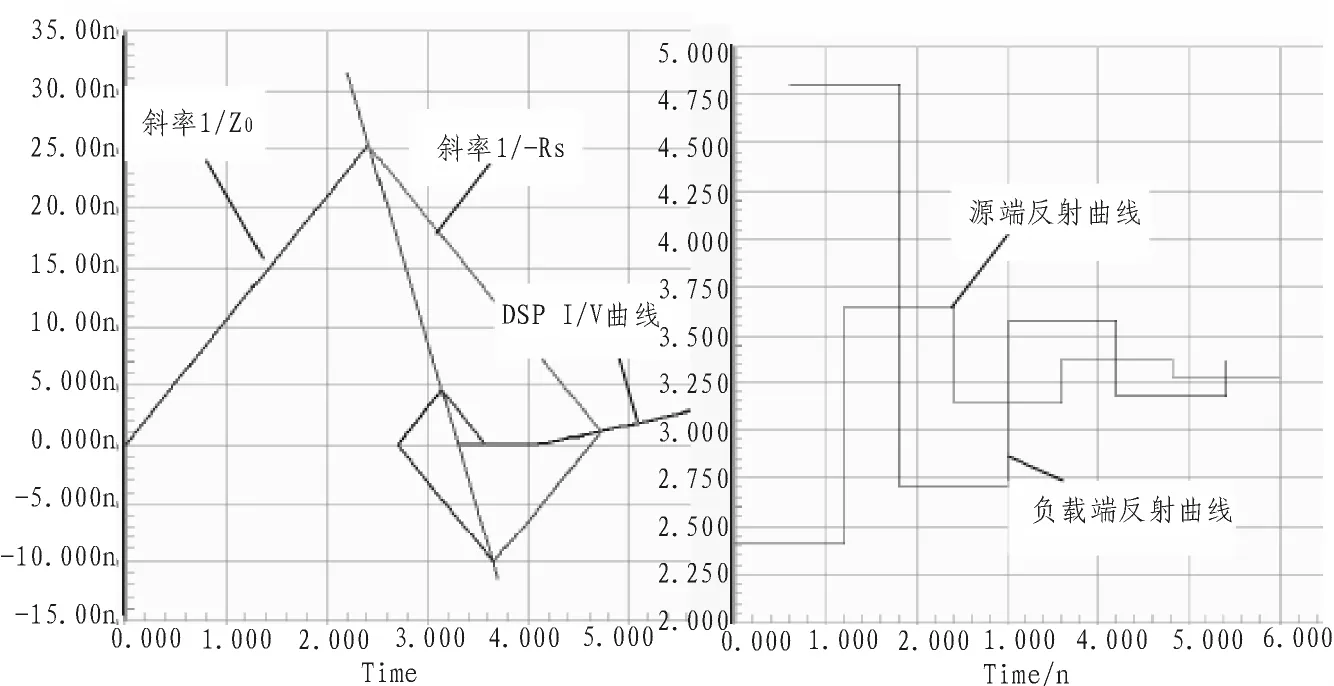

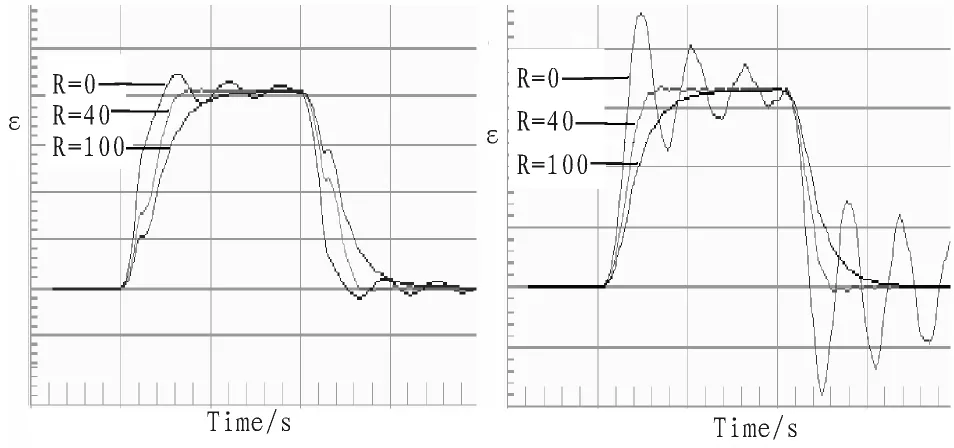

在本文的电路设计中,采用了上述的第三种方案。并针对源端和终端两种端接形式作了仿真与比较[3],图4所示为源端匹配和终端匹配在不同电阻值时信号经多次反射在负载端的仿真波形。源端匹配即在源端串接电阻,使源端阻抗和电阻的总和大致等于传输线的特征阻抗,消除源端反射。而终端匹配即在负载端与地(或电源)之间并接电阻,使负载端阻抗大致等于传输线特征阻抗,消除负载端反射。

图4 仿真波形Fig.4 Waveform of simulation

从图中可以看出:

1)用源端匹配时,当匹配电阻R=0时,源端和负载端的很强的过冲和振荡现象,这和以上用Bergeron图计算的结果大致相似。随着匹配电阻的增大,振荡逐渐减小。但当匹配电阻过大时,信号上升时间拉长。其中,匹配电阻为40 Ω时,信号质量最好。

2)用终端匹配时,随着匹配电阻的减小,振荡逐渐减小,但由于稳态电压由源端电阻和负载电阻之间的分压确定,因此稳态电压也逐渐减小,而DSP的高电平输入最小电压为2 V,所以匹配电阻为40 Ω时,信号质量最好[6]。

7 串扰的影响

另外,在高速电路中串扰现象也很严重。PCB板层的参数、信号线间距、源端和负载端的电气特性等都对串扰有一定的影响。增大两条传输线之间的距离,使传输线紧密地与地面进行耦合等等都能够减少串扰的影响[1,5]。

8 信号完整性在实际应用中的经验

终端匹配可以消除缓冲器阻抗相关的未知变量,它的缺点在于电路中大部分的直流电流被分流到地,这加大了功率输出和发热问题。而源端匹配可以很好地消除反射造成的振铃和过冲效应,它的缺点在于电阻增加了板的成本并占用有效的PCB板面积。因此,在高速电路设计中,通常采用源端匹配技术。通常情况下,100~200 MHz的信号频率其匹配电阻为30~50 Ω。当然,还有其他匹配技术,如在负载端使用串联电容和电阻的方式消除反射等等,这些方法都各有其优缺点。合理的布线对解决信号完整性问题也显得尤为重要。

本系统中,在频率大于100 MHz的信号线上均采用了源端匹配技术有效消除了反射造成的噪声影响;在每个器件的电源和接地引脚间均加入了去耦电容。在不违背一般原则的前提下,利用现有的布线经验和一些信号完整性的仿真结果来约束和指导布线。

9 结论

本文结合系统设计中的实例,对高速信号传输的信号完整性问题作了较为详细的论述。通过建立信号完整性模型,并利用模型仿真结果进行信号完整性设计[4],从而大大减小了开发周期和开发成本,对嵌入式电路设计人员的电路设计有较强的参考价值。

[1] 周路,贾宝富.信号上升或下降时间对高速电路信号完整性影响的研究[J].现代电子技术,2011,34(6):69-77.ZHOU Lu,JIA Bao-fu.Effects of signal rise or fall time on high-speed circuit’s signal integrity[J].Modern Electronics Technique,2011,34(6):69-77.

[2] 张东,李琼,秦前清.基于IBIS模型的仿真分析在SDRAM印刷电路板设计中的应用[J].武汉大学学报:理学版,2011,57(1):83-87.ZHANG Dong,LI Qiong,QIN Qian-qing.Application of simulation analysis based on IBIS model to SDRAMPCB design[J].Journal of Wuhan University:Natural Science Edition,2011,57(1):83-87.

[3] 李莉,路而红,周玉坤.基于Protel DXP的信号完整性分析[J].北京电子科技学院学报,2007,15(2):52-54.LI Li,LU Er-hong,ZHOU Yu-kun.Signal integrity analysis based on protel DXP[J].Journal of Beijing Electronic Science and Technology Institute,2007,15(2):52-54.

[4] 阮琼,廖红华.高速电路板的信号完整性设计与仿真[J].湖北民族学院学报:自然科学版,2010,28(4):446-449.RUAN Qiong,LIAO Hong-hua.Signal integrity design and simulation of high-speed PCB[J].Journal of Hubei University for Nationalities:Natural Science Edition,2010,28(4):446-449.

[5] 吴昊,陈少昌,王杰玉.高速数字系统的串扰问题分析[J].现代电子技术,2009,32(1):170-173.WU Hao,CHEN Shao-chang,WANG Jie-yu.Crosstalk analysis for high-speed digital system[J].Modern Electronic Technology,2009,32(1):170-173.

[6] 张磊,雷震,刘海波.高速电路设计和信号完整性分析[J].电子技术应用,2001(6):70-73.ZHANG Lei,LEI Zhen,LIU Hai-bo.High-speed circuit design and signal integrity analysis[J].Electronic Technology,2001(6):70-73.