基于FPGA的多仪表合一的设计与实现

2012-04-24罗苏笙苏海涛

赵 云,郭 庆,罗苏笙,苏海涛

(桂林电子科技大学电子工程及自动化学院,广西桂林 451004)

Altera公司提出的片上可编程系统(System-ona-Programmable-Chip,SOPC)解决方案可将 CPU、储存器、I/O接口、锁相环(PLL)等系统设计所必须的模块集成到一片FPGA上,构成一个可编程的片上系统,Nios嵌入式处理器正是借助于这种片上可编程系统实现的,因此用户可以轻松地根据仪器设计的需求,创建合适的硬件。SOPC解决方案使得FPGA在开发嵌入式仪器的设计领域地位越来越重要。设计基于FPGA实现高速FIFO存储体和DDS IP核,设计了高性能的模拟控制电路。将数字示波器和函数信号发生器两种常用仪器,进行了仪表合一的设计。

1 基本原理

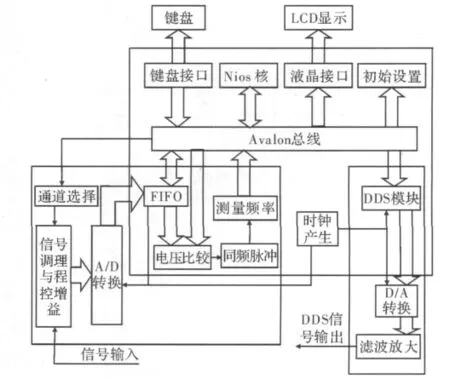

系统主要由数字示波器和函数信号发生器组成,系统整体实现框图如图1所示。其中数字示波器主要包括信号调理与程控增益模块、A/D数据采集模块、FPGA和人机接口模块。函数信号发生器主要包括FPGA、D/A转换模块和人机接口模块。信号调理电路与程控增益模块主要完成阻抗变换,程控增益放大;FPGA主要实现频率测量模块、FIFO模块、键盘扫描模块、高速数字时钟系统以及DDS IP核;人机接口模块采用矩阵键盘和TFT液晶屏,D/A转换模块采用D/A及滤波放大模块。

图1 系统整体实现框图

2 硬件电路设计

2.1 模拟信号调理电路

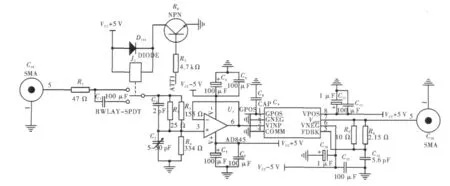

模拟信号调理电路包括信号输入阻抗变换、程控增益。阻抗变换及程控增益电路如图3所示,模拟信号输入可选择交流或直流耦合,采用精密放大器AD845构成电压跟随器实现阻抗变换,提高输入阻抗。

图2 阻抗变换及程控增益电路

程控增益放大器采用 AD603实现,AD603在-10~30 dB时典型带宽为90 MHz。控制电压为-0.5~0.5 V的差分输入电压,采用由使用外部基准电压输出的10位数模转换器TLC5615提供,并由运算放大器OP07将输出的0~VREF电压转换为-0.5~0.5 V的控制电压,外部基准电压由MC1403产生。控制电压产生电路如图3所示。

图3 控制电压产生电路

根据垂直灵敏度20 mV/div~1 V/div,ADC最大输入为1 V,可计算出增益范围为-12~22 dB。AD603可控增益范围-10~30 dB,由于AD845输入采用1/3分压方式,AD603实际增益范围为-19.6~20.4 dB。

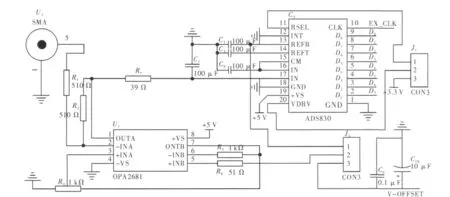

ADC连接电路如图4所示,ADS830采样率为60 MSa/s,前级采用宽帯仪表运放OPA2681构成前级调理电路,并使用精密多圈电位器作直流偏移电平调整。通过调理电路的调理,使信号输入端的模拟输入电压范围扩展至-1.00~1.00 V,并保证模拟输入为0 V时输出的数字量为01111111。

2.2 FPGA模块

FPGA模块使用Altera公司的开发板DE2进行开发与扩展。设计原则是最大程度地使用片上软硬件资源,减少外围附加电路。

2.2.1 FIFO模块

利用Quartus中的LMP定制了两个8 kB的FIFO保存双路A/D采集数据。另外FIFO模块中同时设计了扫描触发模块。其工作原理为启动A/D采样后,采集数据与触发字进行比较,根据触发源选择信号,一旦满足设定条件产生触发信号,送至FIFO控制器端。由于A/D采样时钟与写入时钟同步,采集数据根据写时钟写入到FIFO中。当FIFO未达到预触发深度时,FIFO只写入数据,不读出数据,并且此过程中触发信号是被抑制的。

图4 高速模数转换器ADS830的连接电路

2.2.2 频率测量模块

采用周期同步测频法对触发信号进行测频,根据测得频率选择对应的采样率。在被测信号边沿到来时同时对被测信号和基准信号进行计数,计数闸门时间1 s,当基准信号计数完成时停止对被测信号计数,将对被测信号的计数结果除以计数的时间即可得到实际频率。设计被测信号采用32位计数器,测频范围约为0 ~60 MHz,最小分辨率为5 Hz。

2.2.3 高速数字时钟系统

高速数字时钟系统采用Quartus中的LMP定制的锁相环将晶振信号倍频,送至时基产生模块产生同步的A/D采集时钟与FIFO控制器时钟。

2.2.4 DDS IP核的实现

数字直接合成频率技术(DDS)的基本原理是利用采样定理,通过查表法产生波形。DDS IP核实现了波形选择、频率和幅度调节功能。

3 软件设计

系统软件开发任务是在Nios IDE下完成。主流程图如图5所示,软件主要包括以下工作:

系统初始化。对液晶屏复位并绘出显示框架、初始化函数信号发生器的输出、对FPGA进行复位等。

按键处理。当FPGA响应键盘产生的中断后读取按键值,判断并对按键产生响应,在运行示波器功能时,通过按键实现采样参数的改变、显示参数的改变等;在运行函数信号发生器功能时,通过按键设置函数信号发生器参数的改变。

采样参数设置。包括通过控制继电器改变输入信号耦合方式、控制产生数模转换器输出的增益电压等。

显示参数设置。显示参数包括波形的水平、垂直移动、测量得到的频率、幅度和周期等。

函数信号发生器参数的设置。包括幅度、频率设置以及波形的切换。

图5 系统软件主流程图

4 实验和验证

测试用的仪器为TDS2012示波器及TFG6050 DDS函数信号发生器。将TFG6050输出的信号连至TDS2012与待测数字示波器上,逐个观察三者频率与幅度。如此改变TFG6050输出信号的频率与幅度进行数字示波器功能及指标测试。测得FPGA数字示波器的性能指标如下,垂直分辨率为8 bit,垂直灵敏度范围为20 mV/div~1 V/div,最大实时采样率为60 Msample/s,可测频率范围为200 Hz~6 MHz,扫描速度范围为100 ns/div~0.1 s/div,输入阻抗为1 MΩ,波形显示结果良好。

将待测函数信号发生器的输出接至TDS2012,观测波形及其频度、幅度。可以测得函数信号发生器性能,频率范围为1 Hz~10 MHz,幅度范围0.1 ~9 Vpp,可以产生正弦波、方波、锯齿波和三角波。

5 结束语

经过测试结果表明,设计中示波器和函数信号发生器均可较好完成测试工作,充分发挥了FPGA并行执行的特点,实现数字示波器和函数信号发生器的功能,充分显示了FPGA在仪表控制方面的优势。

[1] HOWARD J.高速数字设计[M].北京:电子工业出版社,2003.

[2] 陈尚松,郭庆,雷加.电子测量与仪器[M].2版.北京:电子工业出版社,2009.

[3] 李世文,潘中良,何道清.数字存储示波器中触发电路的FPGA设计与实现[J].中国仪器仪表,2009(3):68-71.

[4] 江国强.EDA技术与应用[M].北京:电子工业出版社,2010.

[5] 叶苑,周建明,张沁川.高速数字存储示波器实现技术[J].电子测量与仪器学报,2005,19(3):42-45.