两种算法相结合的基带数据流加密编解码方法

2011-08-27刘诚毅桂延宁胡建军

刘诚毅,桂延宁,杨 燕,胡建军

(1.机电动态控制重点实验室,陕西 西安 710065;2.西安机电信息研究所,陕西 西安 710065)

0 引言

加密是数字通信领域中非常重要的技术组成部分。在数字通信系统中通常采用加密的方法对传输信息进行保护。关于加密方法,通常采用对称加密或者非对称加密两种方案。对称加密方法是将原始数据分组和加密密钥一起经过特殊加密算法处理后,使其变成复杂的加密密文发送出去,收信方收到密文后采用相同密钥和加密算法的逆算法进行解密,才能恢复成可读的原始数据。分组加密方法具有算法公开、计算量小、加密速度快等特点。

AES是一种典型的分组加密方法,于2001年公 布 在 FIPS(Federal Inf or mation Processing Standar ds)上,自被接纳为标准之日起就已经被工商业界、银行业、政府等作为事实上的密码标准[1]。

AES的高安全性使其成为21世纪加密方法的主流。但是由于其分组的确定性,不能对通信系统中一定的帧结构进行完整的数据加密。针对这一点,本文提出在FPGA平台上基于AES和RC4双分组加密方法相结合的方式对一定帧结构的基带信号进行数据加密。

1 加密算法

1.1 AES加密算法

高级加密标准(Advanced Encryption Stand-ar d,AES)是一种分组迭代加密算法,明文分组长度固定为128 bit,而且支持128、196或256 bit的密钥长度。AES加密算法的实现流程如图1所示。

图1 AES加密算法实现流程Fig.1 Schematic of AES

AES密钥有128、196或256 bit,因此对穷举法攻击有很高的安全性,大多数针对加密算法的攻击已经都在AES上测试过,迄今没有一种攻击可以破坏 AES的安全性[2]。

这种传统的AES加密,信息位个数必须是分组长度的整数倍。不然多余的信息位将不能实行AES加密。这将导致一定帧结构中有部分信息位不能包含消息,进而导致信息传递速率的降低。

1.2 RC4加密算法

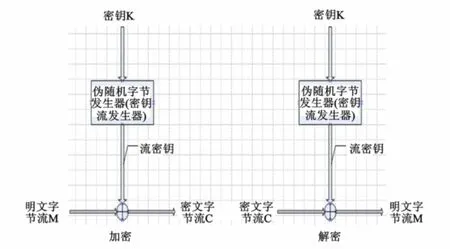

RC4是Ron Rivest在1987为RSA公司年设计的一种流密码。它是一个可变密钥长度且面向字节操作的流密码。RC4算法非常简单,易于描述:用从1~256 B(8~2 045 bit)的可变长度密钥初始化一个256 B的状态向量S,S的元素记为S[0],S[1],…,S[255],从始至终置换后的S包含从0~255所有8 bit数。对于加密和解密,由S中255个元素按照一定方式选出一个元素而生成伪随机字节与明文(密文)进行模2加从而得到密文(明文)。流密码结构见图2。

图2 流密码结构示意图Fig.2 Schematic diagram of stream ciphers

RC4也具有较高的安全性,如果最小的密钥是128 bit,则该种加密方法是安全的[3]。

1.3 传统基带数据流的AES加密算法

1.3.1 基带数据流帧结构

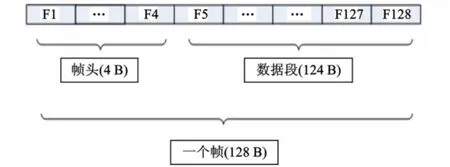

加密解密算法作用于基带数据流,而基带数据流的基本单元是帧。本文采用的是128 B帧长的数据流进行加密。帧结构如图3所示。

图3 帧结构Fig.3 Structure of frame

帧头4 B是帧同步等信息位,后面的124 B是数据段,加密算法应在数据段中进行操作。

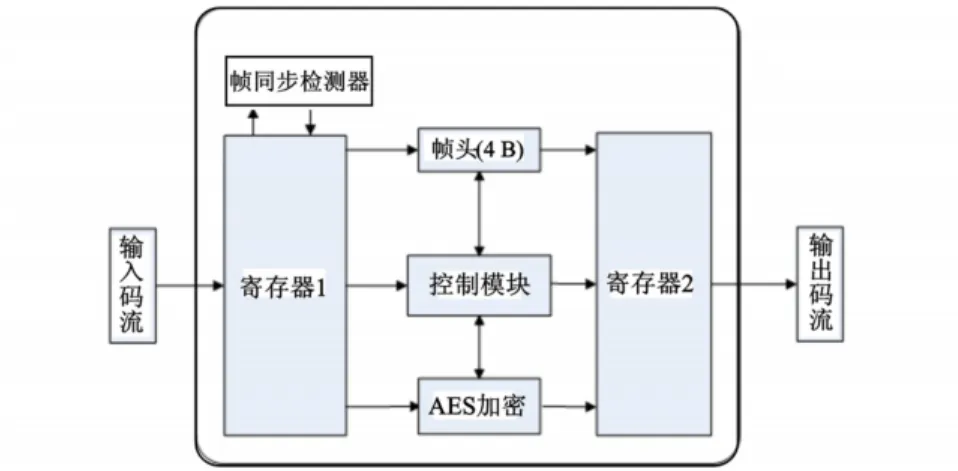

1.3.2 AES对定帧长基带数据流进行加密

单一AES算法加密系统框图如图4所示。

图4 传统AES数据加密Fig.4 Traditional AES encryption

数据输入端口向系统输入码流,系统将其存在寄存器1中,并时刻与帧同步检测器进行通信,若帧同步检测器检测到帧同步信号则输出一个使能信号让寄存器1开始向中间寄存器送数据,由于系统要求帧结构保持不变,帧头信息位不能改变和AES的加密特点,可以看出其中有12 B的信息位没有加密而被输出。所以此加密实现方法在安全性和有效性方面都存在问题。

2 AES和RC4算法相结合的基带数据流加密解密

从上述两种加密算法的介绍可以看出,RC4具有灵活多变性,但是加密强度需要密钥长度的支持。AES加密算法安全性很高,但是分组固定,不宜灵活运用。在FPGA中为了实现高效的基带数据流加密,根据RC4和AES加密的特点,在此引入AES和RC4加密算法相结合的加密方法对基带数据流进行加密。

2.1 AES加密模块

与传统AES加密算法一样,128 bit的帧结构中第5~116 B共有112 B用AES加密,即用了7次AES加密。

2.2 RC4加密模块

基于RC4加密的灵活可变性,将其设计成用于12 B的加密模块,这样传统加密系统中剩余的12位信息位就可以安全地进行数据加密并传输,进而弥补了传统AES加密方法的缺点。此加密模块使用128 bit密钥,具有较高安全性。

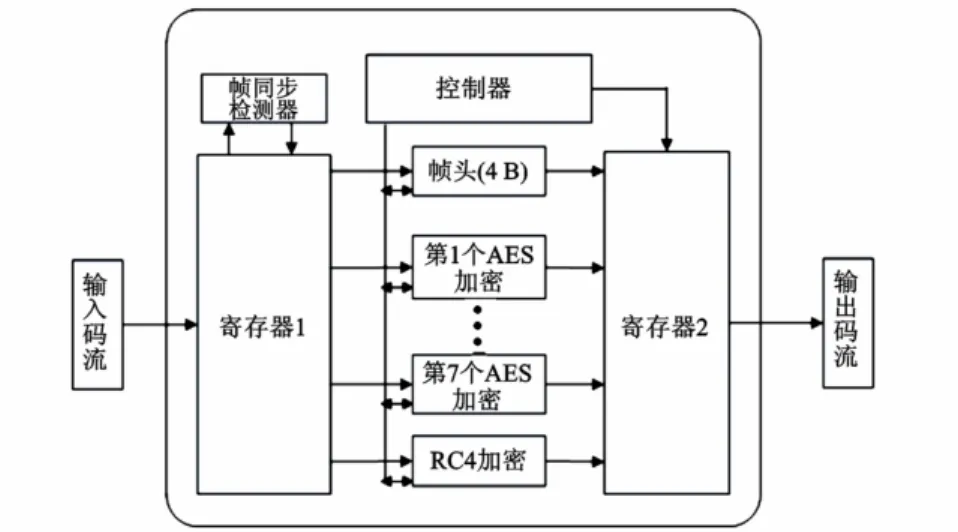

2.3 综合改进后加密方案

本文综合上述方法,将128 bit帧长划分成3部分进行操作,其系统框图如图5所示。

图5 AES与RC4综合加密算法系统框图Fig.5 AES and RC4 encryption algorith m integrated system block diagra m

帧头部分传输的是帧同步等信息,因此在系统中应不做改变,存储于寄存器2中等待发送;7段AES数据加密将帧结构中的5~116 B进行AES加密;帧结构中117~128 B则用RC4进行加密。当系统开始工作,首先检测输入码流的当前4 B,如果是帧同步信号,则帧同步检测器向寄存器1发出加密指令,此时寄存器开始向加密模块进行数据传送,将4 B帧同步信息送入图中帧头寄存器中,送完帧头寄存器反馈给控制器一信号,表明帧头部分传送完毕,由控制器发出开始AES加密的指令。当进行了7次AES加密后,由AES加密模块向控制器输出AES加密完成信号,再由控制器输出RC4加密使能信号,当RC4加密完成后送出使能信号,则寄存器2开始输出加密后的码流。本设计能够在捕捉到帧同步信息后很快、连续地对N帧长的数据进行加密。

2.4 综合改进后解密方案

由于AES与RC4的加密和解密互为逆过程,因此解密系统框图也为图5所示,仅是相应模块作调整。

3 仿真验证

在Quart us环境下使用Modelsi m软件对整个工程进行功能仿真。

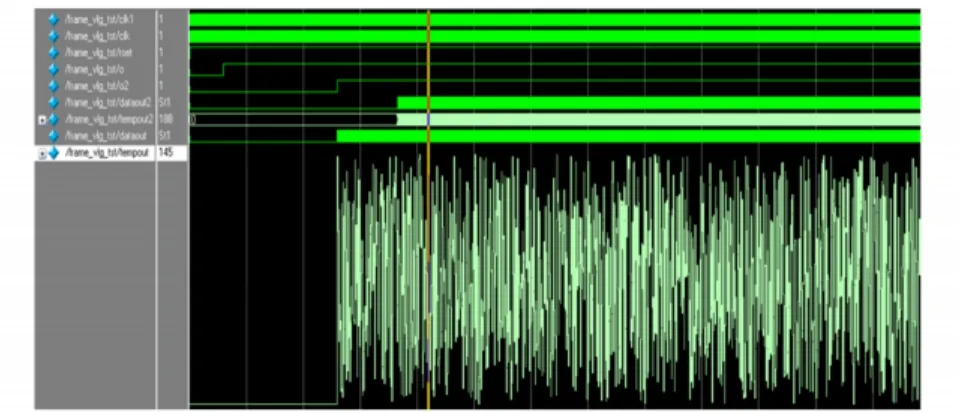

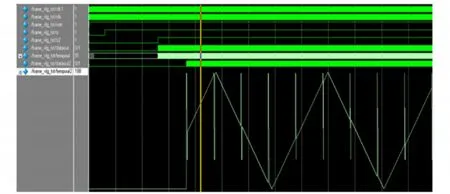

仿真采用的输入是三角波的离散值形成的具有帧结构的二进制码流,其离散值从0到255再到0为一个周期,每一个离散值用8 bit二进制表示,帧同步信息为4 B FDB18540。为了便于直观看出加密和解密的效果,本文把加密和解密的输出码流还原成8 bit离散值进行观察。加密后结果如图6所示,解密后结果如图7所示。

图6 综合后加密仿真波形Fig.6 After the encr yption integrated simulation wavefor m

图7 综合后解密仿真波形Fig.7 After the decryption integrated si mulation wavefor m

从图6中可以看出,加密后输出码流为dataout,还原8 bit的离散值后的tempout信号不再具有三角波的特点,保留帧同步信息FDB18540用于传输,后面信息位124 B在AES和RC4加密算法的共同作用下实现了全帧的基带数据流加密,解决了传统AES加密后12 B不能操作的缺点。

从图7中可以看出,接收端将基带数据流送入解密模块后,输出的码流信号dataout2被还原成8 bit离散值的tempout2信号,tempout2信号保持了三角波的波形,解密效果清晰可见。图中三角波上离散突起的值为帧同步信息FDB18540。

4 结论

本文提出了一种基于FPGA的基带数据流加密编解码方法,通过综合使用AES和RC4两种加密方式,对基带数据流进行加密。仿真结果表明:基于FPGA的基带数据流加密解密系统能够稳定、高效地完成数据流加密和解密。

[1]刘珍桢.AES加密算法的一种优化的FPGA实现方法[J].现代电子技术,2007(23):103-106.LIU Zhenzhen.Implementation of AES encryption based on FPGA[J].Modern Electronics Technique,2007(23):103-106.

[2]Stallings W.密码编码学与网络安全[M].第四版.孟庆树,王丽娜,傅建明,等,译.北京:电子工业出版社,2006.

[3]Behrouz A.Forouzan.密码学与网络安全[M].马振晗,贾军保,译.北京:清华大学出版社,2008.