采用DSP和FPGA多电机速度伺服驱动控制平台

2011-06-06于凯平郭宏吴海洋

于凯平, 郭宏, 吴海洋

(北京航空航天大学自动化科学与电气工程学院,北京 100191)

0 引言

速度伺服是伺服控制系统的重要组成部分之一,在电动汽车、电动轮椅和机器人等领域有广泛应用[1-3]。在这些领域中,往往需要同时使用多台电机,并且具有速度同步控制的需求。传统的方式,都是采用基于单个微控制器或单个定点数字信号处理器(digital signal processor,DSP)的控制器控制单台电机,这些控制器之间通过总线通讯实现速度的同步控制,其存在两点不足[4-5]:孩系统结构复杂,成本高;虎控制器难以实现多电机系统的复杂速度伺服控制算法。近年来,现场可编程门阵列(field programmable gate array,FPGA)已逐渐应用于电机控制中。FPGA可以替代复杂的逻辑电路,在简化系统结构,实现控制器小型化等方面发挥重要作用[6]。因此,基于DSP+FPGA的控制平台技术是目前电机驱动伺服领域的研究热点之一[7-11]。并且,在控制平台中采用浮点DSP便于实现复杂的控制算法,完成高精度的速度伺服控制。

设计了一种以浮点DSP和低成本FPGA为核心的控制平台,划分了DSP和FPGA各自承担功能,并介绍了具体的实现。以2台无刷直流电动机(brushless DC motor,BLDCM)为控制对象,对基于DSP+FPGA的多电机驱动控制平台的功能进行了验证。

1 控制平台的结构和功能

多电机速度伺服系统的结构包括一个控制平台,两个驱动器和两台BLDCM,如图1所示。

图1 多电机速度伺服系统的结构Fig.1 The structure of multi motors speed-servo system

设计的控制平台以浮点DSP-TMS320VC33和低成本FPGA-EP2C8为核心,需要完成的功能包括:

1)接收速度指令;

2)完成速度环计算;

3)完成电流环计算;

4)产生PWM控制信号;

5)获取速度检测值;

6)获取电流检测值。

浮点DSP适合实现控制算法,FPGA善于完成时序电路和逻辑电路。因此,确定DSP作为主控制器,需要完成的功能包括1)、2)和3),FPGA作为从控制器,需要完成的功能是4)、5)和6)。二者之间交换的数据包括:DSP从FPGA读取电机的速度检测值、电流检测值,DSP下发电流环计算结果给FPGA。

2 DSP功能设计

主控制器DSP承担的功能主要是控制算法的计算,2台电机的速度环和电流环均采用的增量式数字PI控制算法,控制算式为

式中:u(k)为当前输出;u(k-1)为前次输出;e(k)为当前偏差;e(k-1)为前次偏差;KP为比例系数;KI为积分系数。

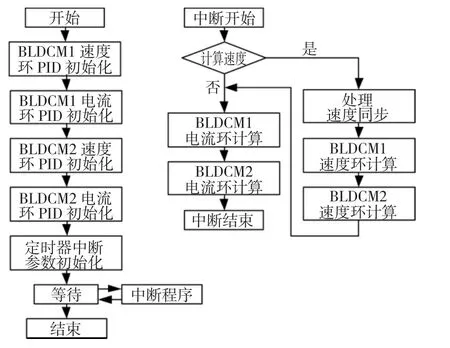

DSP的程序分为两个部分:主程序和中断处理程序,流程如图2所示。电流环计算频率为10kHz,速度环计算频率为1kHz。

图2 DSP的主程序和中断程序流程Fig.2 The programming flowchart of DSP

两台BLDCM的速度指令可以独立输入,也可以给出协同关系,由中断处理程序中的速度同步模块进行处理,非常简便。

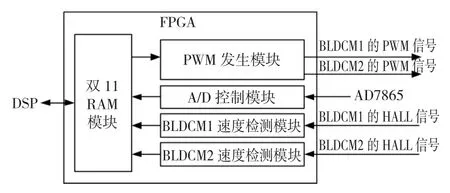

3 FPGA功能设计

在从控制器FPGA的设计中,采用自顶至下的设计方法。将FPGA需要完成的功能划分为若干个功能独立的功能模块,各个模块可以单独进行测试、验证,然后在顶层实体中直接调用。该方法可以缩短开发时间,便于查找问题、修改和功能升级。根据FPGA所承担的功能、结合FPGA的特点,划分了双口RAM模块、PWM发生模块、A/D控制模块、BLDCM1速度检测模块和BLDCM2速度检测模块等5个功能模块,如图3所示。设计流程如下:

1)采用VHDL完成设计输入;

2)综合和逻辑优化;

3)布局、布线;

4)功能仿真和时序仿真;

5)布局优化;

6)配置到EP2C8,硬件调试。

图3 FPGA功能模块图Fig.3 The functional modules of FPGA

3.1 双口RAM模块设计

DSP与FPGA之间的所有数据都通过双口RAM模块交换,该模块在FPGA内部实现,不用外接专用的双口RAM芯片,简化了控制平台的结构,提高了可靠性,充分利用现有硬件的资源,能够实现DSP与FPGA之间的高速数据交换。对DSP而言,FPGA就是一个片外存储器,使用地址线、数据线和R/W信号即可轻松访问。双口RAM模块由两个部分组成,一部分是调用Altera提供的基本宏功能产生的双口RAM部分,另一部分是数据读写部分。数据读写部分采用有限状态机实现,将FPGA需要上传给DSP的数据,如速度检测值、电流检测值等,写入双口RAM部分;从双口RAM部分读取DSP写入的电流环计算结果。

3.2 PWM发生模块设计

采用三角波比较法产生PWM,将DSP下发的2台BLDCM电流环计算结果与模块中增减计数器产生的同一三角波进行比较后产生12路PWM信号。计算结果大于三角波数值时,输出上桥功率管的导通信号;计算结果小于三角波数值时,输出上桥功率管的关闭信号。导通相序相应的下桥功率管恒导通。在导通时间段的中点,产生A/D启动信号。通过改变PWM发生模块的参数,即可方便的调整PWM斩波频率。在关闭时间段的中点同时载入2台电机的电流环计算结果,保证电机PWM信号的同步。PWM发生模块的设计时序如图4所示,图中,M1PWMIN和M2PWMIN分别是DSP下发的2台BLDCM的电流环计算结果,TRI-ANG是增减计数器产生的三角波,ADSRART是A/D启动信号,M1PWMVx和M2PWMVy分别是2台BLDCM的PWM信号。

图4 PWM发生模块时序图Fig.4 The timing diagram of PWM module

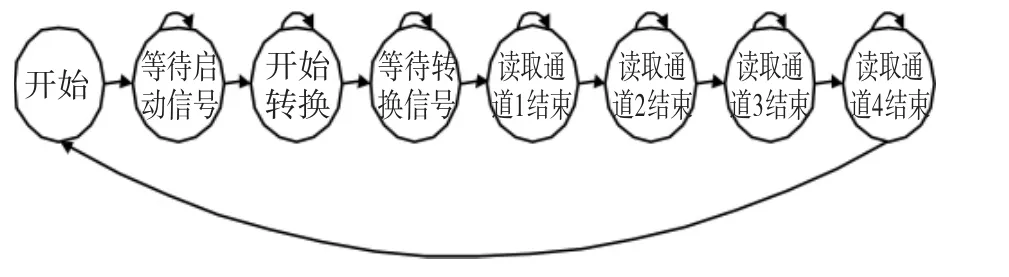

3.3 A/D控制模块设计

使用有限状态机设计了A/D控制器来实现A/D的采样控制。有限状态机的时序根据AD7865的时序编写,如图5所示,分为开始、等待启动信号、开始转换、等待转换结束、读取1通道结果、读取2通道结果、读取3通道结果和读取4通道结果等状态。AD7865的工作频率和PWM的载波频率一致,都是10kHz,并且在导通时间段的中点进行母线电流采样。

图5 A/D模块的状态机Fig.5 The state machine of A/D module

3.4 速度检测模块设计

BLDCM的额定转速是3000 r/min,使用T法测速可以得到较高精度。考虑到开关型霍尔器件只对S磁极作用引起的霍尔信号正负半周期不对称的问题,对霍尔信号的1个完整周期进行计数来检测速度,即在霍尔信号的上升沿开始计数,在下一个上升沿结束计数。将霍尔信号的上升沿进行了处理,保证对霍尔信号的每个周期都能够计数。BLDCM速度的计算公式为式中:n为电机速度,单位是r/min;f为计数时钟频率,单位是Hz;p为BLDCM的极对数;M为计数值。

模块的计数时钟频率是10kHz。最终,BLDCM的速度计算公式为

按照式(3)处理霍尔信号计数值,得到了BLDCM的速度,将其作为速度检测模块的输出。

4 仿真结果

图6 PWM发生模块的时序仿真结果Fig.6 The timing simulation result of PWM module

如前所述,按照FPGA功能模块的设计流程,对各个功能模块进行了功能仿真和时序仿真。在QuartusII 7.0的环境中创建了功能模块的矢量波形文件,使用该文件作为激励,进行了功能仿真和时序仿真。其中,PWM发生模块和速度检测模块的时序仿真结果如图6和图7所示。图6中,M1和M2分别表示BLDCM1和BLDCM2的信号。MxHy是三相霍尔输入信号,MxPWMIN是DSP下发的电流环计算结果,MxPWMVy是6路PWM输出信号,输出信号低电平时功率管导通。从图6(a)可以看出,电流环计算结果可以独立给定,即电机是速度独立运行还是速度协同运行可由DSP确定。由图6(b)可知,A/D启动信号是在导通时间段中点产生的。图7中,CLK是计数时钟,HALL是霍尔输入信号,SPEEDTEMP是计数值,SPEEDOUT是计算得到的电机速度。从图7(a)可以看出,速度检测模块能够对每个霍尔信号进行计数,得到相应的计数值和真实速度。图7(b)中,HA-C、HA-D、HA-A 和 HAB依次对HALL信号进行延时,当后两个信号的组合HA-BUF-A等于2,即霍尔信号出现上升沿时,产生计数启动信号START。霍尔信号的下一个上升沿来临时,前两个信号的组合HA-BUF-B等于2,产生计数停止信号STOP。2个计数时钟周期后,又开始了新的计数。能够完成对霍尔信号的每个周期进行计数的功能。仿真结果表明,各个功能模块的功能和时序能够满足要求。

图7 速度检测模块的时序仿真结果Fig.7 The timing simulation result of speed acquisition module

5 实验结果

速度伺服实验系统使用的BLDCM的参数是:额定电压200 V;额定转速3000 r/min、额定转矩1.6 N·m;极对数 3;转子转动惯量 2.79×10-4kg·m2;相电阻 1.54 Ω;相绕组自感 6.5 mH;相绕组互感0.62 mH。BLDCM的绕组为星型连接,采用两相导通三相六状态的工作方式,使用开关型霍尔元件A3144进行换相和速度检测。

驱动器包括功率电路、隔离电路、电流检测电路、A/D电路等。功率电路选用IRAMS10UP60B集成功率模块。选用高速光耦HCPL2531实现PWM信号的隔离。选用霍尔电流传感器LTS6-NP检测母线电流。A/D选用14位、4通道同时采样、并行输出的AD7865AS-2。

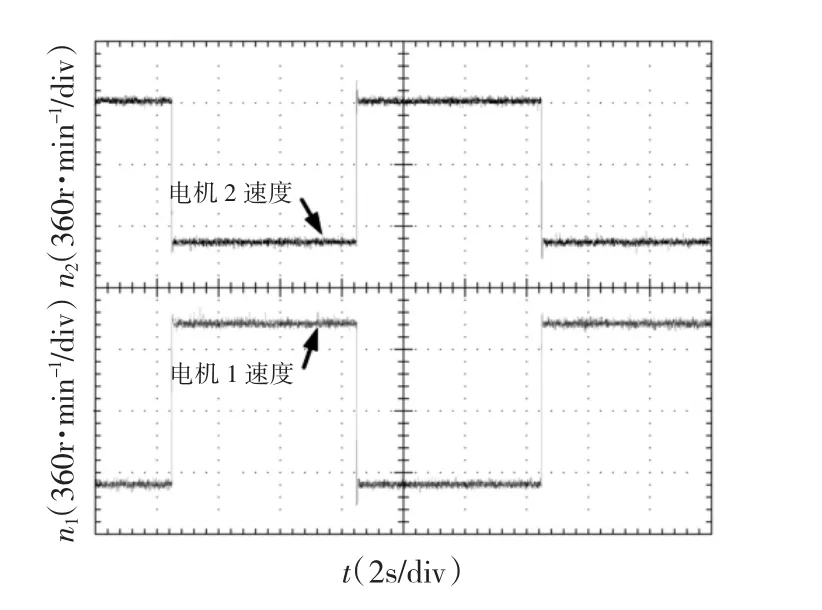

对2台BLDCM进行同步控制的实验结果如图8所示,BLDCM1的速度是2500 r/min,BLDCM 2以2800 r/min的速度跟随运行。同时对2台BLDCM进行独立控制的实验波形如图9所示,BLDCM1的速度在2500 r/min和-2150 r/min之间交替变化;BLDCM2的速度在-2200 r/min和1800 r/min之间交替变化。

图8 BLDCM速度同步控制Fig.8 Synchronizing speed control of BLDCM

图9 BLDCM速度独立控制Fig.9 Individual speed control of BLDCM

5 结语

设计了一种基于DSP和FPGA的电机速度伺服驱动控制平台,采用自顶至下的模块化设计方法实现了DSP和FPFA的功能设计。实验结果表明,该驱动控制平台能够很好的同时完成对2台BLDCM的独立或者协同速度伺服控制。该方案简化了速度伺服系统的结构、降低了成本,并且具有良好的功能扩展性和实现多电机的复杂速度伺服控制的能力。在高精度的速度伺服系统中,也具有很好的应用前景。

[1]TAHAMI F,KAZWMI R,FARHANGHI S.A novel driver assist stability system for all-wheel-drive electric vehicles[J].IEEE Transactions on Vehicular Technology,2003,52(3):683-692.

[2]SHIM H M,HONG J P,CHUNG S B,et al.A powered wheelchair controller based on master-slave control architecture[C]//Proceedings of IEEE International Symposium on Industrial Electronics,June 12 -16,2001,Pusan,South Korea.2001,3:1553-1556.

[3]熊光明,曹晓燕,高峻峣,等.基于速度控制的轮式滑动转向移动机器人航向跟踪[J].北京理工大学学报.2004,24(8):663-666.XIONG Guangming,CAO Xiaoyan,GAO Junyao,et al.Heading following of wheeled skid-steer mobile robots based on speed control[J].Journal of Beijing Institute of Technology.2004,24(8):663-666.

[4]AL-AYASRAH O,ALUKAIDEY T,PISSANIDIS G.DSP based n-motor speed control of brushless DC motors using external fpga design[C]//IEEE International Conference on Industrial Technology,December 15 - 17,2006,Mumbai,India.2006:627-631.

[5]ZHANG Da,LI Hui.A stochastic-based FPGA controller for an induction motor drive with integrated neural network algorithms[J].IEEE Transactions on Industrial Electronics,2008,55(2):551-561.

[6]DUBEY R,AQARWAL P,VASANTHA K M,Programmable logic devices for motion control-a review[J].IEEE Transactions on Industrial Electronics,2007,54(1):559 -566.

[7]AL-AYASRAH O,ALUKAIDEY T,PISSANIDIS G.Mixed signal DSP based multi task motion control system using external FPGA structural design[C]//IEEE Indicon Conference,December 11-13,2005,Chennai,India.2005:419 -422.

[8]XU Dong,WANG Tianmiao,WEI Hongxing,et al.A new dualcore permanent magnet synchronous motor servo system [C]//IEEE Conference on Industrial Electronics and Applicatons,May 25 -27,2009,Xi’an,China.2009:715 -720.

[9]LI Bo,SUN Li,KANG Erliang,et al.High performance and full digital AC position servo system[C]//International Conference on Electrical Machines and Systems,September 27-29,2005,Nanjing,China.2005,3:1869 -1872.

[10]BAI Yucheng,TANG Xiaoqi,CHEN Jihong,et al.Research on ultra-low speed control of PMSM in servo system [C]//World Congress on Intelligent Control and Automation,June 25-27,2008,Chongqing,China.2008:2381 -2386.

[11]王大彧,郭宏.采用DSP和FPGA直驱阀用音圈电机驱动控制系统[J].电机与控制学报,2011,15(4):7-12 WANG Dayu,GUO Hong.A DSP and FPGA based drive control system for voice coil motor used in direct drive valve[J].Electric Machines and Control,2011,15(4):7 -12.