基于现场可编程门阵列的超声电磁复合电机驱动控制系统设计*

2011-06-02羌予践张汝建

羌予践,华 亮, 张汝建,林 纯

(南通大学电气工程学院,江苏南通 226019)

0 引言

以提高电机定位精度及改善电机运行性能为目的的细分驱动技术能使步进电机达到很高的定位精度,但细分数越大,精度越难控制[1]。现实工况下,如焊接过程中的高频起弧和稳弧对驱动电路存在很严重的高频电磁波干扰,采用步进电机细分电路会大大降低系统的可靠性和稳定性,驱动器要满足相当高的技术要求和工艺要求,成本也会较高[1]。超声波电机(Ultrasonic Motor,USM)是一种非电磁电机,由于其具有转速低、转矩大、定位精度高、功率密度大、无电磁干扰等优越特性,所以得到广泛应用。但长时间工作会导致电机材料特性和输出特性变化,产生谐振频率漂移、转速下降。由于依靠摩擦传递力矩,因此USM的寿命一般都不长,如日本Shinsei公司生产,并得到广泛应用的行波USM USR30和USR60寿命分别为2 000 h和1 000 h。

近年来国内、外学者采用电磁伺服电机作为定位系统粗定位驱动元件,采用USM或压电制动器作为定位系统精密定位驱动元件,充分结合了USM与电磁电机各自的优点,取得了较好的效果[2-4]。本文设计了基于现场可编程门阵列(Field Programmable Gata Array,FPGA)的超声电磁混合电机驱动控制系统,充分采用FPGA集成度高、抗干扰能力强、升级维护方便等特点,将USM及步进电机控制信号源均集成于FPGA,有助于超声电磁混合系统的小型化、集成化、高效化设计,有助于系统整体性能的提高。

1 驱动控制系统的整体设计

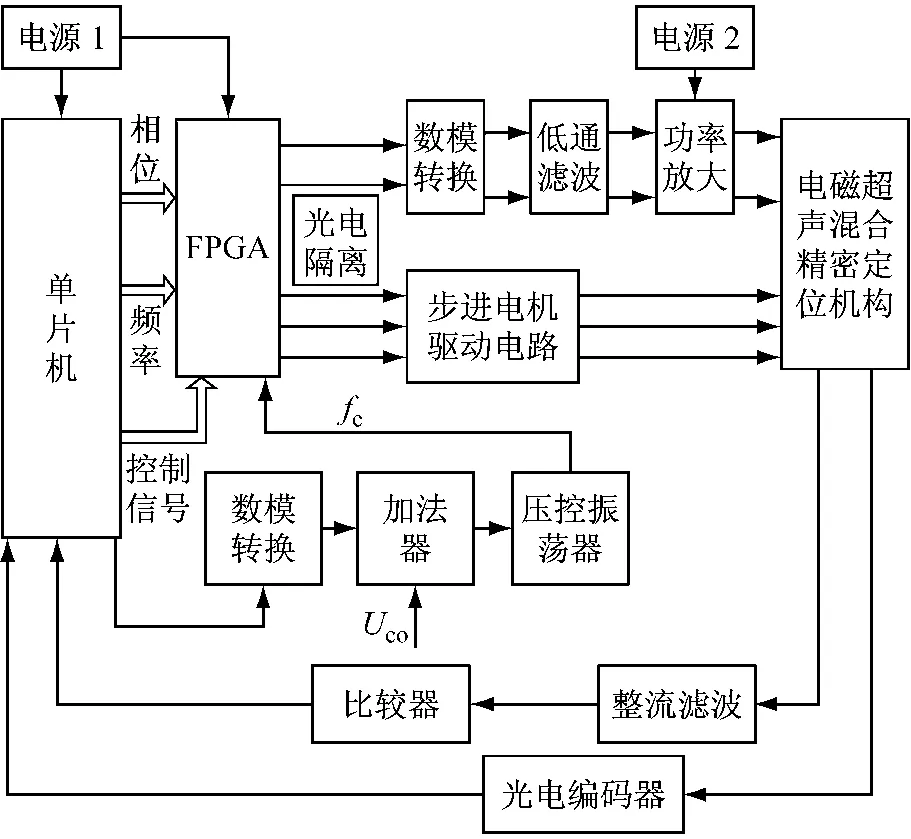

基于单片机和FPGA的混合电机控制系统如图1所示。该驱动控制系统由以单片机为核心的控制单元、以FPGA为核心的执行单元、以电力电子器件为核心的驱动单元三部分组成。单片机把速度、转向、运行步数等控制信息写入FPGA,由FPGA产生电机实际的驱动信号。单片机可专注于信号处理和运算,不必占用过多的CPU资源去直接控制电机,也减小了由此引入干扰的可能性。单片机和FPGA间通过I/O口线进行通信,FPGA的扩展使系统集成度高、维护升级便利。

图1 驱动控制系统总体原理图

2 基于FPGA的行波USM驱动控制系统设计

2.1 设计要求

USM对其外加驱动信号的频率、幅值均有特定的要求。本文采用两相相位差为90°的高频正弦电压信号驱动行波USM,信号频率、相位可调,频率大小由压控振荡器调节。本文分析的驱动控制器具有电机正、反转控制功能,并采用速度闭环控制及频率自动跟踪电路以补偿电机谐振点变化或负载变化造成的参数变化。

2.2 驱动信号源设计

2.2.1 系统总体设计

该移相信号发生器原理框图如图2所示。移相信号发生器[5]由相位字寄存器、相位累加器、波形存储器、相位加法器、数模转换器及低通滤波器组成。其中时钟信号由压控振荡器产生,图2中的N位字长的二进制加法器和N位累加寄存器是驱动源的核心,其作用是对内置为1的频率字进行累加。

图2 数字移相正弦信号发生器原理框图

每来1个时钟脉冲,N位加法器将内置频率控制字数据与累加寄存器输出的累积相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器一方面将加法器在上一次相加后所产生的新相位数据反馈到加法器的输入端,另一方面将其输出的地址分成两路,一路直接从波形存储器中取出波形幅度数据,经D/A转换器和低通滤波器将波形数据转换成参考信号,另一路通过相位加法器加上移相控制字,形成移相信号的地址码,从波形存储器中取出波形数据,最后经D/A转换器和低通滤波器将波形数据转换成移相正弦波信号。当相位累加器累积满量时就会产生1次溢出,完成1个周期性的动作,这个周期就是合成信号的1个周期。

2.2.2 系统的FPGA设计

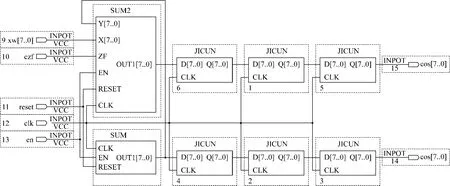

基于FPGA的信号源产生电路如图3所示。

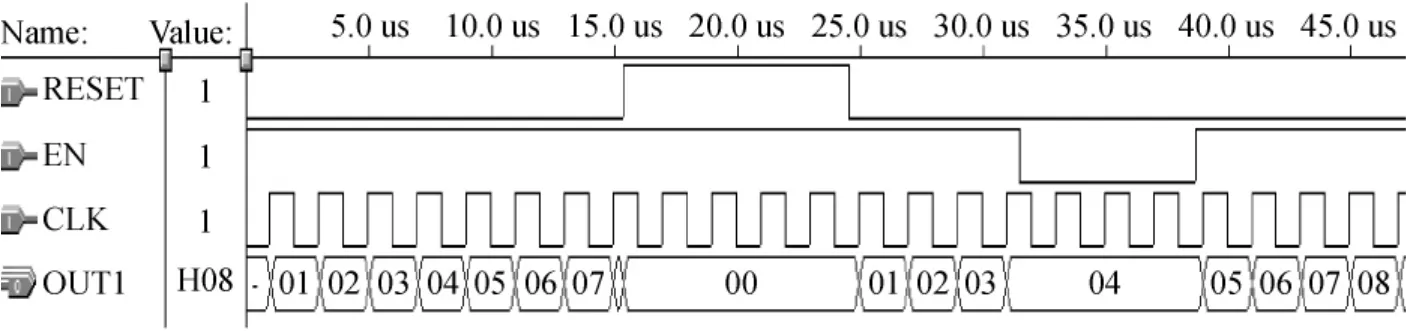

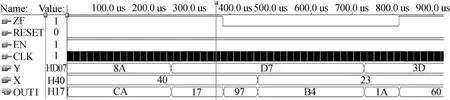

(1)相位累加器。图3中SUM模块为相位累加器,相位累加器的累加值内置为1,当时钟上升沿到来时累加一次,累加至255时,当下一时钟上升沿到来时,相位累加器就会溢出完成一个周 期的累加。SUM模块时序仿真图如图4所示。

图3 基于FPGA的信号源产生电路

图4 SUM模块时序仿真图

(2)相位加法器。图3中的SUM2模块为相位加法器,相位加法器完成将数据地址转换为信号间的相位差值。当时钟上升沿到来时,如果ZF=1,相位加法器将相位累加器的地址值加上移相控制字,如果ZF=0,相位加法器将相位累加器的地址值减去移相控制字,产生一超前或滞后的偏移地址值,从而控制电机的正反转。相位加法器时序仿真图如图5所示。

(3)波形存储器及整体电路仿真。使用LPM模块中只读存储器lpm_rom,把正弦波形离散数据储存在ROM中,使用累加地址访问存储器。由于后续D/A转换精度为8位,因此lpm_rom中输出数据位数LPM_WIDTH置为8位。此外,地址线宽度置为8位,地址输入由时钟上升沿触发,输出为寄存器方式。

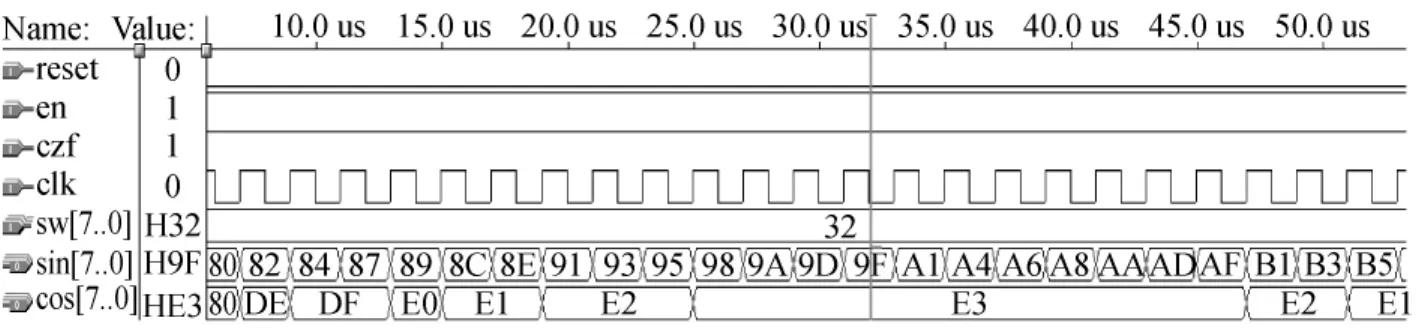

对整体电路进行编译仿真,结果如图6、图7所示。

2.2.3 信号源的实现

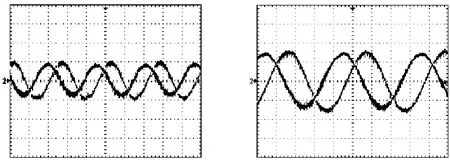

FPGA输出数字量信号依次经8位D/A转换器及滤波器(由二阶滤波器与一阶滤波器级联构成)后,得到的超声波电路驱动波形如图8所示。

图5 相位加法器时序仿真图

图6 系统正转仿真波形图

图7 系统反转仿真波形

图8 行波USM驱动电路波形

2.2.4 功放电路及频率闭环控制电路

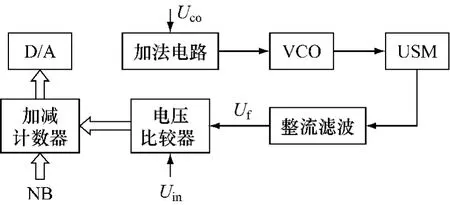

设计中采用基于甲乙类单电源互补对称放大电路技术的功率放大电路作为驱动电路。设计的频率跟踪电路中,Uin为设定电压,它与反馈直流电压Uf在电压比较器中进行比较,输出信号输入单片机,控制单片机内计数器加或者减计数,计数器用软件方式实现。计数值输出到D/AC0832改变输出直流电压的值,它与加法电路的预置电压Uco一起作为VCO输入电压,控制VCO输出实现频率自动跟踪。

图9 频率跟踪器设计框图

3 基于FPGA的三相磁阻式步进电机驱动控制系统设计

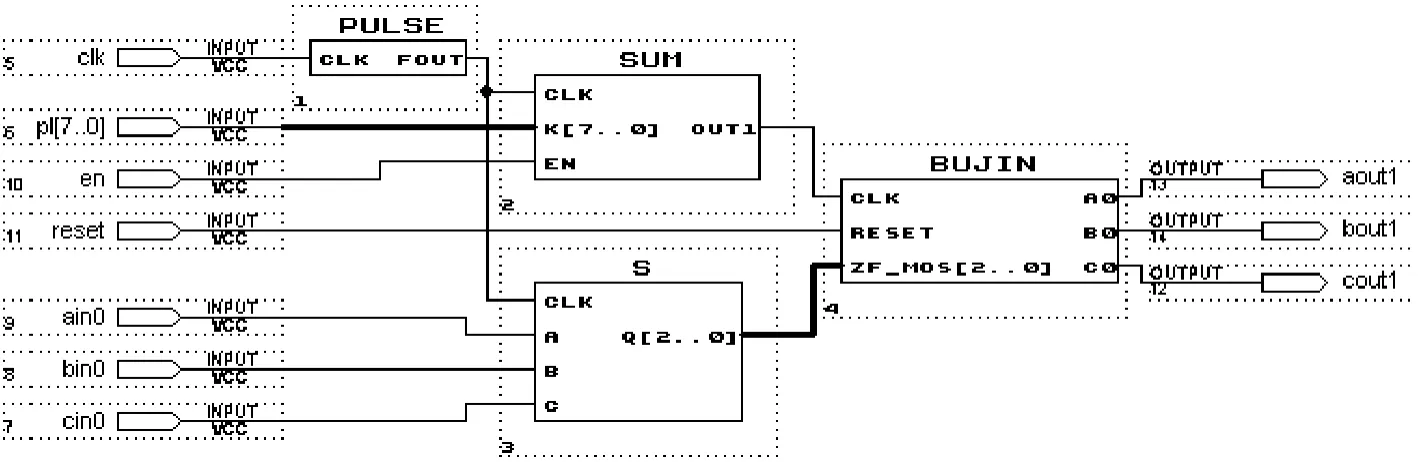

步进电机是在脉冲分配器的控制下进行各种运动动作的。脉冲分配器的输出频率控制步进电机的速度,而脉冲的分配顺序控制步进电机的正反转。脉冲分配器的控制电路逻辑图如图10所示。

整个电路由分频器和相序分配器构成。时钟信号CLK(12 MHz)经过分频器分频后作为相序分配器的时钟信号,a为转向控制端,a为1时正转,a为0时反转。b,c为工作方式选择端,输出不同的相序波形,控制步进电机的动作。A,B,C为三相脉冲输出端。分频器和相序控制器由硬件描述语言VHDL来编写。

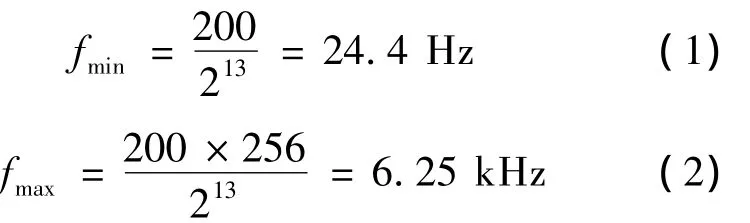

图11中,PULSE分频器模块将系统时钟12 MHz进行60分频,得到200 kHz的方波信号输给调频器SUM。调频器SUM单元由N位累加器为核心组成,累加器将频率控制字K进行累加,把相加后的结果的最高位输出。当相位加法器满时会产生一次溢出,这样就完成了一个周期。调频器 SUM的基准时钟为 200 kHz,累加器13位,K为8位,频率输出范围为

图11 基于FPGA的环形脉冲分配器设计

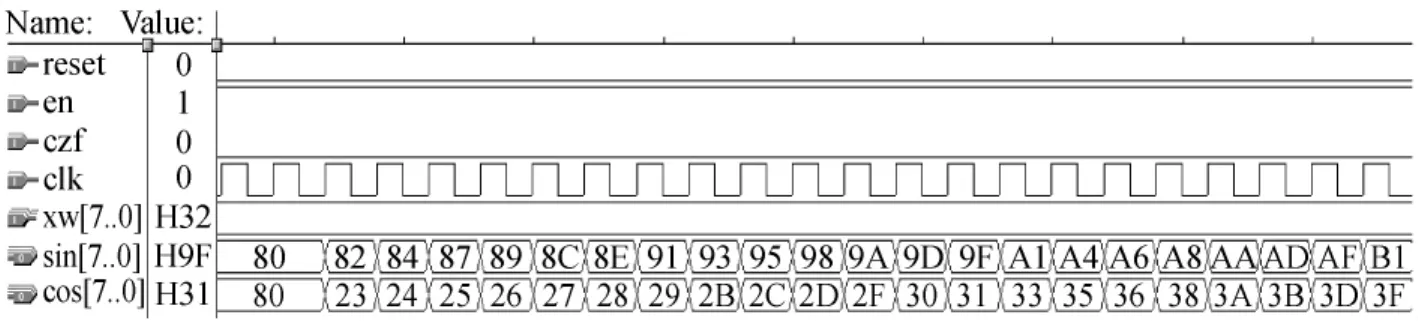

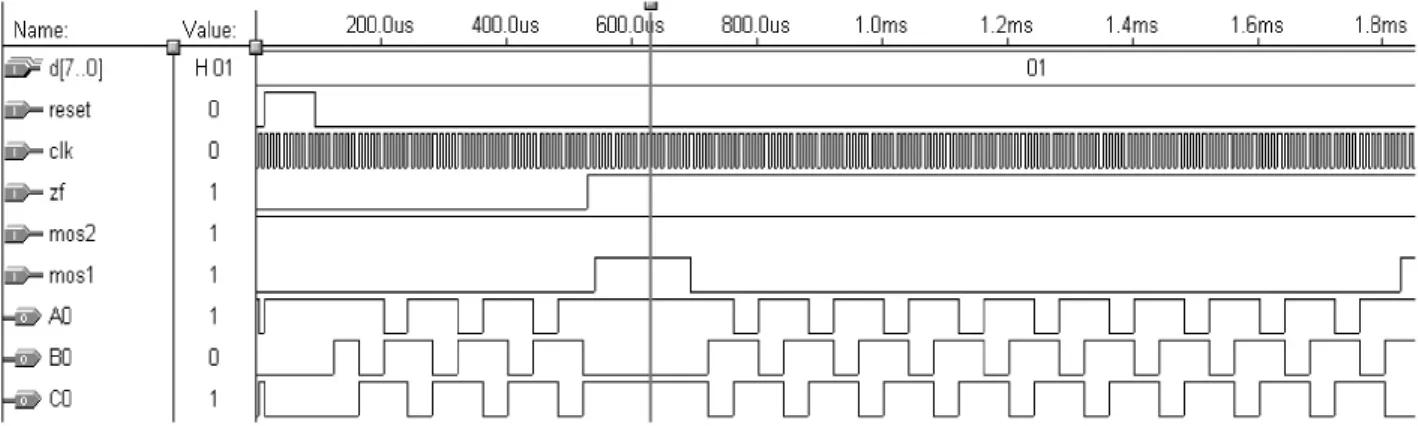

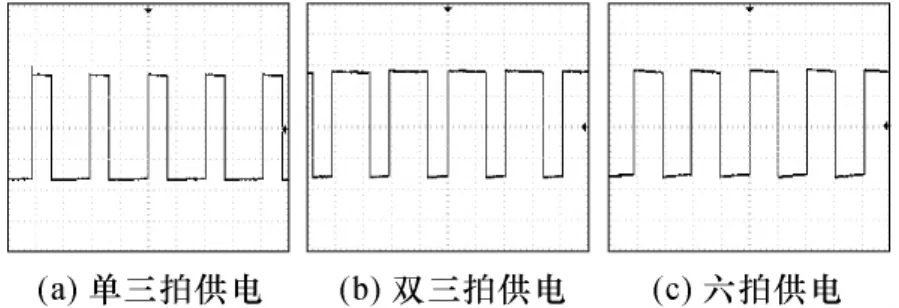

脉冲分配器用有限状态机来实现[7]。步进电机运行方式由控制信号zf,mos1,mos2来选择,信号zf控制电机的正反转,mos1,mos2选择电机的运行模式。整体电路仿真结果如图12所示,示波器采集的波形如图13所示。

图12 整体电路仿真波形

图13 示波器采集波形

4 结语

USM一般有效工作时间少于2 000 h,使USM在连续运行的高精度控制系统中使用受到限制。因此,为真正使USM成为广泛使用的高精度控制电机,须提高电机的有效工作时间。以超声电磁混合电机为背景,设计了基于FPGA的一体化驱动控制系统,并进行了试验研究。该系统采用FPGA作为超声波电机与步进电机的信号发生源,并配合单片机实现了电磁超声混合电机的驱动控制,为超声电磁混合电机系统的小型化、集成化设计提供了基础。

[1]华亮,吴晓,冯浩.新型混合直接驱动的机器人关节精密定位系统[J].机电工程,2008,25(3):10-12.

[2]林海波,黄小良,杨国哲.三维微细电火花加工伺服控制系统设计及实验研究[J].机械设计与制造,2010,20(5):48-49.

[3]林长春.光学零件超精密磨削进给控制系统的研制[D].长春:长春光学精密机械学院,2000.

[4]孙德旭.多功能微细加工数控平台研究[D].青岛:中国石油大学,2007.

[5]王龙帅.基于DDS的超声波电机驱动控制研究[D].洛阳:河南科技大学,2009.

[6]施纪红.基于VHDL语言设计的步进电机控制器[J].苏州市职业大学学报,2008,19(4):19-21.