直扩系统中PN码跟踪技术的研究

2011-05-08施小茜

齐 华 李 岩 施小茜

( 西安工业大学电子信息工程学院,陕西 西安 710032)

引言。在扩频系统中,为了正确的进行扩频信号的解扩,接收机中产生的本地扩频码序列必须与接收信号中的扩频码序列同步,由于直扩系统中接收信号的信干噪比很低,在实现扩频码的同步之前,难以实现载波同步,因此在接收机中一般首先实现扩频码的同步。实现扩频码的同步后,扩频通信系统中的载波同步、位同步和帧同步等就可以使用与一般通信系统基本相同的方法实现。同步的过程一般分两个阶段:捕获和跟踪。典型的伪码跟踪方法是DLL延迟锁相环。

1.延迟锁相环的跟踪机理

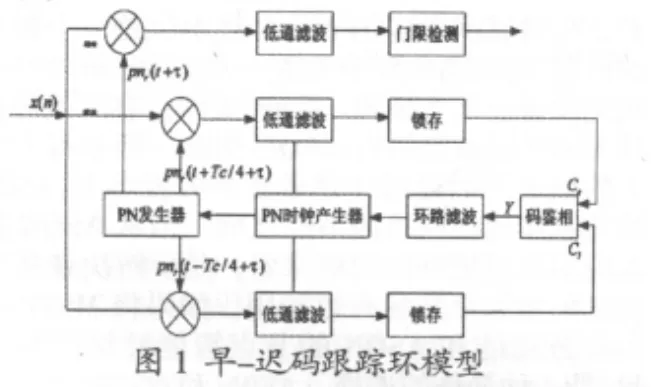

延迟锁相环又叫早-迟码跟踪环,早迟门跟踪环路通常由超前一滞后相关器、码鉴相器、环路滤波器和码NCO等部分组成。其模型如图1所示。

延迟锁相技术在概念上与相位锁相技术相像,它也是通过一非线性的反馈环路来实现输出信号对输入信号的跟踪与同步作用。跟踪原理:本地PN码与发端PN码经捕获后会有一个时差τ,τ小于PN码的码片宽度,图中两路相关器相关特性相同,不同的是其相对位置差一个Δ(即一个码片宽度),这是因为所加的本地参考码的延迟所致。由于环路反馈作用,两个相关输出的误差信息经环路滤波后,控制VCO的输出,来调整本地PN码发生器的相位,从而减少相差。

2.1 PN码跟踪鉴相电路

在延迟锁相环路中,先将下变频后产生的基带信号分别跟本地超前、滞后PN码进行相关,再经包络检波器后,分别求出超前支路的相关值和滞后支路的相关值,然后将它们同时送入到延迟锁相环的减法鉴相器,可得整个相关网络的相关函数波形或误差函数波形,该误差信号经过滤波器后控制本地PN码的码钟。

本文中,对环路滤波的过程做了简化,将得到的超前和滞后支路的相关值之差与门限值进行比较,根据比较的结果来调整伪码的NCO的工作,伪码调整步进为Tchip/8,即一个系统时钟周期。在一个跟踪周期内,如果超前支路相关值减去滞后支路相关值之差大于门限值,则表示本地伪码超前,此时超前指示输出为1,滞后指示输出为0,将本地伪码向后调整Tchip/8的相位;如果滞后支路相关值减去超前支路相关值之差大于门限值,则表示本地伪码滞后,此时超前指示输出为0,滞后指示输出为1,将本地伪码向前调整Tchip/8相位;否则,就认为伪码已经同步,此时超前指示输出为0,滞后指示输出为0,伪码相位不作调整。伪码跟踪的过程中可能会失步,因此需要检测本地伪码相关器输出的值,当连续N个周期相关器输出的值都小于设定的跟踪门限时,则判断伪码失步,重新进入捕获状态。

2.2 PN码时钟控制电路

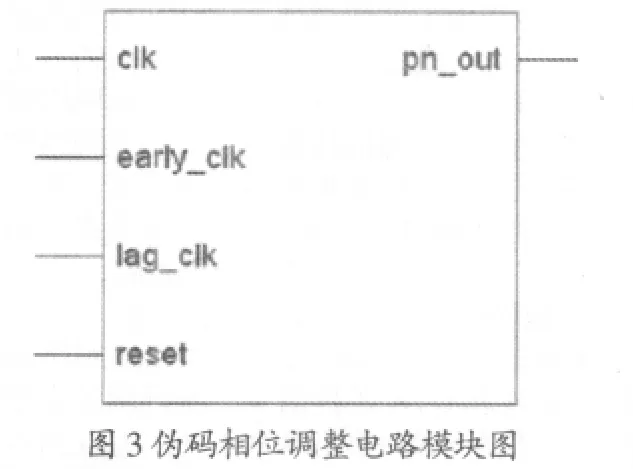

在伪码的捕获和跟踪过程中,为了使伪码相位同步且精确跟踪,需要对本地伪码的相位进行不断调整,即对本地伪码产生器的时钟相位做调整。伪码相位控制电路模块图如图3

图3中,reset为系统复位端,高电平有效;clk为时钟输入端,时钟频率是伪码频率的8倍。当clk的上升沿来到时,若没有调整信息,则内部的计数器的值正常增加1;Early_clk为超前指示,高电平有效,当Early_clk有效时,计数器的值在时钟上升沿时停止计数,这样就将本地伪码的相位往后调整了1/8个码元;Lag_clk为滞后超前指示,高电平有效,当Lag_clk有效时,计数器的值在时钟上升沿时加2,这样就将本地伪码的相位往前调整了1/8个码。

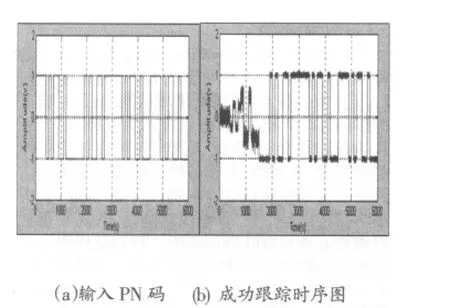

3 仿真结果图4 是在matlab 里对延迟锁相环跟踪电路进行仿真。假设此时捕获已经成功,信道中加入T/8的相位偏差,调制信息码率仍然为10kbps,PN码速率5.12Mbps。系统时钟40.96MHz。所得波形是相位偏差在T/8时的各个关键模块的输出。对早门和迟门的相位差从-7T/8到7T/8的范围内进行了实验,结果表明跟踪效果良好。

图4 延迟锁相环PN码跟踪仿真波形图

结束语

本文通过对延迟锁相环技术的研究,设计并实现了扩频码跟踪电路,并在matlab里对设计的电路进行了仿真,在对早门和迟门的相位差从-7T/8到7T/8的范围内进行的实验结果都表明了其跟踪效果的良好性。

[1]卢屹,张新军,张嘉俊,罗汉文,宋文涛.数字锁相环的参数设计及其应用[J].t通信技术,2001,9:12-14.

[2]张厥盛,郑继禹,万心平.锁相技术[M].西安电子科技大学出版社,1996.

[3]SpilerJJ,D T Magill.TheDelay-Lock Di∽riminator-Anopti—mumTrackingDeviceProc.IRE1961.490):1403~1416.

[4]沈允春.扩频技术Inl.北京:国防T业}n版社,1995,7.

[5]查光明,熊贤祚.扩频通信.西安.西安电子科技大学出版社.