非等量采样伪码跟踪环建模分析

2014-03-25赵林军

梁 芳, 赵林军

(1.陕西理工学院 物理与电信工程学院, 陕西 汉中 723000;2.陕西理工学院 电气工程学院, 陕西 汉中 723000)

0 引 言

直序列扩频系统中常使用延迟抖动环(Delay-Locked Loop,DLL)实现收发伪码相位同步[1]。根据伪码长度与采样频率的关系,DLL又分为等量采样环路(Commensurate Sampling Loop,CSL)与非等量采样环路(Non-Commensurate Sampling Loop,NCSL)[2]。由于NCSL可在较低采样条件下,实现较高的时间分别率而得到广泛应用。

2002年,QUIRK等[2]提出了NCS技术伪码跟踪环,并指出当伪码每chip的时宽Tc与采样间隔Ts满足kTs=nTc时,跟踪环路可获得Tc/k的跟踪精度,而没有对采样频率与伪码环路相关函数的影响进行分析。2006年,QUIRK等[3]对NCSL的累加时间进行了分析,提出环路的累积时长应是未采样伪码周期与其一个整周期内非等量采样样点数的最小公倍数。这对实时性要求较高的系统而言,工程上难以实现。2010年,柯颋等[4]论述了多普勒频移可显著改善等量采样伪码跟踪环的时间分辨力,同时指出伪码跟踪环路的时间鉴别力与采样频率之间不存在简洁的逻辑关系。因此,在伪码跟踪环路的数字化实现时,往往需要花费大量时间对其相关参数进行调试。2014年,JIN等[5]提出当η=Ts/Tc=I.d1d2…dv,累积相关时长L=10v(L是整数倍的伪码周期长),且η·10v与10v互素时,DLL中的收发伪码互相关函数具有理想包络。

综上所述,当DLL环路中的伪码码片速率给定,由于系统中多种因素的影响,实际的NCSL采样频率不能满足文献[4]的约束条件,因此,按其难以评估采样NCS技术的伪码跟踪环路的性能,且文献[2-5]中给出的相关约束条件本身就难以实现。故研究NCSL伪码跟踪环的MATLAB建模与分析,对设计者快速评判NCSL环路具有实际工程意义。

1 伪码DLL跟踪环路的结构及其参数设计

由文献[3,6]知,目前在直扩通信系统中常使用DLL跟踪环实现发信号伪码与本地再生伪码相位的同步,该环路的结构如图1所示。其中r(t)为接收到基带直扩信号,r(k)为采样量化器(ADC)的输出。为了实现伪码相位的精确同步,三路相关累积分别完成r(k)与本地再生伪码的超前相位PN(k+1)、当前相位PN(k)和滞后相位PN(k-1)在一个或数个伪码周期内的相乘累加运算[7],再按照相应的鉴相算法由上述三路相关累积输出量给出本地伪码相位与接收信号中的伪码相位的误差e(k),最后由e(k)控制本地再生伪码发生器更新一组新的伪码相位输出PN(i),(i=k+1,k,k-1)。其中,环路滤波器F(z)可使得本地伪码相位平稳转移。NCO为本地伪码发生器提供工作时钟,在文中所述的仿真分析中,NCO由一个门限ε代替。当y(k)≥ε,本地伪码再生器相位向左移动更新;当y(k)≤-ε时,本地伪码再生器相位向右移动更新;当y(k)∈(-ε,ε)时,本地伪码再生器相位不更新。

图1 基带伪码跟踪环原理

现就伪码DLL跟踪环中的相关算法简述如下:设跟踪环路的离散信号为

(1)

式中S为信号功率,d为符号,每符号1个完整的Gold码长,k为采样序号,kτ为信号传输时延τ经离散后的值。DLL环路中的超前相关、当前相关与滞后相关分别为

(2)

式中累积时长L=nfsTb,其中n为正整数,Tb为符号d的宽度,即累积可在一个符号内或多个符号内进行。根据文献[8],环路鉴相算法采用归一化点积功率型算法[9],于是,鉴相器的输出误差e(k)为

(3)

环路中数字滤波F(z)采用理想二阶数字滤波器,其传递函数为

(4)

滤波器F(z)系数C1与C2分别为

C1=4π·ξ·Bn·Tb,

C2=(2π·Bn·Tb)2,

(5)

式中ξ=0.707为阻尼系数,Bn为环路噪声带宽。环路滤波器的误差输出量为:

y(k)=(C1+C2)e(k)-C1e(k-1)+y(k-1)。

(6)

2 伪码DLL环的非等量采样

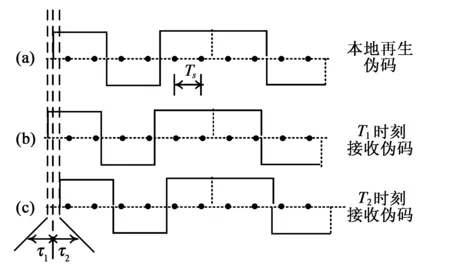

按照文献[4]所述,图1伪码跟踪环的实现有等量采样与非等量采样两种技术。其中,采用等量采样技术时,易引起时间分辨模糊现象,如图2所示。其中的连续方波为实际信号的波形,时间轴上的“点”代表采样位置,设伪码每chip采2个样点(Ts=1/fs)。由于采样脉冲起始位置的不确定性,使得T1时刻DLL环路中本地再生伪码采样(如图2(a)所示)与接收信号中的伪码采样(如图2(b)所示)和T2时刻DLL环路中本地再生伪码采样与接收信号中伪码采样(如图2(c)所示)相关时,结果将是完全一样。而实际对应的连续信号的相关显然是存在差异。于是,等量采样的伪码跟踪环就产生了时间跟踪的模糊问题。

图2 等量采样时间分辨模糊示意图

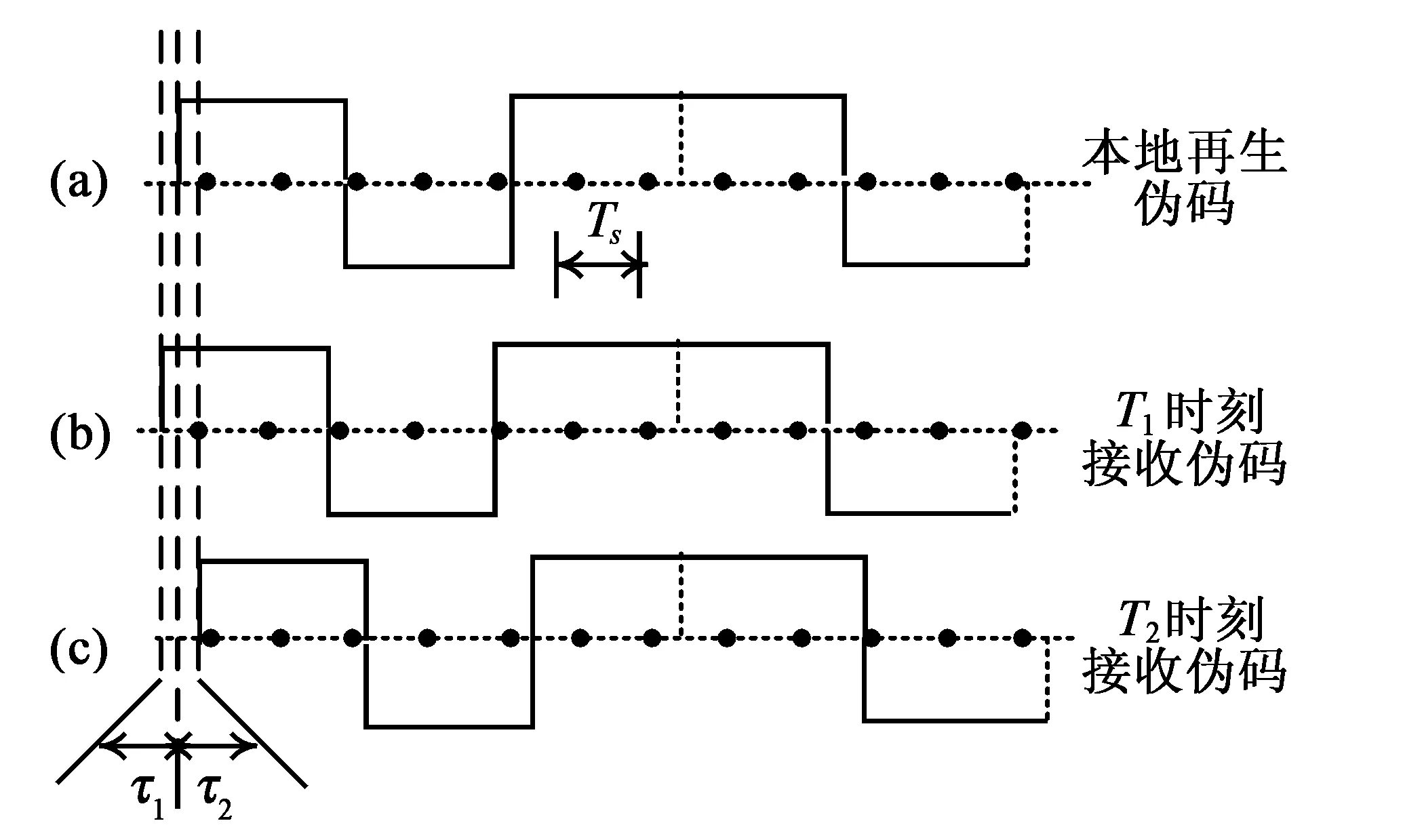

为此,QUIRK等[2-3]提出了非等量采样技术,如图3所示。图中每码片样点数目不同,T1时刻伪码跟踪环路中收发伪码互相关峰显然是不同于T2时刻伪码跟踪环路中的伪码互相关峰的,因此,二者是可分辨的。故采用NCS技术后,DLL环路可以区分图2所示的时延τ1与时延τ2。

图3 非等量采样技术示意图

3 仿真流程与代码实现

基于MATLAB实现NCSL伪码DLL环路的建模流程如图4所示。其中,fso是基带采样频率的中心频率,Δ为采样频率变化区间最大距离,仿真采样速率变化范围为[fso-Δ/2,fso+Δ/2](单位为MHz)。v为采样频率变化步长。伪码DLL跟踪环路假设已实现±1/2 chip捕获。为此程序设计每次相关后,本地伪码的相位移动1 Sample。为了降低仿真实现难度,图1中的信号样点量化采用浮点数,不考虑量化误差与运算误差。

图4 伪码DLL跟踪 环建模流程图

从第二小节知,等量采样伪码DLL环路与非等量采样伪码DLL环路的最大区别是伪码每码片的采样数不同。且由图3可知,在采样频率给定的条件下,实际系统中信号的首样点落在[0,Ts]区间具有不确定性。因此,基于MATLAB实现非等量采样伪码DLL环路的关键是实现对r(t)与本地再生伪码PN(·)的非等量采样。为了伪码便于实现,r(t)中的每个符号(待传数据)采用一个完整的伪码周期进行调制。故对r(t)与本地再生伪码PN(·)的采样具有相似性。

下文着重介绍伪码的非等量采样的实现。为论述方便,首先给出伪码的非等量采样函数的MATLAB代码,具体如下:

function [out]=NCS(fs,fc,n,seq); %n为1采样间隔等分数

Ts=1/fs; %采样间隔

Tc=1/fc; %伪码每码片时宽

len=length(seq); %伪码长

Sample_Delay=n-1; %设置首样随机时延

Start=randint(1,1,[1,Sample_Delay]);

kk=Start/(n*fs); %计算首样时延时间

i=1;

j=0;

while j while kk temp=mod(j,1023)+1; out(i)=seq(temp); i=i+1; kk=kk+Ts; end kk=kk-Tc; j=j+1; end end 在NCS子函数中,seq是由为1 023 chip的Gold序列;Sample_Delay用于设置伪码离散化首样点时延范围,该时延范围的最大值为n,再由MATLAB系统自带函数randint()在[0,Sample_Delay]范围内产生随机时延,以模拟实际系统中的采样脉冲的不确定性。这是因为计算机内的数据均是离散的,而时间系统中,在[0,Ts]内有无穷个时间点,为了简化模拟,代码中预设了一个变量n为[0,Ts]内的预设等分数。如此以来,结合双while嵌套语句,最终完成伪码或信号r(t)的非等量采样。 以下是NCSL的仿真分析。 实验1 Gold码非等量采样方法实现。为便于观察,实验参数设为:fc=1 023,fs=2 240,delay=9,代码运行后,Start=7。在上述参数下,对应离散后的结果,可视为[0,Ts]内又分了10等分非等量采样,从第7个点开始,以Ts为间隔分布。表1列出了NCS函数运行结果,其中所用符号与第3节NCS()函数中变量相对应。 表1 伪码NCS采样结果表 结果分析:由表1可知,在实验1参数条件下,文中所述的非等量采样代码运行后,在Gold码的第4个码片与第9个码片内采得3个样点,而在第1、2、3、5、6、7、8、10码片内各采得2个样点,可见文中所述的分等量采样实现方法是正确的。 实验2采样频率对非等量采样DLL环路伪码相关函数的影响分析。选择采样频率,应使得环路中的收发伪码互相关函数R(τ)具有良好的对称性,这是影响环路时延分辨力的关键。由于文献[2-5]给出的约束关系在实际系统中难以长期满足,故需要通过大量实验对伪码跟踪环所使用的采样频率、相关累积时间进行评估。仿真参数设置为:BPSK伪码采用1 023平衡Gold码调制的基带信号,符号噪声比均为-10 dB。其中,伪码速率为1.023 Mchip/s,采样速率为(4.092+Δ) MHz/s,(Δ∈[-0.005,0.005]),频率变化步长为1 kHz。伪码DLL环中的累积时间L为一个完整的伪码周期(具体点数由程序根据伪码周期与所使用的采样频率自动计算获得)。图5画出了DLL中伪码互相关函数的5条曲线,为了便于观察,它们分别取其各自互相关函数峰值左右各3个点所绘制。由图5可以看出:(1)fs∈[4.089,4.091 9] MHz时,R(τ)在峰值左右均具有良好的对称性;(2)fs≤4.087 MHz时,R(τ)的右斜边下降较快;(3)fs>4.092 MHz时,R(τ)的左斜边下降较快。 结果分析:若假设实际的非等量采样伪码DLL环路使用的采样频率的中心为4.090 MHz,信号r(t)中的多普勒频移或采样时钟在(4.090±0.001) MHz内变化时,环路中的伪码相关函数仍具有良好的对称性,即环路的时间分辨力仍保持良好。这一结论在更高采样频率时,具有类似情况出现。同时,采样频率对伪码DLL中的伪码互相关函数的峰值有一定影响,但其影响在该频率窗内大约为0.32 dB以内。考虑到这一因素,故非等量采样伪码跟踪环所使用的采样频率小于4倍过采样时,其捕获门限的选择应以4倍等量采样门限为准(由图5看出,fs=4fc=4.092 MHz时,其伪码互相关峰应小于fs=4.091 9 MHz的伪码互相关峰)。 同时,由图5又可以得出:若在4倍伪码速率附近实现非等量采样伪码跟踪环路时,应该选择稍小于4倍的伪码速率作为系统的采样频率,而不能选取稍高于4倍的伪码速率为系统的采样时钟,这是由于采用前者可获得伪码捕获门限的下界。而选择后者,显然难以确定这一门限值。 实验3 非等量采样伪码DLL环路滤波器响应分析。仿真参数设置同实验2,环路噪声带宽Bn=2 Hz。图6画出了不同采样频率下,非等量采样伪码DLL环路滤波器输出曲线。 图5 NCSL环路自相关函数曲线 图6 伪码跟踪环环路滤波器输出曲线 结果分析:(1)按照实验2条件,若伪码跟踪环路采用的采样频率fs<4fc时,环路可迅速收敛;当采样频率fs>4fc时,环路收敛速度较慢;(2)按照实验2与实验3的结论(1)选取恰当的采样频率后,与fs=4fc的等量采样伪码跟踪环路的收敛性相比较,二者无明显差别。 在直接序列扩频系统中,由于信号中存在多普勒频移以及本地时钟的抖动等因素的制约,实际的伪码跟踪环路的参数设置难以满足相关文献报道的约束条件,为此,笔者采用MATLAB对非等量采样伪码DLL环进行了建模仿真分析。仿真结果表明:伪码速率给定时,在近4倍(小于4倍)的过采样伪码跟踪环中,存在一个大约2 kHz采样频率窗口,使得系统中所使用的采样频率落在该窗口内时,伪码DLL环路仍具有良好的时间分辨力。同时也发现,在相同条件下,当采样频率小于该频率窗的下限时,伪码DLL环中的伪码互相关函数右斜边下降快于其左斜边;当采样频率大于该频率窗的上限时,伪码DLL环中的伪码互相关函数左斜边下降快于其右斜边。同时,当fs4fc(“”表示稍小)时,NCSL与CSL无明显差别。文中所述的结论显然对非等量采样环路的硬件实现具有工程意义。 文中主要以4倍伪码速率采样时钟论述,但是其结论对更高的采样频率有类似结论。读者在具体设计实现中,可依据相关参数,按照文中方法,进行环路参数分析,以确保伪码跟踪环路能良好工作。 [参考文献] [1] MILEANT A,MILLION S,HINEDI S,et al. The performance of the all-digital data transition tracking loop using nonlinear analysis[J]. Communications,IEEE Transactions on,1995,43(234):1202-1215. [2] QUIRK K J,SRINIVASAN M. Analysis of sampling and quantization effects on the performance of PN code tracking loops[C]//Communications,ICC 2002. IEEE International,2002:1480-1484. [3] QUIRK K J,SRINIVASAN M. PN code tracking using noncommensurate sampling[J]. Communications, IEEE Transactions on,2006,54(7):1349-1349. [4] 柯颋,胡修林,刘禹圻,等.GNSS接收机中采样率对时间鉴别力的影响[J].宇航学报,2010,31(12):2722-2729. [5] JIN Xiao-jun,XU Zhao-bin,ZHANG Chao-jie,et al. Simple approach to determining parameters of noncommensurate sampling for optimal pseudo-noise code phase delay discrimination[J]. Electronics Letters,2014,50(4):283-284. [6] 张大卫,胡修林,李晨.卫星定位接收机高精度伪码跟踪的设计与实现[J].电子技术应用,2009,35(9):108-111. [7] SUWON K,YONG-HWAN L. Rapid acquisition of PN signals for DS/SS systems using a phase estimator[J]. Selected Areas in Communications,IEEE Journal on,2001,19(6):1128-1137. [8] 赵林军.等量采样伪码跟踪环的MATLAB实现[J].陕西理工学院学报:自然科学版,2012,28(6):15-18. [9] 黄波,胡修林.一种高精度系统时间同步方法[J].信息与控制,2011,40(3):347-351.4 仿真结果与分析

5 结束语